一种高档FPGA可重构配置方法

软件无线电资料整理收集

FPGA及动态可重构技术在软件无线电中的应用摘要:介绍了将现场可编程门阵列(FPGA)专用硬件处理器集成到软件通信体系结构">软件通信体系结构(SCA)中的机制,实现了动态部分可重构技术在软件无线电(SDR)硬件平台中的应用,有效地缩短系统开发周期,提高了硬件资源的利用率。

SDR是使用一个简单的终端设备通过软件重配置来支持不同种类的无线系统和服务(包括2G、3G移动通信系统和WLAN)的新技术。

它具有较强的开放性和灵活性,硬件采用标准化、模块化结构,可以随着器件和技术的发展而更新和扩展;软件模块可以进行加载和更改,根据需要不断升级。

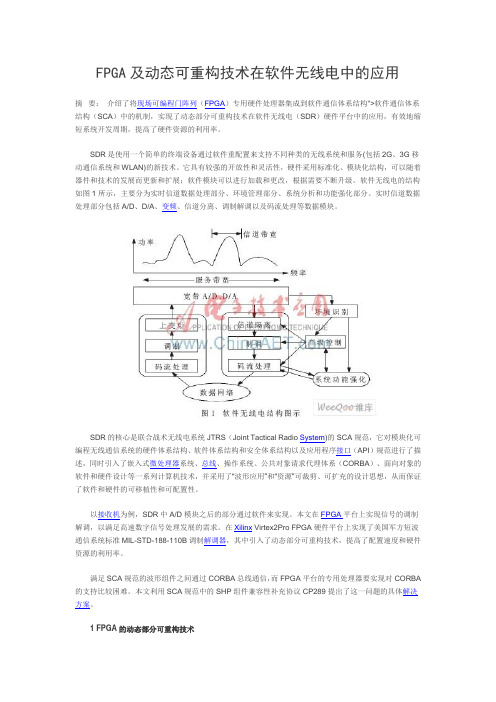

软件无线电的结构如图1所示,主要分为实时信道数据处理部分、环境管理部分、系统分析和功能强化部分。

实时信道数据处理部分包括A/D、D/A、变频、信道分离、调制解调以及码流处理等数据模块。

SDR的核心是联合战术无线电系统JTRS(Joint Tactical Radio System)的SCA规范,它对模块化可编程无线通信系统的硬件体系结构、软件体系结构和安全体系结构以及应用程序接口(API)规范进行了描述,同时引入了嵌入式微处理器系统、总线、操作系统、公共对象请求代理体系(CORBA)、面向对象的软件和硬件设计等一系列计算机技术,并采用了“波形应用”和“资源”可裁剪、可扩充的设计思想,从而保证了软件和硬件的可移植性和可配置性。

以接收机为例,SDR中A/D模块之后的部分通过软件来实现。

本文在FPGA平台上实现信号的调制解调,以满足高速数字信号处理发展的需求。

在Xilinx Virtex2Pro FPGA硬件平台上实现了美国军方短波通信系统标准MIL-STD-188-110B调制解调器,其中引入了动态部分可重构技术,提高了配置速度和硬件资源的利用率。

满足SCA规范的波形组件之间通过CORBA总线通信,而FPGA平台的专用处理器要实现对CORBA 的支持比较困难。

一种基于FPGA的在线升级方案

FPGA摘要现代电子设备的软件系统经常需要更新,以修复错误、增加新功能和提高性能等。

传统的升级方法是通过存储介质或在线下载方式进行传输,可能存在复杂的手动操作和数据完整性的问题。

本文提出一种基于FPGA 的在线升级方案,该方案使用基于网络连接的通信协议和FPGA 的可编程性实现在线升级,提高了安全性和可靠性,并且可以在不断变化的需求下灵活地进行更新。

关键词:FPGA,在线升级,可重构引言在现代电子设备中,获得最新软件功能和性能更新对于产品的长期稳定性和市场竞争力至关重要。

实时更新软件不仅可以提高产品生命周期的利润和收益,还可以减少应用程序中的问题和漏洞。

传统的升级方法是通过存储介质(例如USB 驱动器、CD、SD 卡或U 盘)或通过在线下载方式进行传输。

但是,这种方法可能需要复杂的手动操作,并且存在数据完整性的问题,因此可能导致数据丢失、设备损坏和安全性问题等。

随着技术的发展和电子设备的复杂性的增加,可重构硬件的使用变得越来越广泛。

现代FPGA (现场可编程门阵列)被广泛应用于数字信号处理、加密算法、图像处理和机器学习等领域,在实时更新和软件升级中也充当越来越重要的角色。

使用FPGA 作为处理单元,可以实现硬件的实时升级和灵活的重构,保护设备和数据的安全性和完整性。

在线升级方案基于FPGA本文提出一种基于FPGA 的在线升级方案,该方案使用基于网络连接的通信协议和FPGA 的可编程性实现在线升级。

在这种方案中,系统可以在不中断当前工作的情况下进行在线升级。

该方案的实现可以通过以下步骤:1. 系统设定通过FPGA 的可重构性,可以实现对整个系统进行动态修改。

首先,需要设计新的硬件逻辑,以实现所需的升级。

这通常涉及到重新配置FPGA 的逻辑表达式或使用硬件描述语言(HDL)重新编译代码。

然后,所需的硬件逻辑将被配置到FPGA 中。

这可以通过从存储介质载入现有的逻辑代码或通过网络下载新的逻辑实现。

2. 系统更新使用基于网络连接的通信协议时,更新仅涉及修改FPGA 的逻辑代码,而不是整个设备。

一种基于fpga的cx9261芯片配置方法

一种基于fpga的cx9261芯片配置方法下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!FPGA技术在现代电子行业中扮演着越来越重要的角色,而CX9261芯片作为一种基于FPGA的解决方案,其配置方法对于设备性能的优化和功能实现至关重要。

可重构星载信息处理系统FPGA预规划技术

y s i s o f F P GA i n n e r a r c h i t e c t u r e a n d t h e F P GA r e s o u r c e u s a g e b y t y p i c a l t a s k s . T h e p r o p o s e d p l a n a l s o a n a l y z e d t h e

d o i : 1 0 . 3 9 6 9 / j . i s s n . 1 0 0 6 — 7 0 4 3 . 2 0 1 2 1 0 0 1 0

网络 出版地址 : h t t p : / / w w w . c n k i . n e t / k c m s / d e t a i l / 2 3 . 1 3 9 0 . U . 2 0 1 3 0 6 0 6 . 1 6 3 1 . 0 1 4 . h t m l 中图分类号 : V 4 4 3 文献标 志码 : A 文章编号 : 1 0 0 6 — 7 43 0 ( 2 0 1 3 ) 0 7 — 0 8 7 8 — 0 5

FPGA pr e - l a y o ut p l a n f o r r e c o n ig f ur a b l e

o n— b o a r d i n f o r ma t i o n p r o c e s s i n g s y s t e m

L I U Yu a n , S UN Z h a o we i , S HEN Yi ,XI NG Le i , W U Xi a n d e

o n— bo a r d r e l i a b i l i t y i n t h e o r y .T he s i mu l a t i o n r e s u l t s ho we d t ha t ,t h e p l a n mi g h t g r e a t l y e n ha n c e t he F PGA r e s o ur c e u t i l i z a t i o n r a t e b y u p t o 3 0% .F ur t h e r,i t a l s o i mp r o v e d t h e F PGA r e s o u r c e ut i l i z a t i o n r a t e r o un d a bo u t 5 0% wh e n FPGA h a d p e r ma n e n t f a u l t l o c a l l y . Ke ywo r d s: r e e o n ig f u r a b l e c o mp u t i n g; F PGA ;l a y o u t ;r e l i a b i l i t y;r e c o n ig f u r a bl e o n— b o a r d i n f o r ma t i o n p r o c e s s i n g

基于FPGA的动态可重构体系结构

可重构结构是一种 可 以根 据运算 情况 重组 自身资源 , 实 现硬件结构 自我优化 、 自我生成 的计算技 术 。动 态可重构 可 快速实现器件 的逻辑重 建 , 它的 出现为处 理大规模 计算 问题

提供 了一种兼具通用处理器 灵活性 和 A I SC电路 高速性 的解

整数处理单元 、 指令 C ce 数 据 C ce和存 储器管 理单元构 ah 、 ah 成了 L O 2处理器 的运 算核心 , A B和 A B两级总线构 EN 而 H P 成了处理器的外 围数 据 总线 , 通过 A B A B总线 桥相 连 并 H/P 接 。通过 两级 总线 的联合使用 ,E N L O 2可 以与 不同带宽 的存 储 器和外 部接 口相连接。

FPGA动态可重构技术原理及实现方法分析

Analysis of the Fundamental and ImplementationMethod about Dynamic R ecofigurable FPGAQIN Xiang2Ju1,2,ZHU Ming2Cheng2,ZH ANG Tai2Yi2,3,WEI Zhong2Yi11.Eletronic&Information Dpt.XI’AN Institute o f Technology and Engineering Science,Xi’an710048,China;2.Collegeo fInformation Engineering o f Shenzhen Univer sity,Shenzhen516080,China;3.Eletronic&Information Dpt.XI’AN Jiaotong Univer sity,Xi’an710049,ChinaAbstract: Dynamic Recon fogurable Field Programmable G ate Array(DR2FPG A)can con figure its partial or total logic res ources at run time,and change its functions on system in high speed.This paper presents s ome studies of DR2 FPG A,including basic architecture,recon figuration fundamental,C AD tools and im plement methods.Application of DR2FPG A is useful for designing high2performance systems,and helps to save hardware res ources.K ey w ords: FPG A;static recon figuration;dynamic recon figuration;total recon figuration;partial recon figuration EEACC: 1265B;1130BFPG A动态可重构技术原理及实现方法分析覃祥菊1,2,朱明程2,张太镒1,3,魏忠义11.西安工程科技学院电子与信息工程系 ,西安 710048;2.深圳大学E DA中心,深圳516080;3.西安交通大学电信学院,西安 710049摘要:FPG A动态重构技术主要是指对于特定结构的FPG A芯片,在一定的控制逻辑的驱动下,对芯片的全部或部分逻辑资源实现在系统的高速的功能变换,从而实现硬件的时分复用,,节省逻辑资源。

基于模块化设计方法实现FPGA动态部分重构汇总

基于模块化设计方法实现FPGA动态部分重构动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-BasedParTIalReconfiguration)和基于差别的设计方法(Difference-BasedPartialReconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1FPGA配置原理简介本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-IIPro。

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-Based ParTIal Reconfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1 FPGA配置原理简介本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-II Pro。

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和编程布线等资源[2]。

CLBs是构造用户所需逻辑的功能单元,IOBs提供封装引腿与内部信号引线的接口。

可编程互连资源提供布线通道连接可配置元件的输入和输出到相应的网络。

存储在内部配置存储器单元中的数值决定了FPGA实现的逻辑功能和互接方式。

Virtex FPGA的配置存储器是由配置列(Configuration Columns)组成的,这些配置列以垂直阵列的方式排列,如图1给出了Virtex-E XCV600E器件的配置列构成图。

配置存储器可分为五种配置列:Center 列包含四个全局时钟的配置信息;两个IOB 列存储位于器件左边和右边所有IOBs的配置信息;CLB列存储FPGA基本逻辑功能的配置信息;Block SelectRAM Content列存储内部块RAM的配置信息;Block SelectRAM Interconnect列存储内部块RAM间互联的配置信息[3]。

fpga重构

3 重构的步骤

步骤 1: 进行硬件功能设计,并综合生成网表文件 步骤 2: 创建一个 PlanAhead 工程

3 重构的步骤

步骤 1: 进行硬件功能设计,并综合生成网表文件 步骤 2: 创建一个 PlanAhead 工程 步骤 3:添加可重构模块 步骤 4:添加额外的可重构模块

3 重构的步骤

步骤 5: 添加黑盒子模块(可选项) 步骤 6: 为可重构区域进行布局 步骤 7:运行局部可重构设计规范检查

可重构区域 子模块B2 B

3 重构的步骤

步骤 9:生成并实现额外的配置

FPGA

静态 顶层模块 区域

可重构区域 子模块A2 A

可重构区域 子模块B1 B

3 重构的步骤

步骤 9:生成并实现额外的配置 步骤 10: 验证配置

3 重构的步骤

步骤 9:生成并实现额外的配置 步骤 10: 验证配置 步骤 11:生成并下载比特流配置文件(.bit 文件)

3 重构的步骤

步骤 5: 添加黑盒子模块(可选项) 步骤 6: 为可重构区域进行布局 步骤 7:运行局部可重构设计规范检查 步骤 8:实现并激活一个配置

FPGA

顶层模块 可重构区域 A

子模块A1

子模块A2 子模块B1 可重构区域 B 子模块B2

静态 区域

FPGA

静态 顶层模块 区域

可重构区域 子模块A1 A

2 重构的类型

2 重构的类型

FPGA

顶层模块 可重构区域 A

子模块A1

子模块A2 子模块B1 可重构区域 B 子模块B2

静态 区域

3 重构的步骤

步骤 1: 进行硬件功能设计,并综合生成网表文件 步骤 2: 创建一个 PlanAhead 工程

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种高档FPGA可重构配置方法

基于软件无线电的某机载多模式导航接收机能较好地解决导航体制不兼容

对飞行保障区域的限制,但由于各体制信号差异较大,各自实现其硬件将相当

庞大,若对本系统中数字信号处理的核心FPGA 芯片使用可重构的配置方法,

将导航接收机的多种模式以时分复用的方式得以实现,可以重复利用FPGA 的

硬件资源,达到了缩小体积,减小功耗,增加灵活性和降低系统硬件复杂程度

等目的。

本系统中的核心器件是新一代高档FPGA,适合于计算量大的数字信

号处理,包含实现数字信号处理的DSP 块、数字锁相环、硬件乘法器以及各

种接口等多项技术,支持远程更新,但其配置数据大,实现较为复杂。

采用

CPLD+FLASH 方案,有效的解决了这一问题。

1 FPGA 及其可重构技术简介

现代高速度FPGA 运行时需将其配置数据加载到内部SDRAM 中,改变SDRAM 里面的数据,可使FPGA 实现不同的功能,即所谓的可重构技术。

可

重构技术包括静态系统重构和动态系统重构[1]。

在FPGA 处于工作状态时对

其部分配置数据进行更改称为动态配置,否则称为静态配置。

由于本系统在工

作时需要改变整个FPGA 功能,所以采用静态配置。

这种配置是完全的,它对

整个FPGA 的功能、参数完全更改,而且其引脚功能也被更改。

系统的关键部

件为一片高档密度FPGA EP2S30,其要求的一次配置数据达1.205MBytes,故

其配置采用“Flash存储器+CPLD 主控器”的方案。

EP2S30 支持5 种配置方案,

即AS(Active Serial)模式、PS(PassiveSerial)模式、FPP(FastPassive Parallel)模式、PPA(Passive parallel Asynchronous)模式和JTAG 配置模式等。

为缩短配置时间,

本系统采用FPP 模式,配置数据不压缩,使各配置数据长度一致,以便于分配

Flash 存储空间,且只需要同数据率相同的时钟信号[2]。

2 可重构系统硬件

设计 2.1 芯片介绍 2.1.1 FPGA 芯片采用Altera 公司StratixⅡ系列FPGA,具。