官方例程Kinetis100MHz ADC

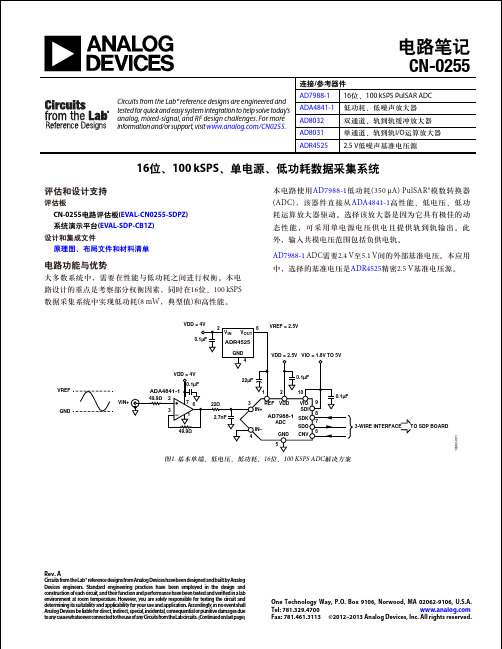

AD电路设计之16位、100 kSPS、单电源、低功耗

常见变化

PulSAR®系列的其它引脚兼容 16位 ADC提供更高的采样速 率: AD7988-5 (500 kSPS) 、 AD7980 (1 MSPS) 和 AD7983 (1.33 MSPS)。请注意,采样速率越高,功耗越高。或者, 如果需要更高的分辨率,合适的引脚兼容器件有 AD7691 (18 位, 250 kSPS) 、 AD7690(18 位, 400 kSPS), AD7982(18 位,1 MSPS差分输入)、AD7984(18位,1.33 MSPS)。 对于更高的输入电压范围,请为基准电压源和ADC驱动器 选择更高的基准电压和更高的电压供电轨。 图4中显示了AD7988-5(16位,500 kSPS)ADC在相似条件下 的动态性能;不过采样速率为500 kSPS。SNR等于86.37dB。

VDD = 4V 22µF 0.1µF VREF VIN+ GND

0.1µF 1 2 10 VIO SDI 9 8 7 3-WIRE INTERFACE 6

10382-001

ADA4841-1

49.9Ω 2 3 7 6 1 49.9Ω 4 22Ω 2.7nF 3

0.1µF

REF VDD IN+ ADC

AD8031

2 3

6

2

VIN

VOUT

6 1µF 0.1µF

VREF = 2.5V

ADR4525

GND 4

VDD = 2.5V VIO = 1.8V TO 5V

VREF +0.5 × VREF GND –0.5 × VREF VIN+ VCM 1µF GND VCM = VREF ÷ 2 = 1.25V 10kΩ 0.1µF 10kΩ

Kinetis E系列_ADC模块

飞思卡尔ADC例程指南例程功能飞思卡尔Kinetis E系列KE02产品ADC_demo例程实现ADC的FIFO操作,不断采样温度、BandGap及VREFH,且在三者采样完成后触发中断,串口打印出采样结果。

相关代码参考KE02-SC.zip中的ADC_demo例程。

运行平台✓FRDM-KE02Z✓IAR ARM IDE运行例程(IAR)1)使用USB cable连接FRDM-KE02Z开发板Min-B USB连接器(J6);2)加载ADC_demo工程后,选择【FLASH_128KB】,点击进行编译;3)编译成功后,点击进入调试界面;4)进入调试界面后,点击运行例程。

串口配置选择串口调试工具,使用图1所示的配置信息;图 1注:其中端口号为实际硬件的串口号,查看【我的电脑】->【设备管理器】->【端口】。

ADC模块介绍ADC模块的特点包括(图2为ADC原理框图):∙线性追次逐次逼近算法,提供8位、10位或12位分辨率;∙高达16个外部模拟输入、外部引脚输入和5个内部模拟输入,包括内部带隙、温度传感器和参考;∙输出格式为8位、10位或12位右对齐无符号格式;∙单次或连续转换(在单次转换后自动返回空闲状态);∙支持高达8个结果及选择通道FIFO深度;∙可配置的采样时间和转换速度/功率;∙转换完成标志和中断;∙输入时钟可从4个时钟源选择;∙在等待或停止模式下运行,支持低噪声运行;∙低噪声运行的异步时钟源;∙可选的异步硬件转换触发器;∙自动中断比较,带有小于、大于或等于可编程值;图2 ADC模块原理框图代码说明引脚名称方向功能PTH2 输出控制绿色led灯ADC_FIFO_Init(ADC_BASE_PTR)ADC_Isr()主程序流程图运行结果代码烧录完成后,主程序运行到等待字符输入状态(如图3和图4所示)。

图3N返回图4输入任意字符,ADC FIFO操作再次运行且绿灯翻转,并回到等待字符输入状态(如图5和图6所示)图 5图 6参考手册KE02芯片参考手册 MKE02Z64M20SF0RM/files/32bit/doc/ref_manual/MKE02Z64M20SF0RM.pdf?fpsp=1KE02芯片数据手册 MKE02P64M20SF0/files/32bit/doc/data_sheet/MKE02P64M20SF0.pdf?fpsp=1FRDM-KE02Z板原理图/files/soft_dev_tools/hardware_tools/schematics/FRDM-KE02Z_SCH.pdf?fpsp=1&WT_TYPE=Schematics&WT_VENDOR=FREESCALE&WT_FILE_FORMAT=pdf&WT_ ASSET=Downloads&sr=1FRDM-KE02Z用户指南/files/microcontrollers/doc/user_guide/FRDM-KE02ZUM.pdf?fpsp=1KE02-SC例程包/zh-Hans/webapp/sps/site/prod_summary.jsp?code=FRDM-KE02Z&fpsp=1&tab=Design_Tools_Tab。

kinetisDAC模块详解(中文资料)

作者:潘峰北京联合大学实训基地微博:/u/1262858854QQ:66797490博客:/panpan_0315/blog/本章内容仅供个人学习之用,请勿用于其它用途。

1.2DAC数模转换模块1.7.1 DAC简介Kinetis10包含两个独立的12位数模转换模块,DAC0和DAC1,用于将数字转换成对应的模拟电压。

转换后的模拟电压可由外部引脚输出,也可以通过芯片内部连接输入到比较器模块、放大器模块、和模数转换模块。

DAC的参考电压可以二选一,一个来自外部或VREF模块的输出,默认连接到DACREF_1;另一个时VDDA,默认连接到DACREF_2。

如果选择VDDA,则DAC的参考电压为3.3V。

12位二进制的表示范围为0~4095的无符号数。

对应数据转换成模拟电压输出范围从VREF/4096~VREF。

以VREF为3.3V计算,则是约0.8mV~3.3V,数据每变化1,输出电压变化约0.8mV。

将数据放入DAC的数据寄存器(DACx_DATL中的DACDATA[11:0]位),即可将数据转换为模拟电压。

电压Vout= VREF * (1 + DACDAT0[11:0])/4096。

在大量数据转换的应用中,也可以将数据放入DAC的缓冲区,由触发源输入触发信号,在触发信号的触发下,自动挨个将缓冲区中的数据转换为模拟电压。

缓冲区大小为1~16可设置大小的以word为单位的区域,转换的时候,由读指针指向正在转换的数据,可通过访问读指针获知当前正在转换的缓冲区单元。

数据转换的次序为从顶部到底部依次转换,从顶部到底部之间,用户可设置位置标记(watermark)作为预警位置,当读指针指向缓冲区顶部、底部或位置标记处时,都有状态位可供查询,也可以发出中断请求。

触发信号可来自PDB模块的TRIG输出详细可查看PDB模块设置。

同时DAC模块也支持DMA操作,可通过DMA的方式向缓冲区中传递数据,大大提高了效率。

Kinetis全系列选型手册-14

SPI

I2C

I2S

CA

线

口 接口 T

N

USB QTG(1)

2 41

2 51

2 51

2 41

2 51

2 51

18/16/2

3 5211

20/16/4

4 5211

32/32/6

5 6211

18/16/2

3 5211

20/16/4

4 5211

21/16/5

5 6211

32/32/6

5 6211

18/16/2

4 521

FS

5 6 3 1 1 FS

6 6 3 1 1 FS

32/32/6 8位 32/32/6 8位 32/32/6 8位

6 6 3 1 1 FS 5 6 3 1 1 FS 6 6 3 1 1 FS

32/32/6 8位

6 6 3 1 1 FS

以太网

定时器

模拟 能

电机控 带正 AD ADC ADC

22√

66

32/32/6

4 621

FS¢

2*8 2*2 2 4 38

22√

81

18/16/2

3 5 3 1 1 FS

2*8 2*2 2 2 22

13√

40(38)

20/16/2 4位

4 5 3 1 1 FS

2*8 2*2 2 3 27

13√

52(52)

21/16/5 4位

5 6 3 1 1 FS

2*8 2*2 2 5 33

USB QTG(1)

FS¢ FS¢ FS¢ FS¢ FS¢ FS¢ FS¢ FS¢

以太网

定时器

模拟 能

一种12位100MHz流水线ADC采样保持电路

一种12位100MHz流水线ADC采样保持电路作者:栾舰孙海燕来源:《科技传播》2016年第12期摘要本文设计了一款基于SMIC130nm标准CMOS工艺的应用于12位流水线ADC的采样保持电路。

采保(SHA)采用翻转围绕式结构,以减小电容的匹配要求、降低整体功耗;采用增益提高型二级运算放大器,以保证所设计的电路处理信号的速率与精度。

通过仿真结果表明,采保电路(SHA)符合12位流水线ADC的性能要求。

关键词流水线ADC;采样保持电路;增益提高运算放大器中图分类号 TP33 文献标识码 A 文章编号 1674-6708(2016)165-0237-02采保电路(SHA)对于流水线ADC很重要,其作用是对持续变化的模拟量输入信号的值进行采集,并在输出端对这个采样信号保持一段时间,以保证在给定采样频率下,后续电路对其进行处理,采保电路(SHA)的性能指标直接影响流水线ADC的速率与精度。

本文对采保(SHA)电路进行研究,通过对两种不同类型的采保的分析,最终选择翻转围绕式结构,设计了高性能的增益提高型运放,以满足电路的速率与精度的要求,最终设计实现了应用于12位100MHz流水线ADC的采保(SHA)电路。

1 采保结构的分析与选择闭环结构的采保(SHA)电路主要有两种结构[1-3]:重分配电荷式和翻转围绕式。

在采样相,重分配电荷式采保的采样电容对输入模拟量进行采集;在保持相,对采集信号的电容上的电荷重新分配,使其移动到反馈电容上,从而实现采样保持功能。

翻转围绕式采保则是在保持相通过翻转采集信号的电容,实现了采样保持作用。

二者相比较,在信噪比相同要求下,重分配电荷式采保电路在采样相与保持相的热噪声均为翻转围绕式采保电路的2倍。

且因为重分配电荷式采保电路(SHA)的反馈系数是翻转围绕式采保电路(SHA)的一半,所以在相同建立速率要求下,前者的单位增益带宽是后者的两倍,即前者的运放要比后者的运放功耗大很多。

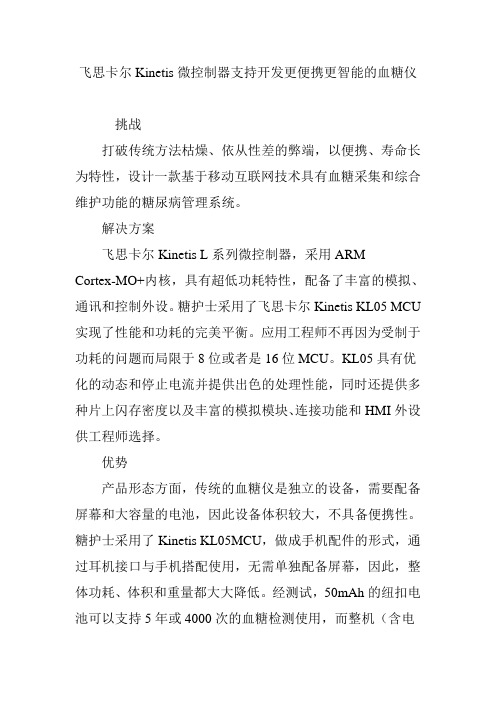

飞思卡尔Kinetis微控制器支持开发更便携更智能的血糖仪

飞思卡尔Kinetis微控制器支持开发更便携更智能的血糖仪挑战打破传统方法枯燥、依从性差的弊端,以便携、寿命长为特性,设计一款基于移动互联网技术具有血糖采集和综合维护功能的糖尿病管理系统。

解决方案飞思卡尔Kinetis L系列微控制器,采用ARMCortex-MO+内核,具有超低功耗特性,配备了丰富的模拟、通讯和控制外设。

糖护士采用了飞思卡尔Kinetis KL05 MCU 实现了性能和功耗的完美平衡。

应用工程师不再因为受制于功耗的问题而局限于8位或者是16位MCU。

KL05具有优化的动态和停止电流并提供出色的处理性能,同时还提供多种片上闪存密度以及丰富的模拟模块、连接功能和HMI外设供工程师选择。

优势产品形态方面,传统的血糖仪是独立的设备,需要配备屏幕和大容量的电池,因此设备体积较大,不具备便携性。

糖护士采用了Kinetis KL05MCU,做成手机配件的形式,通过耳机接口与手机搭配使用,无需单独配备屏幕,因此,整体功耗、体积和重量都大大降低。

经测试,50mAh的纽扣电池可以支持5年或4000次的血糖检测使用,而整机(含电池)重量仅有9克。

该产品通过国家食品药品监督局严格认证,获得CFDA(国家食品药品监督管理总局)证书(湘食药监械(准)字2014第2400052号)。

在数据的管理方面,使用传统血糖仪的患者需要把测量的血糖数据抄到本子上,就诊时拿给医生看,这样麻烦且血糖数据的变化趋势展示不直观。

有了糖护士,糖尿病患者测量的数据自动存储到智能手机和云端,它可以很方便地以曲线、表格的形式展示数据。

通过移动互联网,医生可以远程查看数据,然后指导患者调整饮食、运动、用药。

通过糖护士软件,患者还可以方便的记录日常饮食、运动、用药情况,通过设置提醒确保按时测量血糖和用药,并且可以在软件上浏览丰富的糖尿病知识。

寻找合适的技术合作伙伴北京糖护科技有限公司首席技术官(CTO)Brent Zheng (郑志华)表示:“我们需要寻找既能高速运算又具有低功耗特性的MCU,普通的8/16位MCU已经无法满足糖护士产品研发的需求,一筹莫展之时,我们找到了飞思卡尔的KL05,它完全能满足我们对功耗和运算速度的双向需求。

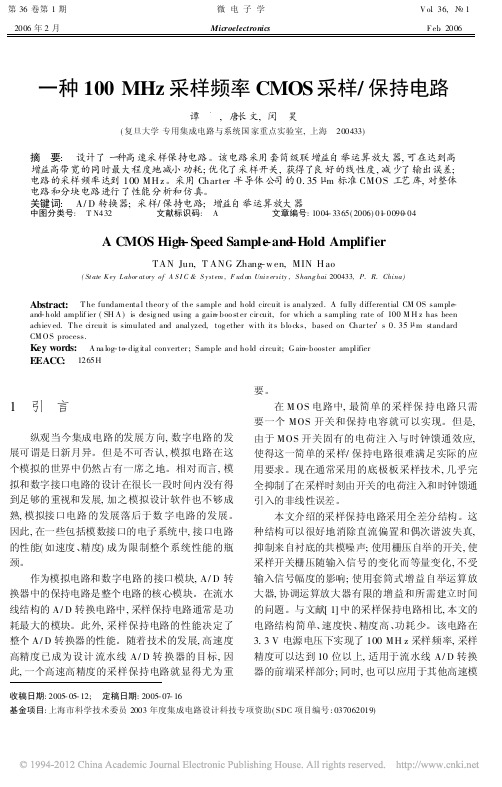

一种100MHz采样频率CMOS采样_保持电路

Abstract: T he fundamenta l theor y of the sample and hold circuit is analyzed. A fully differential CM OS sample-

and- hold amplif ier ( SH A ) is desig ned using a gain- boo st er cir cuit, for which a sampling rate of 100 M H z has been achiev ed. T he circuit is simulated and analyzed, tog ether with it s blo cks, based on Char ter s 0. 35 m standard CM O S process.

间, 使运放能够稳定地工作, 要求自举运放的单位增 益频率 3 满足 2 < 3 < 5 的条件( 其中, 5 是整个 运放的第二极点) 。为了满足设计要求, 在半个时间 周期( 5 ns) 之内完全建立, 需要对自举运放进行电 容补偿, 使其带宽满足上述要求, 从而消除由自举运 放引入的零点和极点问题。

92

谭 等: 一种 100 M H z 采样频 率 CM OS 采样/ 保持电路

2006 年

图 2 自举电路中采样开关的栅源电压

4 套筒式增益增强运算放大器的设计

采样保持电路中的核心部件是运算放大器, 其 性能直接决定了采样保持电路是否可以实现功能。 运算放大器的整体电路如图 3 所示。

度和输入输出电压的指标要求。对于自举运放, 并 不需要很高的增益, 但是希望得到较大的动态范围。 在设计的过程中, 要考虑自举运放和整体运放直接 带宽的相互关系[ 4] 。

12位100MHz流水线型ADC行为级建模与仿真

12位100MHz流水线型ADC行为级建模与仿真作者:王月海刘红岩来源:《电脑知识与技术》2016年第24期摘要:为了提高大规模集成电路的设计效率,该文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。

通过仿真结果验证得到SNDR为72.9465dB,SNR为72.9484dB距离理想的12比特ADC模型的SNR只差1.0516dB,ENOD为11.8155距离理想的12比特ADC的ENOD只差0.1845,以此验证了本文的ADC是高速有效的ADC模型。

关键词: Verilog-A;行为级建模;流水线型ADC中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)24-0236-03行为级建模的方法有很多,Matlab/Simulink建模 [1],模型通用性和可移植性差。

采用VHDL-AMS(VHDL Analog and Mixed-Signal Extensions)建模[2],但并没有创建出针对流水线的实际非理想因素进行特定的流水线结构ADC模型。

利用Pspice和Simulink进行联合仿真[3],但是普通用户无法得知系统内部详细的电路结构和参数。

基于Verilog-A对多位每级流水线ADC做行为级建模,Verilog-A可以使用电路仿真工具Spectre仿真,而且可以精确描述模拟电路中的各种性能参数,Verilog-A主要通过基尔霍夫电流定律和基尔霍夫电压定律,描述输入输出信号之间的电路行为,verilog-A可以描述时钟抖动、运放增益等非理想因素。

本文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Y

输出四次采样结果和 电位器经滤波结果

程序结束

运行效果

参考资料

TWR-K60D100M 开发板用户手册: /files/32bit/doc/ref_manual/TWRK60D100MUM.pdf K60 100MHz Silicon2.x 开发手册: /files/32bit/doc/ref_manual/K60P100M100SF2V2R M.pdf 飞思卡尔 Kinetis 芯片中 NVIC 模块的中断寄存器的介绍及其应用举例: /bbs/article_1280_551272.html

串口配置

选择串口调试工具,使用下图配置信息;

代码说明

ADC 例程使用下列 IO 引脚资源,以及每个 IO 引脚的功能描述:

引脚名称

方向

功能

PTA11

数字输出 显示 ADC1 触发状态 1:A 触发 0:B 触发(橙色 LED)

PTA28

数字输出 显示 ADC0 触发状态 1:A 触发 0:B 触发(黄色 LED)

ADC 例程流程图

主函数入口 初始化状态显示引脚

关闭中断请求 配置中断向量地址

开模块时钟 配置 PDB 与 ADC 关系

设置 PDB 模块 设置 ADC 模块 输出程序说明 开启中断请求和总中断 软件触发开启 PDB 计数

查询串口是 否收到字符

Y 关闭 PDB

N

查询四次触发采

N

样转换是否完成

关闭中断请求 打印程序结束信息

PTA29

数字输出 每次翻转电平表示 PDB 复位并开始计数(绿色 LED)

ADC0_DM0 模拟输入

ADC0 的 A 触发采样端

ADC0_DM1 模拟输入 ADC0 的 B 触发采样端(上拉到 V_BRD 默认 3.3V)

ADC1_DM0 模拟输入

ADC1 的 A 触发采样端(电位器可调端)

ADC1_DM1 模拟输入

运行平台

TWR-K60D100M IAR ARM IDE

运行例程(IAR)

1) 使用 USB cable 连接 TWR-K60D100M 开发板 Min-B USB 连接器(J17); 2) 短接 J5 跳帽,将电位器 R50 的可调端连接至 ADC1_DM1 即 ADC1 的采样端口; 3) 加载 ADC 工程后,选择【RAM_128KB】,点击 进行编译; 4) 编译成功后,点击 进入调试界面; 5) 进入调试界面后,点击 运行例程。

飞思卡尔中文论坛支持小组所在地:/bbs/forum_1280.html

飞思卡尔 ADC 例程指南

例程功能

飞思卡尔 Kinetis 100MHz Silicon2.x 产品 ADC 例程实现 MCU 通过 PDB(可编程延迟模块) 连续地延时触发 ADC 采样,并通过串口输出采样结果的功能。

ADC1 的 B 触发采样端(电位器可调端)

主程序(main 函数)代码说明 PDB 硬件触发 ADC(Hw_Trig_Test.c)注释说明

PDB 硬件触发 ADC(Hw_Trig_Test 函数)代码说明

PDB 模块配置部分代码说明

ADC 模块配置部分代码说明

ADC1 b_isr 函数)代码说明