eda论文报告

EDA技术论文报告

目录1.EDA概述 (1)2.EDA发展的最新动向2.1新器件 (2)2.2新工具软件 (2)2.3在FPGA中植入嵌入式系统处理器 (2)2.4基于FPGA的DSP系统设计 (2)2.5计算机处理器设计 (3)2.6与ASIC市场的竞争技术 (3)3.关于EDA技术的应用 (3)4.电子抢答器的EDA设计与实现4.1 电子抢答器的功能 (4)4.2 电子抢答器的结构原理 (5)4.3 体会 (8)参考文献 (9)摘要:随着微电子技术和计算机技术的不断发展,在涉及通信、国防、航天、工业自动化、仪器仪表等领域工作中,EDA技术的含量以惊人的速度上升,从而使它成为当今电子技术发展的前沿之一;本文首先阐述了EDA的基本概念和发展过程,并以硬件描述语言(VHDL) 为主要表达方式,以QuartusⅡ开发软件为设计工具,阐述了电子抢答器的工作原理和软硬件实现方法,并对所设计的电子抢答器进行了时序仿真和硬件验证。

关键词: EDA 发展与应用电子抢答器 VHDL QuartusⅡ1. EDA概述EDA(Electronic Design Automation)技术,近十年来随着微电子和计算机技术的进步及电子产品市场运作节奏的进一步加快已迈入了一个全新的阶段[1],其特点是通过软件方式的设计和测试,达到对既定功能的硬件系统的设计和实现。

是一种以计算机为工作平台,利用计算机图形学、拓扑逻辑学、计算数学以至人工智能学等多种计算机应用学科的最新成果而开发出来的一整套软件工具;是一种帮助电子设计工程师从事电子系统设计的综合技术。

它的出现极大的改变了传统的设计方法、设计过程乃至设计观念,使广大的电子设计工程师开始实现“概念驱动工程”的梦想。

设计师们摆脱了大量的辅助设计工作,而把精力集中于创造性的方案与概念构思上,用新的思路来发掘硬件设备的潜力,从而极大地提高了设计效率,缩短了产品的研制周期。

尤其是九十年代初Lattice 公司首创ISP(In System Programmability)技术,加之各大VLSI厂商纷纷推出各种系列的大规模和超大规模FPGA 和CPLD产品, 以大规模集成电路为物质基础的EDA技术终于打破了软硬件之间的最后屏障,使硬件设计软化了,而不受产品是否已交付使用的限制,给电子产品的设计和生产带来了革命性的变化。

eda实验论文

EDA电子实训乒乓球游戏机专业:电子信息科学与技术组长:赵林帆组员:何晨旭、孙毅指导教师:任国凤完成时间:2017年6月19日摘要 (1)1、EDA (2)1.1EDA简介 (2)1.2设计语言VHDL (2)2、乒乓球游戏机的设计 (2)2.1设计要求 (2)2.2设计说明 (3)2.2.1整体思路 (3)2.2.2具体设计思路 (4)3、编程 (5)3.1分频器模块 (5)3.2状态机编程设计 (6)3.3七段数码管显示 (13)3.4整体电路 (17)4、系统编译和仿真 (17)4.1仿真 (17)4.1.1球运动仿真 (17)4.1.2得分仿真 (17)4.1.3总仿真图 (17)4.2结果图 (18)5、心得与体会 (18)摘要EDA(电子设计自动化)技术是现代电子工程领域的一门新技术。

它提供了基于计算机和信息技术的电路系统设计方法。

EDA技术的发展和推广应用极大地推动了电子工业的发展。

乒乓球是中华人民共和国国球,是一种极为流行的球类体育项目。

随着科学技术的发展,人类进入信息化社会,信息社会的发展离不开电子产品的进步。

现代电子产品发展得越来越快,于是人们将乒乓球与电子产品结合在一起,形成了乒乓球游戏机。

通过拨码开关模拟球拍,发光二极管模拟乒乓球,进行游戏的操作。

关键词:EDA 电子工业信息社会乒乓球游戏机1、EDA1.1EDA简介EDA是电子设计自动化(ElectrONic Design AUTOMATION)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

集成电路设计EDA报告

集成电路设计EDA 实验报告学院:电信学部专业:微电子与固体电子学班级:********姓名:Wang Ke qin指导老师:*******学号:*******日期:2012-6-12目录1.EDA发展简介 (1)2.IC设计中所使用的EDA工具 (1)3.反相器(inventer)设计 (4)3.1.实验目的 (4)3.2.设计要求 (5)3.3.反相器电路原理图设计 (5)3.3.1.电路结构和工作原理 (5)3.3.2.原理图设计 (5)3.3.3.生成符号图 (6)3.3.4.反相器功能验证 (6)3.4.电路版图设计与规则验证 (11)3.4.1.工艺与版图层次描述 (11)3.4.2.版图设计 (11)3.5.小结 (13)4.由版图画出原理图并说明电路功能 (13)4.1.标准单元IT01D0 (13)4.1.1.IT01D0的版图 (13)4.1.2.IT01D0的原理图提取 (13)4.1.3.IT01D0的原理图网表提取 (14)4.1.4.IT01D0的LVS验证 (15)4.2.标准单元ND02D2 (15)4.2.1.ND02D2的版图 (15)I4.2.2.ND02D2的原理图提取 (15)4.2.3.ND02D2的原理图网表提取 (16)4.2.4.ND02D2的LVS验证 (17)4.3.标准单元DFNNSNRQQB1 (18)4.3.1.DFNNSNRQQB1的版图 (18)4.3.2.DFNNSNRQQB1的原理图 (18)4.3.3.DFNNSNRQQB1的符号 (19)4.3.4.DFNNSNRQQB1的测试电路 (19)4.3.5.DFNNSNRQQB1测试电路的网表提取 (20).end (21)4.3.6.DFNNSNRQQB1的波形仿真 (21)4.3.7.DFNNSNRQQB1的LVS验证 (22)4.4.小结 (23)5.四位移位寄存器的设计 (23)5.1.四位移位寄存器的原理图设计 (23)5.2.四位移位寄存器的原理图网表提取 (24)5.3.四位移位寄存器的电路仿真 (26)5.4.四位移位寄存器的版图设计 (27)5.5.四位移位寄存器的DRC和LVS验证 (27)5.4.1.四位移位寄存器的DRC验证 (27)5.4.2.四位移位寄存器的LVS验证 (28)5.6.小结 (28)6.两级运算放大器电路设计 (28)II6.1.运算放大器的设计目标 (28)6.2.运算放大器的电路结构 (29)6.3.手工计算晶体管尺寸 (30)6.4.电路仿真与参数调整 (31)6.4.1.电路仿真的参数调整参考 (31)6.4.2.增益Av及单位增益带宽GB的仿真 (32)6.4.3.共模输入范围ICMR的仿真 (34)6.4.4.输出摆率的仿真 (36)6.4.5.共模抑制比CMRR的仿真 (38)6.4.6.电源抑制比PSRR的仿真 (41)6.4.7.摆率SR和建立时间的仿真 (45)6.5.差分放大器的版图设计 (47)6.5.1.差分放大器原理图的网表提取 (48)6.5.2.差分放大器的版图 (48)6.5.3.差分放大电路的DRC验证 (49)6.5.4.差分放大电路的LVS验证 (49)6.6.小结 (49)7.总结 (50)III1.EDA发展简介集成电路在性能不断提高、规模和复杂度不断增大的同时,价格却不断下降,而且设计周期越来越短。

EDA实验 报告范文

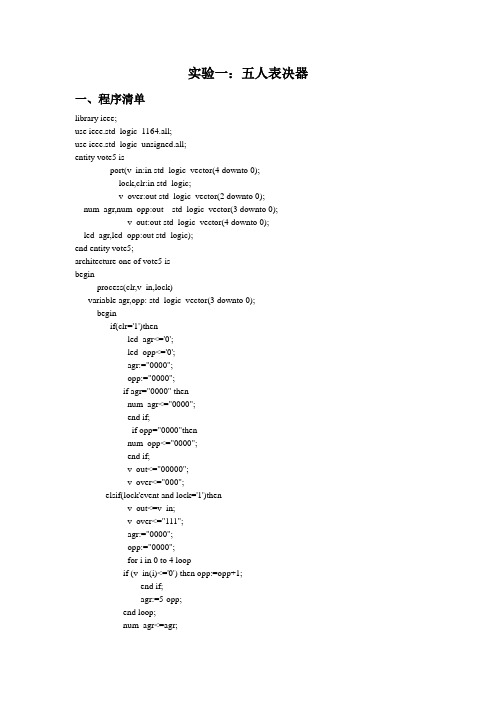

实验一:五人表决器一、程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity vote5 isport(v_in:in std_logic_vector(4 downto 0);lock,clr:in std_logic;v_over:out std_logic_vector(2 downto 0);num_agr,num_opp:out std_logic_vector(3 downto 0);v_out:out std_logic_vector(4 downto 0);led_agr,led_opp:out std_logic);end entity vote5;architecture one of vote5 isbeginprocess(clr,v_in,lock)variable agr,opp: std_logic_vector(3 downto 0);beginif(clr='1')thenled_agr<='0';led_opp<='0';agr:="0000";opp:="0000";if agr="0000" thennum_agr<="0000";end if;if opp="0000"thennum_opp<="0000";end if;v_out<="00000";v_over<="000";elsif(lock'event and lock='1')thenv_out<=v_in;v_over<="111";agr:="0000";opp:="0000";for i in 0 to 4 loopif (v_in(i)<='0') then opp:=opp+1;end if;agr:=5-opp;end loop;num_agr<=agr;num_opp<=opp;if(agr>opp)thenled_agr<='1';led_opp<='0';elseled_agr<='0';led_opp<='1';end if;end if;end process;end architecture one;三.仿真1. 功能仿真波形2.时序仿真波形实验二:九九乘法表系统的设计一、程序清单library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;entity multiply is --构造体描述4位乘法器port( clk:in std_logic;a,b:in std_logic_vector(3 downto 0);led_data:out std_logic_vector(7 downto 0);seg_sel:out std_logic_vector(2 downto 0) );end multiply;architecture rtl of multiply issignal led_data2,led_data1,led_data0: std_logic_vector(7 downto 0);--LED显示代码,寄存十位个位的数signal displayclk: std_logic;beginprocess(a,b)variable s: std_logic_vector(7 downto 0);--乘积variable bai,shiwei,gewei: std_logic_vector(3 downto 0);--乘积的十位个位begins(7 downto 0):=a(3 downto 0)*b(3 downto 0);if s>="11001000" then bai:="0010";s:=s-"11001000";elsif s>="01100100" then bai:="0001";s:=s-"01100100";else bai:="0000";end if;if s>="01011010" then shiwei:="1001";s:=s-"01011010";gewei:=s(3 downto 0);--90以上 elsif s>="01010000" then shiwei:="1000";s:=s-"01010000";gewei:=s(3 downto 0);--80以上 elsif s>="01000110" then shiwei:="0111";s:=s-"01000110";gewei:=s(3 downto 0); --70以上 elsif s>="00111100" then shiwei:="0110";s:=s-"00111100";gewei:=s(3 downto 0);--60以上 elsif s>="00110010" then shiwei:="0101";s:=s-"00110010";gewei:=s(3 downto 0);--50以上 elsif s>="00101000" then shiwei:="0100";s:=s-"00101000";gewei:=s(3 downto 0);--40以上 elsif s>="00011110" then shiwei:="0011";s:=s-"00011110";gewei:=s(3 downto 0);--30以上 elsif s>="00010100" then shiwei:="0010";s:=s-"00010100";gewei:=s(3 downto 0);--20以上 elsif s>="00001010" then shiwei:="0001";s:=s-"00001010";gewei:=s(3 downto 0);--10以上 else gewei:=s(3 downto 0);shiwei:="0000";end if;case bai iswhen "0001" => led_data2<="11111001";when "0010" => led_data2<="10100100";when others => led_data2<="11111111";end case;case shiwei iswhen "0000" => led_data1<="11000000";when "0001" => led_data1<="11111001";when "0010" => led_data1<="10100100";when "0011" => led_data1<="10110000";when "0100" => led_data1<="10011001";when "0101" => led_data1<="10010010";when "0110" => led_data1<="10000010";when "0111" => led_data1<="11111000";when "1000" => led_data1<="10000000";when "1001" => led_data1<="10010000";when others => led_data1<="11111111";end case;case gewei iswhen "0000" => led_data0<="11000000";when "0001" => led_data0<="11111001";when "0010" => led_data0<="10100100";when "0011" => led_data0<="10110000";when "0100" => led_data0<="10011001";when "0101" => led_data0<="10010010";when "0110" => led_data0<="10000010";when "0111" => led_data0<="11111000";when "1000" => led_data0<="10000000";when "1001" => led_data0<="10010000";when others => led_data0<="11111111";end case;end process;process(clk)variable cnt:integer range 0 to 20000; --1KHZ扫描显示时钟 beginif clk'event and clk='1' then cnt:=cnt+1;if cnt<10000 then displayclk<='1';elsif cnt<20000 then displayclk<='0';else cnt:=0;displayclk<='0';end if;end if;end process;process (displayclk) --显示两位variable cnt2: std_logic_vector(1 downto 0);beginif displayclk'event and displayclk='1' then cnt2:=cnt2+1;if cnt2="01" then seg_sel<="001";led_data<=led_data0;elsif cnt2="010" then seg_sel<="010";led_data<=led_data1;elsif cnt2="11" then cnt2:="00"; seg_sel<="100";led_data<=led_data2;end if;end if;end process;end rtl;二、仿真设计输入文件经maxplus软件开发系统编译、处理,由功能仿真器进行模拟,获得仿真波形如图6所示。

eda技术实验报告

eda技术实验报告EDA技术实验报告引言EDA(Electronic Design Automation)技术是电子设计自动化的缩写,是现代电子设计中不可或缺的一环。

它通过计算机辅助设计,提高了电路设计的效率和质量。

本文将介绍EDA技术的背景、应用和实验结果。

背景随着电子产品的不断发展,电路设计变得越来越复杂,传统的手工设计已经无法满足需求。

EDA技术的出现填补了这一空白。

它利用计算机的强大计算能力和算法,帮助设计师完成电路设计、仿真、布局和验证等工作。

应用1. 电路设计EDA技术的核心应用是电路设计。

通过EDA工具,设计师可以绘制电路图、选择器件、进行参数设置等。

EDA工具还可以自动进行电路优化,提高电路性能。

2. 仿真验证在电路设计完成后,需要对电路进行仿真验证。

EDA技术可以提供准确的仿真结果,帮助设计师分析电路的性能和稳定性。

仿真验证可以帮助设计师发现潜在的问题,提前解决。

3. 物理布局物理布局是将电路逻辑转化为实际的物理结构。

EDA技术可以自动进行物理布局,优化电路的面积和功耗。

物理布局的好坏直接影响到电路的性能和可靠性。

4. 电路验证在电路设计完成后,需要进行电路验证,确保电路的正确性和可靠性。

EDA技术可以自动进行电路验证,提供准确的验证结果。

电路验证可以帮助设计师发现设计缺陷,提高电路的可靠性。

实验设计在本次实验中,我们选择了一款EDA工具进行实验。

首先,我们设计了一个简单的数字电路,包括与门和或门。

然后,利用EDA工具进行电路仿真和优化。

最后,对电路进行物理布局和验证。

实验结果通过实验,我们得到了以下结果:1. 仿真结果显示,设计的数字电路在不同输入条件下均能正确输出结果,验证了电路的正确性。

2. 通过优化算法,我们成功提高了电路的性能,减少了功耗和面积。

3. 物理布局结果显示,电路的布局紧凑,满足了设计要求。

4. 电路验证结果显示,电路的功能和性能均符合设计要求,验证了电路的可靠性。

EDA实验报告完结版

EDA实验报告完结版一、实验目的本次 EDA 实验的主要目的是通过实际操作和设计,深入理解和掌握电子设计自动化(EDA)技术的基本原理和应用。

具体而言,包括熟悉 EDA 工具的使用方法,学会运用硬件描述语言(HDL)进行逻辑电路的设计与描述,以及通过综合、仿真和实现等流程,将设计转化为实际的硬件电路,并对其性能进行评估和优化。

二、实验环境本次实验所使用的 EDA 工具为_____,该工具提供了丰富的功能模块和强大的设计支持,包括原理图编辑、HDL 代码编写、综合、仿真和下载等。

实验所使用的硬件平台为_____开发板,其具备多种接口和资源,便于对设计的电路进行实际验证和测试。

三、实验内容1、基本逻辑门电路的设计与实现使用 HDL 语言(如 Verilog 或 VHDL)设计常见的基本逻辑门电路,如与门、或门、非门等。

通过编写代码,对逻辑门的输入输出关系进行描述,并进行综合和仿真,验证设计的正确性。

2、组合逻辑电路的设计与实现设计并实现较为复杂的组合逻辑电路,如加法器、减法器、编码器、译码器等。

运用 HDL 语言描述电路的功能,进行综合和仿真,确保电路在各种输入情况下的输出结果符合预期。

3、时序逻辑电路的设计与实现设计常见的时序逻辑电路,如计数器、寄存器、移位寄存器等。

在设计过程中,考虑时钟信号、同步复位和异步复位等因素,通过仿真验证时序逻辑的正确性,并对电路的性能进行分析。

4、有限状态机(FSM)的设计与实现设计一个有限状态机,实现特定的功能,如交通信号灯控制器、数字密码锁等。

明确状态转移条件和输出逻辑,通过编写 HDL 代码实现状态机,并进行综合和仿真,验证其功能的准确性。

5、综合与优化对设计的电路进行综合,生成门级网表,并通过优化工具对电路进行面积、速度等方面的优化,以满足特定的设计要求。

6、硬件实现与测试将综合后的设计下载到硬件开发板上,通过实际的输入输出信号,对电路的功能进行测试和验证。

观察电路在实际运行中的表现,对出现的问题进行分析和解决。

EDA实验报告(绝对有用)

EDA实验报告(绝对有用)本次实验主要针对数据分析中的探索性数据分析(Exploratory Data Analysis, EDA)进行了深入学习和实践。

EDA是一种针对数据集中每个变量和变量之间关系的视觉和统计方法的分析方法,它旨在识别有趣的模式、特征和异常,这些信息有助于之后的建模和分析。

在实验中,我们采用了Python编程语言进行数据分析。

我们利用了NumPy、Pandas、Matplotlib、Seaborn等库进行计算、数据处理、数据可视化等操作。

我们选取了Titanic 号乘客的数据集进行实验,该数据集包含了乘客的个人信息、船票信息、生还情况等信息。

该数据集是一个经典的数据集,经常被用来进行数据分析和建模。

实验主要从以下几个方面进行了数据探索。

首先,我们对数据集的整体情况进行了概述。

我们利用head()和sample()函数查看了数据集的前5和5个随机样本,了解了数据集的变量的类型和取值范围。

然后,我们通过describe()函数来对数据集进行统计摘要分析,包括每个变量的均值、标准差、最小值、最大值等,从而对数据集的分布情况进行了把握。

接着,我们利用info()函数查看了数据集中的缺失值和数据类型,进一步了解了数据清洗的工作量。

在了解了数据整体情况之后,我们进一步对数据集的不同变量进行了探索。

我们先对生还情况(“Survived”)进行了统计分析,以了解不同乘客的生还率分布情况。

我们利用pie()和countplot()函数分别使用饼图和直方图来展示了不同生还情况的比例和数量。

我们发现,生还乘客和死亡乘客的比例为38.4%和61.6%。

接着,我们对乘客的性别(“Sex”)进行了分析,以确定男女乘客的生还率差异情况。

我们利用countplot()函数来展示男女乘客的数量和生还率情况,发现女性乘客的生还率比男性高得多。

这进一步证明了Titanic号上的“女士优先”政策。

我们还分析了乘客的舱位等级(“Pclass”)和年龄(“Age”)等变量,以确定这些因素与生还率的关系。

eda技术与实验报告

eda技术与实验报告

EDA技术与实验报告

近年来,EDA技术在电子设计领域发挥着越来越重要的作用。

EDA(Electronic Design Automation)技术是指利用计算机软件和硬件工具来设计、验证和生成

电子系统的过程。

它涵盖了从电路设计到芯片制造的整个流程,包括逻辑设计、物理设计、验证和仿真等各个环节。

在实验报告中,我们将重点介绍EDA技术在电子设计中的应用和优势。

首先,EDA技术可以大大提高设计效率和质量。

利用EDA工具,设计师可以快速完成

电路设计和验证,大大缩短了产品的上市时间。

其次,EDA技术可以帮助设计

师发现和解决潜在的设计问题,提高了设计的可靠性和稳定性。

此外,EDA技

术还可以实现自动化设计和优化,从而降低了设计成本和风险。

在实验中,我们使用了一款先进的EDA工具来设计和验证一个数字电路。

通过

该实验,我们深刻体会到了EDA技术的强大功能和优势。

在设计过程中,我们

可以通过EDA工具快速搭建电路原型,并进行逻辑仿真和时序分析,从而验证

设计的正确性和性能。

此外,EDA工具还提供了丰富的库元件和模型,可以大

大简化设计过程和提高设计的可靠性。

总的来说,EDA技术在电子设计领域发挥着不可替代的作用。

它不仅提高了设

计效率和质量,还为设计师提供了强大的工具和支持。

随着科技的不断发展,EDA技术将继续发挥着重要的作用,推动电子设计领域的进步和发展。

希望通

过本次实验报告的分享,可以让更多的人了解和认识EDA技术的重要性和价值。

eda实验报告

eda实验报告EDA(Exploratory Data Analysis)是一种常用的数据分析方法,通过对数据集进行可视化、统计和计算,来揭示数据中的潜在规律和趋势。

下面是一份关于EDA实验的报告,总字数700字。

实验目的:1. 熟悉EDA方法和流程;2. 分析数据集的特征和表现;3. 发现数据集中的异常和趋势。

实验过程:1. 数据收集与预处理本次实验使用的数据集是关于某公司销售数据的报告。

首先,收集了公司销售数据,并进行了数据清洗与预处理,包括去除重复数据、处理缺失值和异常值等。

2. 数据可视化通过绘制直方图、散点图和箱线图等可视化图表,分析如下几个方面:(1)销售额分布情况:绘制直方图分析销售额的分布情况,观察是否存在明显的集中趋势或异常值。

(2)销售额与时间的关系:绘制时间序列图,观察销售额随时间的变化趋势。

(3)不同产品类别的销售情况:绘制柱状图比较不同产品类别的销售额,从而分析各类别产品的市场表现。

(4)销售额与其他因素的关系:绘制散点图分析销售额与其他因素(如广告费用、产品价格等)之间的关系,发现潜在的规律。

3. 数据统计与计算通过对数据集进行统计和计算,揭示数据集中的特征和规律,如:(1)平均销售额:计算销售额的平均值,以了解公司销售的平均水平。

(2)销售额的标准差:计算销售额的标准差,以评估销售额的波动性和不稳定性。

(3)销售额的趋势:使用回归分析等方法,拟合销售额与时间的关系,从而预测未来的销售趋势。

实验结果:通过数据可视化和统计计算,我们获得了以下一些结果:1. 销售额的分布呈正偏态,大部分销售额集中在较低水平,但也存在一些异常值;2. 销售额随时间呈现出上升的趋势,说明公司的销售业绩在逐渐提升;3. 不同产品类别的销售额差异较大,其中某些类别的销售额明显高于其他类别;4. 销售额与广告费用和产品价格之间存在一定的正相关关系,即投入更多的广告费用和提高产品价格可以带来更高的销售额。

《EDA技术》实验报告

《EDA技术》实验报告

本次实验报告是关于EDA技术的研究和应用。

EDA技术全称电子设计自动化技术,能

够实现电子设计的自动化和优化。

首先,我们讨论了EDA技术的应用范围。

EDA技术主要应用于现代集成电路的设计和

制造,目的是提高电路的性能,并减少设计和制造的成本和时间。

EDA技术可用于设计各

种电路,包括数字电路、模拟电路、混合信号电路和射频电路等。

其次,我们介绍了EDA技术的主要工具。

EDA技术工具包括原理图编辑器、电路模拟器、布局编辑器和综合工具等。

这些工具可以协同工作,在电路设计的不同阶段对电路进

行分析和优化。

接着,我们描述了EDA技术的设计流程。

EDA技术的设计流程分为四个主要阶段:设计,模拟,综合和布局。

在设计阶段,设计师使用原理图编辑器和其他工具来设计电路。

在模拟阶段,设计师将电路模型装入电路模拟器中,并进行仿真以验证电路的功能和性能。

在综合阶段,设计师使用综合工具将电路转换为特定的逻辑网表文件。

在布局阶段,设计

人员使用布局编辑器来设置电路的物理布局。

最后,我们讨论了EDA技术的优缺点。

EDA技术的主要优点是提高电路设计的效率和

准确性,并减少了设计和制造的成本和时间。

然而,EDA技术也存在一些缺点,例如,设

计人员需要具备高水平的技术和知识,否则可能出现算法错误或设计缺陷。

综上所述,EDA技术在现代电子设备设计和制造中起着非常重要的作用,技术的发展

将会极大程度上促进电子设备的设计和制造的进步和发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

盐城师范学院物理科学与电子技术学院 09(5)班课程名称 EDA技术基础教程姓名:夏天学号 09223459 考核方式:考查得分EDA技术的应用(题目自拟,黑体小三居中)一、简述设计电路说明电路的作用和本论文所做的工作。

二、原理图的设计1.说明电路图中所用的元器件;2.说明原理图的规划及其截图;图1 原理图三、PCB的设计说明PCB设计的注意事项及其结果图。

Pcb设计的注意事项:原理图设计是前期准备工作,经常见到初学者为了省事直接就去画PCB板了,这样将得不偿失,对简单的板子,如果熟练流程,不妨可以跳过。

但是对于初学者一定要按流程来,这样一方面可以养成良好的习惯,另一方面对复杂的电路也只有这样才能避免出错。

在画原理图时,层次设计时要注意各个文件最后要连接为一个整体,这同样对以后的工作有重要意义。

由于,软件的差别有些软件会出现看似相连实际未连(电气性能上)的情况。

如果不用相关检测工具检测,万一出了问题,等板子做好了才发现就晚了。

因此一再强调按顺序来做的重要性,希望引起大家的注意。

原理图是根据设计的项目来的,只要电性连接正确没什么好说的。

下面我们重点讨论一下具体的制板程序中的问题。

l、制作物理边框封闭的物理边框对以后的元件布局、走线来说是个基本平台,也对自动布局起着约束作用,否则,从原理图过来的元件会不知所措的。

但这里一定要注意精确,否则以后出现安装问题麻烦可就大了。

还有就是拐角地方最好用圆弧,一方面可以避免尖角划伤工人,同时又可以减轻应力作用。

以前我的一个产品老是在运输过程中有个别机器出现面壳PCB板断裂的情况,改用圆弧后就好了。

2、元件和网络的引入把元件和网络引人画好的边框中应该很简单,但是这里往往会出问题,一定要细心地按提示的错误逐个解决,不然后面要费更大的力气。

这里的问题一般来说有以下一些:元件的封装形式找不到,元件网络问题,有未使用的元件或管脚,对照提示这些问题可以很快搞定的。

3、元件的布局元件的布局与走线对产品的寿命、稳定性、电磁兼容都有很大的影响,是应该特别注意的地方。

一般来说应该有以下一些原则:3.l放置顺序先放置与结构有关的固定位置的元器件,如电源插座、指示灯、开关、连接件之类,这些器件放置好后用软件的LOCK功能将其锁定,使之以后不会被误移动。

再放置线路上的特殊元件和大的元器件,如发热元件、变压器、IC等。

最后放置小器件。

3.2注意散热元件布局还要特别注意散热问题。

对于大功率电路,应该将那些发热元件如功率管、变压器等尽量靠边分散布局放置,便于热量散发,不要集中在一个地方,也不要高电容太近以免使电解液过早老化。

4、布线布线原则走线的学问是非常高深的,每人都会有自己的体会,但还是有些通行的原则的。

◆高频数字电路走线细一些、短一些好◆大电流信号、高电压信号与小信号之间应该注意隔离(隔离距离与要承受的耐压有关,通常情况下在2KV时板上要距离2mm,在此之上以比例算还要加大,例如若要承受3KV的耐压测试,则高低压线路之间的距离应在3.5mm以上,许多情况下为避免爬电,还在印制线路板上的高低压之间开槽。

)◆两面板布线时,两面的导线宜相互垂直、斜交、或弯曲走线,避免相互平行,以减小寄生耦合;作为电路的输人及输出用的印制导线应尽量避兔相邻平行,以免发生回授,在这些导线之间最好加接地线。

◆走线拐角尽可能大于90度,杜绝90度以下的拐角,也尽量少用90度拐角◆同是地址线或者数据线,走线长度差异不要太大,否则短线部分要人为走弯线作补偿◆走线尽量走在焊接面,特别是通孔工艺的PCB◆尽量少用过孔、跳线◆单面板焊盘必须要大,焊盘相连的线一定要粗,能放泪滴就放泪滴,一般的单面板厂家质量不会很好,否则对焊接和RE-WORK都会有问题◆大面积敷铜要用网格状的,以防止波焊时板子产生气泡和因为热应力作用而弯曲,但在特殊场合下要考虑GND的流向,大小,不能简单的用铜箔填充了事,而是需要去走线◆元器件和走线不能太靠边放,一般的单面板多为纸质板,受力后容易断裂,如果在边缘连线或放元器件就会受到影响◆必须考虑生产、调试、维修的方便性对模拟电路来说处理地的问题是很重要的,地上产生的噪声往往不便预料,可是一旦产生将会带来极大的麻烦,应该未雨绸缎。

对于功放电路,极微小的地噪声都会因为后级的放大对音质产生明显的影响;在高精度A/D转换电路中,如果地线上有高频分量存在将会产生一定的温漂,影响放大器的工作。

这时可以在板子的4角加退藕电容,一脚和板子上的地连,一脚连到安装孔上去(通过螺钉和机壳连),这样可将此分量虑去,放大器及AD也就稳定了。

另外,电磁兼容问题在目前人们对环保产品倍加关注的情况下显得更加重要了。

一般来说电磁信号的来源有3个:信号源,辐射,传输线。

晶振是常见的一种高频信号源,在功率谱上晶振的各次谐波能量值会明显高出平均值。

可行的做法是控制信号的幅度,晶振外壳接地,对干扰信号进行屏蔽,采用特殊的滤波电路及器件等。

需要特别说明的是蛇形走线,因为应用场合不同其作用也是不同的,在电脑的主板中用在一些时钟信号上,如PCIClk、AGP-Clk,它的作用有两点:1、阻抗匹配2、滤波电感。

对一些重要信号,如INTELHUB架构中的HUBLink,一共13根,频率可达233MHZ,要求必须严格等长,以消除时滞造成的隐患,这时,蛇形走线是唯一的解决办法。

一般来讲,蛇形走线的线距>=2倍的线宽;若在普通PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。

5、调整完善完成布线后,要做的就是对文字、个别元件、走线做些调整以及敷铜(这项工作不宜太早,否则会影响速度,又给布线带来麻烦),同样是为了便于进行生产、调试、维修。

敷铜通常指以大面积的铜箔去填充布线后留下的空白区,可以铺GND的铜箔,也可以铺VCC的铜箔(但这样一旦短路容易烧毁器件,最好接地,除非不得已用来加大电源的导通面积,以承受较大的电流才接VCC)。

包地则通常指用两根地线(TRAC)包住一撮有特殊要求的信号线,防止它被别人干扰或干扰别人。

如果用敷铜代替地线一定要注意整个地是否连通,电流大小、流向与有无特殊要求,以确保减少不必要的失误。

6、检查核对网络有时候会因为误操作或疏忽造成所画的板子的网络关系与原理图不同,这时检察核对是很有必要的。

所以画完以后切不可急于交给制版厂家,应该先做核对,后再进行后续工作。

7、使用仿真功能完成这些工作后,如果时间允许还可以进行软件仿真。

特别是高频数字电路,这样可以提前发现一些问图2 器件自动布局四、电路板布线布线的要求和布线后的PCB图。

图3 全局布线后的PCB图1.布线的要求:布线是整个PCB设计中最重要的工序。

这将直接影响着PCB板的性能好坏。

在PCB的设计过程中,布线一般有这么三种境界的划分:首先是布通,这时PCB设计时的最基本的要求。

如果线路都没布通,搞得到处是飞线,那将是一块不合格的板子,可以说还没入门。

其次是电器性能的满足。

这是衡量一块印刷电路板是否合格的标准。

这是在布通之后,认真调整布线,使其能达到最佳的电器性能。

接着是美观。

假如你的布线布通了,也没有什么影响电器性能的地方,但是一眼看过去杂乱无章的,加上五彩缤纷、花花绿绿的,那就算你的电器性能怎么好,在别人眼里还是垃圾一块。

这样给测试和维修带来极大的不便。

布线要整齐划一,不能纵横交错毫无章法。

这些都要在保证电器性能和满足其他个别要求的情况下实现,否则就是舍本逐末了。

布线时主要按以下原则进行: ①.一般情况下,首先应对电源线和地线进行布线,以保证电路板的电气性能。

在条件允许的范围内,尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最细宽度可达0.05~0.07mm,电源线一般为1.2~2.5mm。

对数字电路的PCB可用宽的地导线组成一个回路,即构成一个地网来使用(模拟电路的地则不能这样使用) ②.预先对要求比较严格的线(如高频线)进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

③.振荡器外壳接地,时钟线要尽量短,且不能引得到处都是。

时钟振荡电路下面、特殊高速逻辑电路部分要加大地的面积,而不应该走其它信号线,以使周围电场趋近于零; ④.尽可能采用45o的折线布线,不可使用90o 折线,以减小高频信号的辐射;(要求高的线还要用双弧线) ⑤.任何信号线都不要形成环路,如不可避免,环路应尽量小;信号线的过孔要尽量少; ⑥.关键的线尽量短而粗,并在两边加上保护地。

⑦.通过扁平电缆传送敏感信号和噪声场带信号时,要用“地线-信号-地线”的方式引出。

⑧.关键信号应预留测试点,以方便生产和维修检测用 ⑨.原理图布线完成后,应对布线进行优化;同时,经初步网络检查和DRC检查无误后,对未布线区域进行地线填充,用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。

或是做成多层板,电源,地线各占用一层。

——PCB布线工艺要求 ①.线 一般情况下,信号线宽为0.3mm(12mil),电源线宽为0.77mm(30mil)或1.27mm(50mil);线与 线之间和线与焊盘之间的距离大于等于0.33mm(13mil),实际应用中,条件允许时应考虑加大距离;布线密度较高时,可考虑(但不建议)采用IC脚间走两根线,线的宽度为0.254mm(10mil),线间距不小于0.254mm(10mil)。

特殊情况下,当器件管脚较密,宽度较窄时,可按适当减小线宽和线间距。

②.焊盘(PAD) 焊盘(PAD)与过渡孔(VIA)的基本要求是:盘的直径比孔的直径要大于0.6mm;例如,通用插脚式电阻、电容和集成电路等,采用盘/孔尺寸 1.6mm/0.8mm(63mil/32mil),插座、插针和二极管1N4007等,采用 1.8mm/1.0mm (71mil/39mil)。

实际应用中,应根据实际元件的尺寸来定,有条件时,可适当加大焊盘尺寸;PCB板上设计的元件安装孔径应比元件管脚的实际尺寸大0.2~0.4mm左右。

③.过孔(VIA) 一般为1.27mm/0.7mm(50mil/28mil); 当布线密度较高时,过孔尺寸可适当减小,但不宜过小,可考虑采用1.0mm/0.6mm(40mil/24mil)。

④.焊盘、线、过孔的间距要求 PADandVIA:≥0.3mm(12mil) PADandPAD:≥0.3mm (12mil) PADandTRACK:≥0.3mm(12mil) TRACKandTRACK:≥0.3mm (12mil) 密度较高时: PADandVIA:≥0.254mm(10mil) PADandPAD:≥0.254mm(10mil) PADandTRACK:≥0.254mm(10mil) TRACKandTRACK:≥0.254mm(10mil) 2.布线优化和丝印。