MIPS内存管理单元的设计与实现

mips和x86区别

mips和x86区别MIPS和PowerPC是RISC构架,基于Load/Store的内存访问方式,长度固定的指令,流水线结构。

而MIPS是教科书似的RISC构架,使它和其它的RISC构架显得很不同,比如delay slot(对新手来说相当的难),cache管理,TLB管理都需要很繁琐的软件配合,相对来说PowerPC更偏向于向实际应用倾斜,比如有功能强大也让人头痛的移位指令、旋转指令。

而X86,曾经是CISC的典型,不过现在只是RISC的内核披了件CISC的外衣,从Pentium开始,CISC指令在内部被解码成几条RISC指令,即所谓的uOps,然后通过处理器调度机制将指令分配给RISC内核进行。

X86不同于RISC的地方:硬件管理的TLB,长短不一且执行时间也长短不一的指令。

PC服务器与小型机的区别在英文里这两位都叫server(服务器),小型机是国内的习惯称呼。

pc服务器则主要指基于intel处理器的架构,是一个通用开放的系统。

而不同品牌的小型机架构大不相同,使用risc、mips处理器,像美国sun、日本fujitsu等公司的小型机是基于sparc处理器架构,而美国hp公司的则是基于pa-risc架构,compaq公司是alpha架构,ibm和sgi等的也都各不相同;i/o总线也不相同,fujitsu是pci,sun是sbus,等等,这就意味着各公司小型机机器上的插卡,如网卡、显示卡、scsi卡等可能也是专用的;操作系统一般是基于unix 的,像sun、fujitsu是用sun solaris,hp是用hp-unix,ibm是aix,等等,所以小型机是封闭专用的计算机系统。

使用小型机的用户一般是看中unix操作系统的安全性、可靠性和专用服务器的高速运算能力,虽然小型机的价格是pc服务器的好几倍。

pc服务器一般用的操作系统是安全性、可靠性稍差的windows2000/windows nt4。

MIPS存储管理

MIPS存储管理一.虚拟地址空间地址空间的最大长度与实际可用的物理内存数量无关,因此被称为虚拟地址空间(Virtual Address Space)。

这个虚拟地址空间的大小是由计算机的硬件平台决定的,具体来说是由CPU的位数决定的。

硬件决定了地址空间的最大理论上限,即硬件的寻址空间大小,比如主流的32位处理器(IA32,MIPS,ARM)等能寻址2^32B,即4GB的大小的地址空间(0~0xFFFF FFFF)。

Linux将虚拟地址空间划分为两个部分:内核空间和用户空间。

系统中每个用户进程都有自己的虚拟地址范围,从0到TASK_SIZE。

通常取TASK_SIZE=0xC000 0000,即4GB的底部3GB(0x0000 0000 ~ 0xBFFF FFFF)留给用户空间的进程使用的,顶部1GB(0xC000 0000 ~ 0xFFFF FFFF)留给内核使用。

对于Windows操作系统来说,它的进程虚拟地址空间划分是操作系统占用2GB,用户进程只剩下2GB。

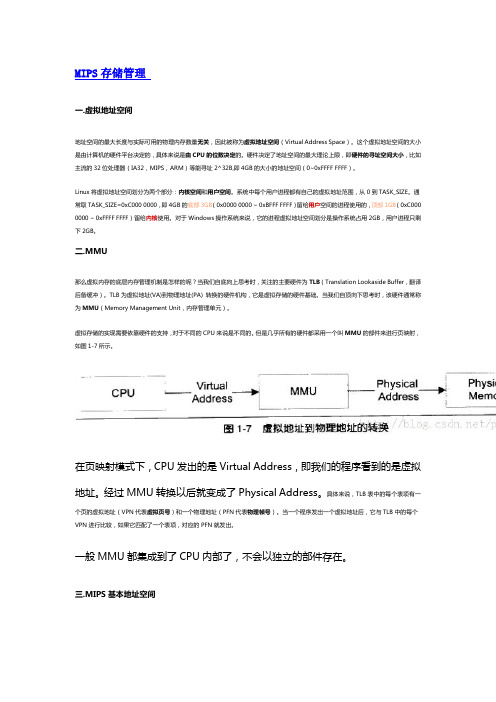

二.MMU那么虚拟内存的底层内存管理机制是怎样的呢?当我们自底向上思考时,关注的主要硬件为TLB(Translation Lookaside Buffer,翻译后备缓冲)。

TLB为虚拟地址(VA)到物理地址(PA) 转换的硬件机构,它是虚拟存储的硬件基础。

当我们自顶向下思考时,该硬件通常称为MMU(Memory Management Unit,内存管理单元)。

虚拟存储的实现需要依靠硬件的支持,对于不同的CPU来说是不同的。

但是几乎所有的硬件都采用一个叫MMU的部件来进行页映射,如图1-7所示。

在页映射模式下,CPU发出的是Virtual Address,即我们的程序看到的是虚拟地址。

经过MMU转换以后就变成了Physical Address。

具体来说,TLB表中的每个表项有一个页的虚拟地址(VPN代表虚拟页号)和一个物理地址(PFN代表物理帧号)。

华中科技大学HUST类MIPS单周期微处理器设计实验报告

类MIPS单周期微处理器设计实验报告专业:班级:学号:姓名:一、微处理器各模块设计各模块的框图结构如上图所示。

由图可知,该处理器包含指令存储器、数据存储器、寄存器组、ALU单元、符号数扩张、控制器、ALU控制译码以及多路复用器等。

图中还忽略了一个单元:时钟信号产生器,而且以上各个部件必须在时钟信号的控制下协调工作。

1.指令存储器的设计指令寄存器为ROM类型的存储器,为单一输出指令的存储器。

因此其对外的接口为clk、存储器地址输入信号(指令指针)以及数据输出信号(指令)。

(1)在IP wizard 中配置ROM,分配128个字的存储空间,字长为32位宽。

(2)选择输入具有地址寄存功能,只有当时钟上升沿有效时,才进行数据的输出。

(3)配置ROM内存空间的初始化COE文件。

最后单击Generate按钮生成IROM模块。

2.数据存储器的设计数据存储器为RAM类型的存储器,并且需要独立的读写控制信号。

因此其对外的接口输入信号为clk、we、datain、addr;输出信号为dataout。

数据存储器基本建立过程同ROM的建立。

3.寄存器组设计寄存器组是指令操作的主要对象,MIPS中一共有32个32位寄存器。

在指令的操作过程中需要区分Rs、Rt、Rd的地址和数据,并且Rd的数据只有在寄存器写信号有效时才能写入,因此该模块的输入为clk、RegWriteAddr、RegWriteData、RegWriteEn、RsAddr、RtAddr、reset;输出信号为RsData、RtData。

由于$0一直输出0,因此当RsAddr、RtAddr为0时,RsData以及RtData 必须输出0,否则输出相应地址寄存器的值。

另外,当RegWriteEn有效时,数据应该写入RegWriteAddr寄存器。

并且每次复位时所有寄存器都清零。

代码如下:module regFile(input clk,input reset,input [31:0] regWriteData,input [4:0] regWriteAddr,input regWriteEn,output [31:0] RsData,output [31:0] RtData,input [4:0] RsAddr,input [4:0] RtAddr);reg[31:0] regs[0:31];assign RsData = (RsAddr == 5'b0)?32'b0:regs[RsAddr];assign RtData = (RtAddr == 5'b0)?32'b0:regs[RtAddr];integer i;always @(posedge clk)beginif(!reset)beginif(regWriteEn==1)beginregs[regWriteAddr]=regWriteData;endendelsebeginfor(i=0;i<31;i=i+1)regs[i]=0;regs[31]=32'hffffffff;endendendmodule4.ALU设计在这个简单的MIPS指令集中,微处理器支持add、sub、and、or、slt运算指令,需要利用ALU单元实现运算,同时数据存储指令sw、lw也需要ALU单元计算存储器地址,条件跳转指令beq需要ALU来比较两个寄存器是否相等。

OpenMIPS教学版讲解

流水线架构

流水线架构是现代处理器中常见的一种架构,通过将指令执行过程划分为多个阶段, 实现并行处理,提高处理器的执行效率。

OpenMIPS教学版的流水线架构分为取指、解码、执行、访存和写回五个阶段,每 个阶段都有相应的硬件单元进行支持,确保指令执行的快速和准确。

流水线架构能够有效地提高处理器的吞吐量,同时使得处理器更加灵活,能够适应 不同的应用场景。

算平台上实现更快速的计算和推理。

嵌入式系统应用

03

OpenMIPS教学版可以应用于嵌入式系统中,为人工智能传感

器和设备提供强大的计算能力。

OpenMIPS在物联网领域的应用

实时数据处理

OpenMIPS教学版适用于物联网设备中的实时数据处理,如传 感器数据的采集、分析和处理。

低功耗设计

针对物联网设备的低功耗要求,OpenMIPS教学版可以进行优 化,降低设备能耗,延长电池寿命。

实验案例选择

选择具有代表性的实验案 例,如简单的加法器、乘 法器等。

实验案例解析

对每个实验案例进行详细 解析,包括输入输出、算 法实现等。

实验案例实现

根据解析结果,在 OpenMIPS教学版上实现 相应的算法。

实验结果分析

实验结果验证

通过实际运行和测试,验证实验结果的正确性。

结果分析

对实验结果进行分析,包括性能指标、优化空间 等。

数据中心优化

通过OpenMIPS教学版的优化,可以提高数据中心的处理能力和能效, 降低运营成本。

THANKS FOR WATCHING

感谢您的观看

C语言与汇编的交互

在OpenMIPS教学版中,可以使用内嵌汇编的方式将C语言与汇编 语言进行交互,实现更高效的代码实现。

MIPS指令多周期CPU设计

– MEMread, IRwrite, PCwrite

译码/取操作数 – ALUsrcA=0, ALUsrcB=11,ALUop=00 执行运算 – ALUsrcA=0, ALUsrcB=00,ALUop=00

写回寄存器

– RegDST=1 RegWrite MemtoReg = 0

MIPS的 LW 指令 的执行过程

A 寄 存 器

1

A A L U

Z

PC

0 1

存 A 储 D 器

B 寄 存 器

4

1 0 2 3

B

R

结 果 寄 存 器

DR

1 0

扩展

Clock

Immediate

左移2位

MIPS的 ADD 指令 的执行过程

取指 周期: 执行 周期:

IR←MEM[PC]

PC ←PC+4 C ← A+B

WritePC IODR WriteMEM WriteIR MEMtoREG SE REGds WriteREG ALUsrcA

0

0

指 令 内 容 IR

rs rt

rd

0 1

N1 寄 Q1 存 N2 器 堆 ND DI Q2

A 寄 存 器

1

A A L U

Z

PC

0 1

存 A 储 D 器

B 寄 存 器

4

1 0 2 3

B

R

结 果 寄 存 器

DR

1 0

Immediate

Clock

扩展

左移2位

存储器存指令和数据。 读指令时由 PC 提供地址,读出的指令保存到 IR; 读写数据时由结果寄存器提供地址,读操作的读出数据保存到 DR; 写操作的写入数据由 B寄存器给出。

MIPS

作者点评:MIPS技术公司则是一家设计制造高性能、高档次及嵌入式32位和64位处理器的厂商。在通用方面,MIPS R系列微处理器用于构建SGI的高性能工作站、服务器和超级计算机系统。在嵌入式方面,MIPS K系列微处理器是目前仅次于ARM的用得最多的处理器之一(1999年以前MIPS是世界上用得最多的处理器),其应用领域覆盖游戏机、路由器、激光打印机、掌上电脑等各个方面。

MIPS的系统结构及设计理念比较先进,其指令系统经过通用处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV到MIPS V,嵌入式指令体系MIPS16、MIPS32到MIPS64的发展已经十分成熟。在设计理念上MIPS强调软硬件协同提高性能,同时简化硬件设计。

中国龙芯2和前代产品采用的都是64位MIPS指令架构,它与大家平常所知道的X86指令架构互不兼容,MIPS指令架构由MIPS公司所创,属于RISC体系。过去,MIPS架构的产品多见于工作站领域,索尼PS2游戏机所用的“Emotion Engine”也采用MIPS指令,这些MIPS处理器的性能都非常强劲,而龙芯2也属于这个阵营,在软件方面与上述产品完全兼容。

MIPS公司设计RISC处理器始于二十世纪八十年代初,1986年推出R2000处理器,1988年推R3000处理器,1991年推出第一款64位商用微处器R4000。之后又陆续推出R8000(于1994年)、R10000(于1996年)和R12000(于1997年)等型号。

MIPS课程设计

MIPS课程设计一、课程目标知识目标:1. 理解MIPS汇编语言的基本概念,掌握其指令集和编程规则。

2. 学会使用MIPS汇编语言进行程序设计,包括顺序、分支和循环结构。

3. 了解计算机内部存储器组织和寻址方式,理解寄存器的作用和用法。

技能目标:1. 能够编写简单的MIPS汇编程序,实现基本算法和逻辑控制。

2. 能够使用模拟器和调试工具进行汇编程序的编译、运行和调试。

3. 能够分析MIPS汇编程序的性能,并进行简单的优化。

情感态度价值观目标:1. 培养学生对计算机硬件和底层编程的兴趣,激发探索精神。

2. 培养学生良好的编程习惯,注重代码规范和逻辑清晰。

3. 增强学生的团队合作意识,提高沟通与协作能力。

分析课程性质、学生特点和教学要求:本课程为计算机科学与技术专业的核心课程,以MIPS汇编语言为载体,帮助学生深入理解计算机硬件和软件的交互原理。

学生具备一定的编程基础,但大部分学生对硬件层面了解较少。

教学要求注重理论与实践相结合,强调动手实践和问题解决能力。

根据以上分析,课程目标分解为以下具体学习成果:1. 学生能够独立编写并运行简单的MIPS汇编程序。

2. 学生能够通过调试工具分析汇编程序的执行过程,找出并修复错误。

3. 学生能够以小组形式完成一个综合性的汇编程序项目,展示对知识点的掌握和团队协作能力。

二、教学内容1. 引言:计算机硬件与汇编语言概述,介绍MIPS汇编语言的发展和应用场景。

- 章节关联:课本第1章 计算机硬件基础2. MIPS汇编语言基础:- 指令集与寄存器- 数据表示与存储器寻址- 章节关联:课本第2章 MIPS汇编语言基础3. MIPS汇编程序设计:- 顺序程序设计- 分支程序设计- 循环程序设计- 章节关联:课本第3章 程序设计基础4. MIPS汇编程序调试与优化:- 使用模拟器和调试工具- 性能分析- 简单优化技巧- 章节关联:课本第4章 程序调试与优化5. 综合项目实践:- 小组项目任务分配与协作- 项目需求分析、设计与实现- 项目展示与评价- 章节关联:课本第5章 综合项目实践教学内容安排与进度:第1周:引言,计算机硬件与汇编语言概述第2-3周:MIPS汇编语言基础第4-5周:MIPS汇编程序设计第6周:MIPS汇编程序调试与优化第7-8周:综合项目实践三、教学方法本课程采用以下多样化的教学方法,旨在激发学生的学习兴趣,提高主动性和实践能力:1. 讲授法:- 用于讲解MIPS汇编语言的基本概念、指令集、编程规则等理论知识。

处理器结构与操作系统相关(MIPS为例)

无效虚地址(BadVaddr) 无效虚地址( )

保存引发异常的地址( 异常, 之外, 保存引发异常的地址(MMU异常,用户访问 异常 用户访问kuseg之外, 之外 地址未对齐)。 地址未对齐)。

- 11 -

CPU控制寄存器

Config Register

CM: 设为 表示主设备 检查器 设为1表示主设备 表示主设备/检查器 EC: 时钟分频 EP: 数据传输模式 SB: 片外二级缓存块的大小 SS: 控制片外二级缓存块指令和数据空间统一还是分立 SC: 二级缓存使能 SM: 多处理器缓存一致性配置 BE: CPU尾端 尾端 EM: 数据检验模式,1:ECC;0:奇偶校验 数据检验模式, : ; : IC/DC: 一级指令 数据缓存大小 一级指令/数据缓存大小

- 26 -

异常处理

软件中实现中断优先级

1. 软件中每个中断源都属于某个优先等级(IPL); 软件中每个中断源都属于某个优先等级( ); 2. CPU运行在最低优先级,任何中断允许; 运行在最低优先级, 运行在最低优先级 任何中断允许; 3. CPU运行在最高优先级,任何中断禁止; 运行在最高优先级, 运行在最高优先级 任何中断禁止; 4. 任意 任意IPL上,分配到该级和更低优先级的中断被禁止,而 上 分配到该级和更低优先级的中断被禁止, 更高优先级的使能,同一级的不同中断先来先服务; 更高优先级的使能,同一级的不同中断先来先服务; 5. IPL和被运行代码相关:任意一段代码以固定 和被运行代码相关: 执行; 和被运行代码相关 任意一段代码以固定IPL执行; 执行 6. 如果不在最低优先级并且没有更高优先级中断活跃时,中 如果不在最低优先级并且没有更高优先级中断活跃时, 断返回被中断的代码,如果在最低优先级可能会进行任 断返回被中断的代码, 务调度来实现CPU共享。 共享。 务调度来实现 共享

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

p o e s r r ei e nF r c s o e v rf d o PGA o r u n n n x a d t e h r wa ec s b u 2 l g c ae . a i b a dr n i g Li u n a d r o ti a o t3 K i a g t s h s o l

LU h -ig YOU i iHAN u ZENG a -a g S it , n Ka- , d J n, Xioy n

( S C & S s m tt Ke a , u a ies y S a g a 2 1 0 , h n ) A I y t Sae y b F d n e L Unv r t, h n h i 0 2 3 C ia i

第 3 卷 第 2 期 6 1

V .6 o1 3

No 2 00 1

No m be 1 ve r 20 0

Comput rEng n e i e i e rng

・ 发研 究与设 计技术 ・ 开

文章 编号: 0 32( l) —o 0 文献标识 A 10_ 48 0o 1_ 7— 2 2 2 2 码:

[ y r s mo Maa e n iMMU)Ta s t nL o -s eB f r L )MISpoesr Ke d lMe  ̄ wo n gme t t Un ( ; rnl i o kai uf ( B ; P rcso ao d eT

1 概述

内存管理 单元( MMU) 是处理 器支持操 作系统 高效运行 的基础 ,与软件 内存管理模块…相结合完成了虚拟地址到物 理地址的转换 。同时 ,MMU 能够对处理器发出的地址进行

3 个模块粘合起来 ,使访存操作能安全高效地进行。

对于一次普通 的访 问内存操作 ,处理器发出的虚拟地址 首先会经过主控制器判断 ,如果该地址属于静态地址 映射范 围,则根据固定的映射算法把地址转换为物理地址并交 由总 线接 1 3以处理具体 的数据读写。如果该地址属于 动态地址范 围映射 ,则控制器会启 动相应 的 T B 工作来查 找地址映射 L

地址空间采取 了静态和动态映射 相结合 的方式 ,其 中动态映 射 以地址后备转换表( L ) T B 为基础 , 硬件设计上采甩与处理器 流水线平行对齐 的流水线结构 。为了加快地址转换 ,在处理 器指令端 口和数据端 1分别设计 了 IL 3 T B和 D L 。 T B 与总线访 问接 口的连接 ,采用简化的 A A协议。 MB

中田 分类号: P1. T 31 2 5

MI S内存 管理单元 的设计 与实现 P

卢仕 听,尤凯迪 ,韩 军 ,曾晓洋

( 复旦大学专用集成电路与系统 国家重点实验 室,上海 2 10 ) 0 23 摘 要 :设计 MI S 24 c P 3 k 处理器 内存管理单元( MMU ,该模块对处理器地址进行合法性检查 ,并按照不同的地址 空间对虚拟地址进行静 ) 态或动态映射 。 在硬件上采 用三级流水线方式实现 J L , T B 并为处理器指令端 口和数据端 口设计相应的快表 以提高 T B的查询速 度。 L MMU

。

[ src]Me  ̄ Ma ae n iMMU) i ae nMI S 24cpo esri dsge . h d l c ek ea desf m e Abta t mo n g met t Un ( whc i b sdo P 3 k rcso eind T emo ue hc st d rs r t hs s h o h

与总线接 口模块的时序采用简化的 AMB A协议 ,与处理器进行联合调试并运行 Ln x操作系统 ,同时在 功能上通过 F GA验证。该模块 iu P 经过 DC综合后,面积约为 3 K等效逻辑 门。 2

关健词 :内存管理 单 ;地址转换 后备表 ;MIS 元 P 处理器

De i n a d I p e e t t n 0 e o yM a a e e t sg n m l m n a i f o M m r n g m n i n M I Un t PS 0

其 中 ,T B 又分 为 J L L T B、IL 和 D L TB T B。MMU 接 受 处 理

器访存请求时 ,根据虚拟地址和处理器当前的工作模式进行

地址转换 。 如果访 问合法 , 它将把得到的物理地址送给 cc e ah 或者是总线接 1进行数据读写; 3 否则 , 它会触发处理器异常 。

MMU 在 此处于 核心地位 ,它把 处理器 、缓存、总 线接 E l

合法性检验 , 在硬件上提供 了内存访问授权控制。由于 MMU

与处理器体 系结构高度相关,因此在 不同的处理器 下内存管

理 机 制 区别 很 大 。 根 据 MIS 24 c 1 理器 对 内存 管理 的规 范 ,针 对 不 同 P 3 k [处 2

p o e s rc r , n rn ltsi t hy ia d rs ttc l rd n mial. B stec r fdy a c lma piga d i mpe ntd b sn r c so oe a d ta sae t O p sc la d essaial o y a c ly TL i h oeo n mia p n n si lme e yu ig y