寄存器组的设计与实现预习

寄存器和锁存器设计实验报告总结

寄存器和锁存器设计实验报告总结一、实验内容学习寄存器和锁存器的基本概念、分类以及工作原理;利用基本电路元件搭建寄存器和锁存器的电路结构;进行实验验证,并分析实验结果。

二、实验步骤确定实验目的和要求;学习寄存器和锁存器的基本概念、分类以及工作原理;根据实验要求,利用基本电路元件搭建寄存器和锁存器的电路结构;对搭建好的电路进行实验验证;分析实验结果并撰写实验报告。

三、实验原理寄存器是一种用于存储数据的器件,它可以暂时存储数据并在需要时将其取出使用。

根据存储方式的不同,寄存器可以分为随机访问寄存器(RAM)和只读存储器(ROM)等类型。

其中,RAM是一种能够被多次读取的存储器件,而ROM则是一种只能被读取一次的存储器件。

锁存器是一种能够保持输入信号不变的器件。

当输入信号为高电平时,锁存器的输出端也会变为高电平;当输入信号为低电平时,锁存器的输出端也会变为低电平。

锁存器的特点是能够将输入信号暂时保存下来,以便后续使用。

四、实验过程及结果分析在搭建寄存器电路时,我们采用了与门、或门、非门等基本逻辑门电路来实现寄存器的读写功能。

具体来说,我们将一个触发器作为主控单元,通过控制触发器的输入端来实现数据的读写操作。

同时,为了保证数据的安全性,我们在主控单元周围添加了一个锁存器来进行数据的保护。

在搭建锁存器电路时,我们同样采用了与门、或门、非门等基本逻辑门电路来实现锁存器的开关功能。

具体来说,我们将一个触发器作为主控单元,通过控制触发器的输入端来实现数据的开关操作。

同时,为了保证数据的稳定性,我们在主控单元周围添加了一个与门来实现数据的同步更新。

五、结论与展望通过本次实验的学习与实践,我们深入了解了寄存器和锁存器的基本原理和应用场景。

同时,我们也掌握了一些基本的电路设计和调试技巧。

在未来的学习和工作中,我们将继续深入研究计算机组成原理的相关知识和技术,不断提升自己的实践能力和创新能力。

青岛理工大学通用寄存器组设计

青岛理工大学实验报告实验课程:计算机组成原理I Array实验日期:2014年10月15日,交报告日期:2014年11月日,成绩:实验地点:现代教育技术中心305(计算机实验室)计算机工程学院,计算机科学与技术专业,班级:计算122班实验指导教师:龚玉玺批阅教师:龚玉玺一、实验课题一、主要元件设计1.16位寄存器功能要求:同步并行置数,异步复位(清零),三态输出,片选信号,读/写控制。

2.地址译码器功能要求:3-8译码器二、顶层设计用层次结构设计的方法设计一个通用寄存器组。

包括8个16位寄存器,1个地址译码器等元件。

功能要求:每个寄存器能够同步并行置数,异步复位(清零),三态输出。

每个都可以(用地址)独立访问三、仿真设计仿真波形数据,要考虑到所有可能的情况。

在实验报告中必须清楚说明仿真波形数据是怎样设计的。

四、深入的课题①上面设计的通用寄存器组,每次只能访问一个寄存器。

如果想同时访问两个寄存器,应该怎样设计?②16位的寄存器每次读/写都是一个16位字,如果需要写入的是8位的字,即将8位的字写到16位寄存器的高8位或低8位(例如,16位寄存器A由AH和AL两个8位的寄存器组成),读出时,可一次读16位。

应该怎样设计二、逻辑设计端口说明:A(1-3):输入信号 S(1-3):使能端 Y(0-7):输出端口功能表:321逻辑函数:S A A A Y ⋅⋅⋅=)(0120,S A A A Y ⋅⋅⋅=)(0121,S A A A Y ⋅⋅⋅=)(0122 S A A A Y ⋅⋅⋅=)(0123,S A A A Y ⋅⋅⋅=)(0124,S A A A Y ⋅⋅⋅=)(0125 S A A A Y ⋅⋅⋅=)(0126,S A A A Y ⋅⋅⋅=)(0127十六位寄存器系统框图端口说明: A(0-15):输入 D(0-15):输出 Clk:时钟信号r,chip,z:分别是异步清零信号,片选信号,三态输出 rw,:分别是读写控制信号功能表:十六位寄存器组系统框图端口说明: AI(0-3):给译码器的输入z,r,clk,rw:分别是三态输出,异步置零,时钟,读写控制 A(0-15):数据输入 D(0-15):数据输出十六位寄存器逻辑图1、3-8译码器:--Decodelibrary ieee;use ieee.std_logic_1164.all;entity decode isport(s1,s2,s3: in std_logic;--使能端A : in std_logic_vector(2 downto 0);--输入Y : out std_logic_vector(7 downto 0)--输出);end decode;architecture de_behave of decode issignal s: std_logic;begins<=s1 and (not s2) and (not s3);Y(0)<=not( ((not A(2)) and (not A(1)) and (not A(0))) and s );Y(1)<=not( ((not A(2)) and (not A(1)) and A(0)) and s);Y(2)<=not( ((not A(2)) and A(1) and (not A(0))) and s );Y(3)<=not( (not A(2) and A(1) and A(0)) and s);Y(4)<=not( (A(2) and (not A(1)) and (not A(0))) and s);Y(5)<=not( (A(2) and (not A(1)) and A(0)) and s);Y(6)<=not( (A(2) and A(1) and (not A(0))) and s);Y(7)<=not( (A(2) and A(1) and A(0)) and s);end de_behave;2、十六位寄存器:--十六位寄存器library ieee;use ieee.std_logic_1164.all;entity Sixteen_Register isport( --clk:时钟信号(上升沿有效)--r:异步清零信号(高电平有效)--chip:片选信号(低电平有效)--z:三态门(z=1三态门打开)--load:同步置数信号--rw:读写控制信号rw = 1 is Read ,or is Writeclk,r,chip,z,rw : in std_logic ;a : in std_logic_vector(15 downto 0);d : out std_logic_vector(15 downto 0));end Sixteen_Register;architecture behave of Sixteen_Register issignal sign : std_logic_vector(15 downto 0);--中间信号beginprocess(clk,r,chip,z,rw)beginif chip = '0' then --片选信号有效时候if r = '1' then --异步置零sign <= (others=>'0');elsif rising_edge(clk) then --clk上升沿if rw = '1' thend <= sign;else --时钟上升沿,写sign<=a;end if;if z = '0' thend<=(others=>'Z');end if;end if;elsed<=(others=>'Z');end if;end process;end behave;3、十六位寄存器组--通用寄存器组library ieee;use ieee.std_logic_1164.all;entity Sixteen_Register_group isport(--A是选择信号,端口和3-8译码器相连--clk是时钟信号--load是同步置数控制端--rw是读写控制--r异步清零--load:同步置数信号--z三态门--a输入--d输出s1,s2,s3 : in std_logic;AI : in std_logic_vector(2 downto 0);clk,rw,r,z: in std_logic;a : in std_logic_vector(15 downto 0);d : out std_logic_vector(15 downto 0));end Sixteen_Register_Group;architecture struct of Sixteen_Register_Group issignal Y : std_logic_vector(7 downto 0);--暂时存储3-8译码器产生的信号component Sixteen_Register --十六位寄存器元件说明port( --clk:时钟信号(上升沿有效)--r:异步清零信号(高电平有效)--chip:片选信号(低电平有效)--z:三态门(z=1三态门打开)--load:同步置数信号--rw:读写控制信号rw = 1 is Read ,or is Writeclk,r,chip,z,rw : in std_logic ;a : in std_logic_vector(15 downto 0);d : out std_logic_vector(15 downto 0));end component;component decode --3-8译码器元件说明port(s1,s2,s3: in std_logic;--使能端A : in std_logic_vector(2 downto 0);--输入Y : out std_logic_vector(7 downto 0)--输出);end component;begin--3-8译码器的一次例化TEdecode: decode port map(A=>AI , Y=>Y,s1=>s1,s2=>s2,s3=>s3);--十六位寄存器的例化G0:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(0),a=>a,d=>d);G1:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(1),a=>a,d=>d);G2:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(2),a=>a,d=>d);G3:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(3),a=>a,d=>d);G4:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(4),a=>a,d=>d);G5:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(5),a=>a,d=>d);G6:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(6),a=>a,d=>d);G7:Sixteen_Register port map(clk=>clk,r=>r,z=>z,rw=>rw,chip=>Y(7),a=>a,d=>d);end struct;四、仿真设计3-8译码器仿真设计:从它的功能表可以知道输入的数据是有限的且只有八组。

移位寄存器的设计与实现

移位寄存器的设计与实现移位寄存器(Shift Register)是一种特殊的寄存器,用于在数字电路中将数据按位移动的操作。

它可以将数据向左或向右进行平行移位,并且可以用来实现各种电路功能,例如串行-并行数据转换、频率分频或倍频、数据缓存等。

本文将从移位寄存器的基本结构、设计要点、实现方法等方面进行详细介绍。

移位寄存器的基本结构通常由多个触发器(Flip-flop)组成,每个触发器负责存储一个位的数据。

根据移位方向的不同,可以将移位寄存器分为向左移位(左移寄存器)和向右移位(右移寄存器)两种类型。

其中,向左移位寄存器采用最左边的触发器接收数据,然后依次向右边的触发器传递;向右移位寄存器则采用最右边的触发器接收数据,然后依次向左边的触发器传递。

在设计移位寄存器时,需考虑以下几个要点:1.触发器的选择:常用的触发器包括D触发器、JK触发器等,具体选择哪种触发器取决于设计的功能需求和性能要求。

同时还需要考虑触发器的时钟信号和复位信号。

2.位移方向的确定:根据具体的应用需求,确定是向左移位还是向右移位,以及移位的次数。

3.并行加载和并行输出:除了进行移位操作,移位寄存器通常还需要支持同时将多个位数据加载进来(并行加载)或者并行输出到外部设备。

4.移位寄存器的宽度:决定了可以存储的位数,根据具体应用需求选择合适的宽度。

5.时序控制和控制信号:移位寄存器的正常工作需要时钟信号和其他控制信号,例如复位信号、使能信号等。

通过以上的设计要点,可以实现不同功能的移位寄存器。

例如,通过多次移位操作可以实现数据的频率分频或倍频,具体实现方式是将时钟信号输入到移位寄存器,并利用移位寄存器的特性进行数据的整除或整倍处理。

此外,通过适当地选择触发器和控制信号,还可以实现串行-并行数据转换的功能。

即将串行数据输入到移位寄存器中,通过控制信号使数据在移位寄存器中进行移位,并经过并行输出接口输出到外部设备。

最常见的实现方法是使用门电路(AND、OR、NOT门)和触发器电路的组合。

寄存器组的设计与实现

寄存器组的设计与实现第______ _________组成员___ ____ ____实验日期___ _____ _____实验报告完成日期___________一、实验目的1、学习掌握Quartus软件的基本操作;2、理解寄存器组的工作原理和过程;3、设计出寄存机组并对设计的正确性进行验证;二、实验内容1、设计出功能完善的寄存器组,并对设计的正确性进行验证。

要求如下:(1)用图形方式设计出寄存器组的电路原理图(2)测试波形时用时序仿真实现,先将不同的数据连续写入4个寄存器后,再分别读出(3)将设计文档封装成器件符号。

(4)数据的宽度最好是16位2、能移位的暂存器实验,具体要求如下:(1)用图形方式设计出能移位的暂存器电路原理图,分别实现左移、逻辑右移和算术右移。

(2)测试波形时要用时序仿真实现,测试数据不要全为0也不要全为1,算术右移的测试数据要求为负数(即符号位为1)(3)将设计文档封装成器件符号。

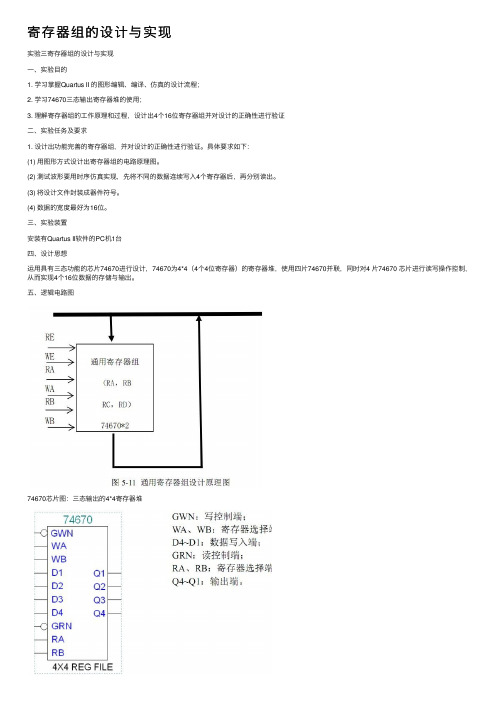

(4)数据的宽度最好是16位三、能完善的寄存器组设计思想1、对于寄存器组设计思路利用具有三态功能的寄存器堆74670芯片进行设计,根据实验要求,需要设计16位的存储器组,则需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行读写操作控制,封装后即可作为包含有4个寄存器的16位寄存器组在主机系统中调用。

2、对74670器件的学习74670(三态输出4×4寄存器堆)提供4个4位的寄存器,在功能上可对4个寄存器去分别进行写操作和读操作。

在寄存器进行写操作时,通过WB、WA两个寄存器选择端的组合和00、01、10、11、来选择寄存器,公国GWN写操作端控制进行三态控制,在GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器;在寄存器进行读操作时,通过RB/RA两个寄存器选择端的组合和00、01、10、11来选择寄存器,通过GRN读控制端进行三态控制,在GRN为低电平时将所选寄存器数据通过Q4Q3Q2Q1进行输出,芯片图如下:功能表如下:读功能表:写功能表:四、能完善的寄存器组逻辑电路图(以框图方式画)五、能移位的暂存器设计思想算术移位和逻辑移位区别:算术移位是对带符号数进行移位,逻辑移位对无符号数进行移位。

寄存器组的设计与实现

寄存器组的设计与实现实验三寄存器组的设计与实现⼀、实验⽬的1. 学习掌握Quartus II 的图形编辑、编译、仿真的设计流程;2. 学习74670三态输出寄存器堆的使⽤;3. 理解寄存器组的⼯作原理和过程,设计出4个16位寄存器组并对设计的正确性进⾏验证⼆、实验任务及要求1. 设计出功能完善的寄存器组,并对设计的正确性进⾏验证。

具体要求如下:(1) ⽤图形⽅式设计出寄存器组的电路原理图。

(2) 测试波形要⽤时序仿真实现,先将不同的数据连续写⼊4个寄存器后,再分别读出。

(3) 将设计⽂件封装成器件符号。

(4) 数据的宽度最好为16位。

三、实验装置安装有Quartus II软件的PC机1台四、设计思想运⽤具有三态功能的芯⽚74670进⾏设计,74670为4*4(4个4位寄存器)的寄存器堆,使⽤四⽚74670并联,同时对4 ⽚74670 芯⽚进⾏读写操作控制,从⽽实现4个16位数据的存储与输出。

五、逻辑电路图74670芯⽚图:三态输出的4*4寄存器堆六、实验结果:见原理图,波形图以及元件封装图。

1.原理图分析:见设计思想2.波形图分析:当RE为1,WE不为1时,实现输⼊功能,WB,WA控制数据输⼊到哪个寄存器组当RE为1,WE为1时,出现⾼阻状态,此时既不输⼊也不输出当WE为1,RE不为1时,实现输出功能,RB,RA控制哪个寄存器组的数据输出3.封装元件的功能说明:d[15..0]16位输⼊数据q[15..0]16位输出数据gwn:写⼊数据使能控制端,低有效wa,wb:选择控制端,四种组合控制16位数输⼊到相应四种寄存器组grn:读出数据使能控制端,低有效ra,rb:选择控制端,四种组合控制从四种寄存器组读出相应16位数七、实验⼩结:1.遇到的问题及解决⽅法:a.当Grid Time未进⾏设置时,输出的结果显⽰为全是Z,将时间改成100ns即可。

b.当读⼊操作数时,让WE是能控制端⼀直处于0状态,结果却不能正确显⽰。

实验一 寄存器组实验

实验一寄存器组实验1 实验目的(1) 明确寄存器功能。

(2) 掌握寄存器的工作原理,熟练进行读、写操作。

2 实验设备PC 机一台,TD-CMA实验系统一套。

3 实验原理本实验的原理如图1所示。

图1 寄存器组寄存器组由四个8位寄存器通过单总线结构方式组织,数据写操作由时钟上升沿使能,寄存器数据输出端有三态缓冲器,控制信号低电平有效。

图中T4为时钟信号,是连续的方波,实验台加电后即由时序发生器电路输出,与门的另外一个输入为门控信号,高电平时使T4通过完成寄存器写操作,低电平时寄存器处于数据保持状态。

输入数据由实验台上一组8个拨动开关提供,高电平表示数据1,低电平表示数据0。

寄存器的输出由挂接在总线上的8个led灯显示,其原理如图2所示,当输出数据是1时,灯点亮,数据为0时灯熄灭。

图2 LED显示原理4 实验步骤(1) 按图3 连接实验电路,并检查无误。

图中将用户需要连接的信号用圆圈标明(其它实验相同)。

图3实验接线图(2) 将时序与操作台单元的开关KK2 置为‘单拍’档,开关KK1、KK3 置为‘运行’档。

开关S3至S0置低电平,SD13至SD10置高电平。

(3) 打开电源开关,如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。

(4) 用输入开关向4个寄存器写入数据。

①拨动CON单元的SD27…SD20 数据开关,形成二进制数01100101(或其它数值),数据显示亮为‘1’,灭为‘0’。

②将S0拨至高电平,连续按动时序单元的ST 按钮,产生一个T4 上沿,则将二进制数01100101 置入寄存器R0中,将S0拨回低电平。

用相同操作方法向其他三个寄存器中写入另外3组数据。

(5)依次读取四个寄存器的值,与之前写入的值比较检验是否相同。

以寄存器R0为例,将SD10拨至低电平,数据即输出至总线并由8个LED灯显示,读取输出值,灯亮为1,暗为0。

完成后将SD10拨回高电平。

移位寄存器的设计及实现

移位寄存器的设计及实现移位寄存器(Shift Register)是一种常用的数字逻辑电路器件,它能够将数据按照输入和输出的时序进行移位操作。

通过移位寄存器,我们可以实现数据的串行传输、并行-串行或者串行-并行转换、数据延迟等功能。

本文将对移位寄存器的设计与实现进行介绍。

一、移位寄存器的设计1.串行输入、串行输出的移位寄存器这种移位寄存器称为串行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过一个输入端串行输入,然后通过触发器依次移位,最后从输出端串行输出。

2.并行输入、并行输出的移位寄存器这种移位寄存器称为并行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过n个输入端并行输入到各个触发器,然后通过控制信号进行同步移位。

最后从n个输出端并行输出。

3.并行输入、串行输出的移位寄存器这种移位寄存器称为并行-串行移位寄存器,它先从n个输入端并行输入数据,然后通过控制信号进行同步移位,并将移位结果通过一个输出端串行输出。

4.串行输入、并行输出的移位寄存器这种移位寄存器称为串行-并行移位寄存器,它先从一个输入端串行输入数据,然后通过触发器进行移位,最后将移位结果从n个输出端并行输出。

1.触发器选择由于是8位移位寄存器,需要选择8个触发器。

常用的触发器有D触发器、JK触发器等,可以根据实际需求选择合适的触发器。

2.输入输出端口设计设计一个输入端口用于串行输入数据。

由于是串行输入,需要一个时钟信号和一个使能信号进行同步移位操作。

同时,设计一个输出端口用于串行输出数据。

3.控制信号电路设计根据串行输入、串行输出的要求,需要设计一个时钟信号和一个使能信号的电路。

使能信号在移位过程中保持逻辑高电平,只有当8位数据全部移位完成时才将使能信号置为逻辑低电平。

二、移位寄存器的实现1.设计一个8位移位寄存器电路,并连接8个D触发器。

2.将串行输入信号与D触发器的数据端相连,时钟信号与D触发器的时钟端相连,使能信号与D触发器的使能端相连。

计算机组成原理实验报告-寄存器实验

千里之行,始于足下。

计算机组成原理实验报告-寄存器实验计算机组成原理实验报告-寄存器实验》一、实验目的本次实验旨在通过设计和实现一个基本的寄存器,加深对计算机组成原理中寄存器的理解,并掌握寄存器在计算机中的应用。

二、实验设备及软件1. 实验设备:计算机2. 实验软件:模拟器软件Mars3. 实验材料:电路图、线缆、元器件三、实验原理寄存器是计算机的一种重要组成部分,用于存储数据和指令。

一个基本的寄存器通常由一组触发器组成,可以存储多个位的信息。

本实验中,我们需要设计一个16位的寄存器。

四、实验步骤1. 确定寄存器的结构和位数:根据实验要求,我们需要设计一个16位的寄存器。

根据设计要求,选择合适的触发器和其他元器件。

2. 组装寄存器电路:根据电路图,将选择好的元器件按照电路图连接起来。

3. 连接电路与计算机:使用线缆将寄存器电路连接到计算机的相应接口上。

4. 编写程序:打开Mars模拟器软件,编写程序来测试寄存器的功能。

可以编写一段简单的程序,将数据写入寄存器并读取出来,以验证寄存器的正确性。

5. 运行程序并测试:将编写好的程序加载到Mars模拟器中,并运行程序,观察寄存器的输出和模拟器的运行结果。

第1页/共3页锲而不舍,金石可镂。

五、实验结果在本次实验中,我们成功设计和实现了一个16位的寄存器,并进行了相关测试。

经过多次测试,寄存器的功能和性能良好,能够准确地存储和读取数据。

六、实验心得通过本次实验,我对寄存器的结构和工作原理有了更深入的了解。

寄存器作为计算机的一种重要组成部分,起着存储和传输数据的作用。

通过实际操作和测试,我更加清楚了寄存器在计算机中的应用和重要性。

在实验过程中,我遇到了一些问题,如电路连接不稳定、程序错误等,但通过仔细检查和调试,最终解决了这些问题。

这次实验也让我深刻体会到了学习计算机组成原理的重要性,只有深入理解原理并通过实践运用,才能真正掌握计算机的工作原理和能力。

通过这个实验,我有了更深入的认识和理解,对计算机组成原理的学习也更加系统和完整。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

寄存器组的设计与实现

一、实验目的

1、学习掌握Quartus||软件的基本操作;

2、理解寄存器组的工作原理和过程;

2、设计出寄存器组并对设计的正确性进行验证。

二、实验内容

1、设计出功能完善的寄存器数组并对设计的正确性进行验证。

(1)用图形方式设计出寄存器的电路原理图;

(2)测试波形时用时序仿真实现,先将不同的数据连续写入4个寄存器后,再分别读出;(3)将设计文件封装成器件符号;

(4)数据宽度最好为16位。

三、实验设计

1、集成电路芯片

(1)74760:三态输出4*4寄存器堆

74760提供了4个4位寄存器。

在功能上可对这4个寄存器分别进行写操作和读操作。

在寄存器写操作时,通过WB、WA两个寄存器选择端的组合00、01、10、11选择寄存器。

通过GWN写控制端进行三态控制,GWN为低电平时将数据写入端数据D4D3D2D1写入该寄存器。

在寄存器读操作时,通过RB、RA两个寄存器选择端的组合00、01、10、11选择寄存器,通过GRN读控制端进行三态控制,在GRN为低电平时,将所选寄存器数据通过Q4Q3Q2Q1进行输出。

“写”功能表

“读”功能表

2、设计原理

要设计16位的存储器组,需要74670芯片4片,在寄存器组工作时,同时对4片74670芯片进行操作,封装后即可作为包含有4个16位寄存器的寄存器组在主机系统中调用。

四、实验结果

1、原理图

寄存器组由4个74670组成,将4个芯片的GWN、WA、WB、GRN、RA、RB 分别连在一起,共同控制4个芯片的读写操作。

总共有22个输入端。

即

IN[15]、IN[14]....IN[1]、IN[0]和GWN、WA、WB、GRN、RA、RB。

16个输出

端。

即OUT[15]、OUT[14]...OUT[1]、OUT[0]。

2、波形仿真

当GWN=0、GRN=0都有效时,可以对寄存器组进行读写操作。

当WB/WA=00时,将0321写入寄存器组的W0寄存器,RB/RA=00时,读取寄存器W0的值即0321。

当WB/WA=01时,将1111写入寄存器组的W1寄存器,RB/RA=01时,读取寄存器W1的值即1111。

当WB/WA=10时,将1010写入寄存器组的W2寄存器,RB/RA=10时,读取寄存器W2的值即1010。

当WB/WA=11时,将0201写入寄存器组的W3寄存器,RB/RA=11时,读取寄存器W3的值即0201。

3、封装

将设计好的16位寄存器组封装。

五、实验总结

通过这次实验了解了通用寄存器的使用方法,熟悉了图形语言描述通用寄存器的方法,为以后实验做了准备。