基于FPGA的数字低通滤波器

基于FPGA的三相四线制APF数字低通滤波仿真

第4 期

2 . 3 采样 频率

赵爽, 等: 基于F P G A的三相四线制A P F 数字低通滤波仿真

有源电力滤波过采样技术是在奈奎斯 特频率的基础上实现的 , 通常将采样频率提高一个过采样倍

流检 测 的稳定 性高 。

常用 的数字滤波器有 F I R和 I I R 两种 。A P F 实时性非常重要 , 在 同样的滤波效果条件下 , F I R 设计阶 数比I I R高 5 ~ l O 倍, 花费的资源多 , 成本高 , 同时信号的延迟明显。对于模拟滤波器 , I I R 滤波器可以很方 便利用其参数进行升级 , 设计工作量相对较小。综合比较 , 用F P G A实现 I I R滤波器具有多种优越性。 I I R滤波器主要有 3 种: 巴特沃斯滤波器 , 切 比雪夫滤波器 , 椭 圆滤波器 。在 A P F 中, 需要滤波器具

F P G A用于处理谐波检测, 通过改进瞬时无功功率理论的 ‘一 ‘ 谐波检测方法和合适的低通滤波器配置, 解决电

网负裁不平衡 问题。仿真结果表 明: 采用此方法 , 时延仅 为2 0 0 n s , 对基波没有影响。

关键 词 : 有源电力滤波器; 数字低通滤波器; 三相四线制; 流水线并行处理结构

仿真研究设计 0 . 1  ̄ o . 3 s 为三相对称负载 , 此时负载端为三相对称六脉动晶闸管整流器 , 负载为直流

辽 宁 科 技 大 学 学 报 阻感负载 。A P F 补偿前后 系统 电流波形如 4 图

^

第3 6 卷

所示。

L 1

基于FPGA的IIR低通数字滤波器的设计

文件 时调 用 已建立好 的模 块 。测 试仿 真结 果表 明基于 F GA设计 的 IR数字滤 波器 达到 了设计 要求 。 P I

关键 词 :I I R数字 滤波 器 级 联型 中图分 类号 :T 1 N7 3 F GA P 文章 编号 :1 0 .8 22 1)20 2 .3 0 34 6 (0 20 .0 40

小截 断误 差的考 虑 , 据设计 指标 首先 利用 Mal 依 t b进行 参数 的计算 并进行 量化 ,同时获得 系统 的幅频 响应 、 a 单位 冲击 响应等 系统 基本信 息 。随后 在分 析 IR 数字 滤波器 内部 乘法器 、加 法器 的输入 输 出基础上 ,调 用 I Q ats I u r 软件 调试 程序 建立乘 法器 和加 法器模 块 ,依据 自顶 向下的设 计思想 搭建 整体 电路 ,并在 建立项 层 uI

据 幅度 特 性 指 标 要 求 设 计 了 一个 输 入 8位 、输 出

8位 的 IR低 通 数 字滤 波 器 。 I

频谱分析等领域 。数字滤波器按照响应方 式的不 同 ,可 分 为 FR ( 限长 脉 冲 响 应 )滤 波 器 和 IR I 有 I ( 限长 脉 冲 响应 ) 波 器 ] 比较 于 FR 数 无 滤 。相 I

Ab tat On ido IR d i l l rw ihhs8i usa d8o tusi ds ndbsdo PG I src: ekn I i t f t hc a n t n u t s ei e ae nF A.n f g ai e p p g tr so elain o sdrn erai h ut g err rt 'tep rmeesaecm ue n em frai t .cniei dces g tectn ro, sl h aa t r o p td ad z o g n i y r q a te yui t bb sdo eing ieie h se fr aino a ntd ep nead u ni db sn Mal ae nd s ud l .Tes tm i om t m g i erso s n z g a g n y n o f u ip l e o s r l curd L trbsdo ea a s p t n u u IRdgtl l rn e m us rs ne e s aq i . ae ae t n l io i u do t tf I ii f t n r e p a ao e , nh y sf n a p o ai e i mut l ainada dr c ie Quru it n erdt tpmut l aina da drm c ie l lpi t n d e hn , ats s r s re s lpi t n d e a hn d i c o ma H a f o eu i c o mo

基于FPGA的16阶FIR数字滤波器的设计

基于FPGA的16阶FIR数字滤波器的设计作者:王香张莉莉来源:《电子世界》2013年第16期【摘要】本文是利用Altera提供的DSP Builder开发工具从Simulink模型自动生成VHDL 代码的一种FPGA设计方法来实现一个16阶FIR数字低通滤波器,设计出的滤波器用于线性调制的相干解调中。

通过对设计的电路进行验证和仿真,结果表明电路工作正确可靠,能满足设计要求。

【关键词】FPGA;DSP Builder;FIR数字低通滤波器;相干解调1.引言信号的数字滤波在图像处理、语音识别、模式识别等数字信号处理中都占有要的地位。

与模拟滤波器相比,数字滤波器可以满足滤波器幅度和相位特性的严格要求,可以克服模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

根据数字滤波器冲激响应函数的时域特性,可将数字滤波器分为无限长冲激响应(IIR)滤波和有限长冲激响应(FIR)滤波器两种。

由于FIR系统只有零点、系统稳定,便于实FFT算法、运算速度快、线性相位的特性和设计更为灵活等突出优点而在工程实际中得广泛应用。

在复杂运算中,FPGA的处理速度表现了很好的优势,而且FPGA开发周期短且编程灵活,易于反复擦写,算法实现不受DSP之类固件性能的限制。

本文研究了基于FPGA的16阶数字低通滤波器硬件电路的实现方法。

设计出的16阶FIR 数字低通滤波器用于线性调制中的相干解调(也叫同步解调)来实现对原始信号的恢复。

2.本设计利用的基本原理及设计指标的选择2.1 相干解调的基本原理在线性调制中,设调制信号m(t)=sinω1t,载波为cosωct,则已调信号:Sm(t)=m(t)cosωct将已调信号乘上一个同频同相的载波,得:χ(t)=Sm(t)cosωct=m(t)(cosωct)2 =0.5m(t)+0.5m(t)cos2ωct由上式可知,用一个低通滤波器可以将第一项与第二项分离,从而恢复出原始的调制信号,这种方法称为同步解调或相干解调。

基于FPGA的数字滤波器的设计与实现

基于FPGA的数字滤波器的设计与实现数字滤波器是一种非常重要的数字信号处理技术,用于消除输入信号中的噪声,并提高信号品质和可靠性。

FPGA(Field Programmable Gate Array)是一种用于构建数字电路的可编程逻辑器件,因其高度的可定制性、可重构性和高性能而被广泛应用于数字信号处理中。

本文将介绍基于FPGA的数字滤波器的设计和实现,包括滤波器原理、数字滤波器设计方法、FPGA实现技术以及实验结果分析等内容。

一、数字滤波器原理数字滤波器是滤波器的一种,其实现基于数字信号处理技术。

数字滤波器的输入信号是离散时间信号,输出信号也是离散时间信号。

数字滤波器通过在离散时间域上对输入信号进行滤波,实现对输入信号中某些频率成分的滤除或保留。

数字滤波器通常分为FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器两类。

FIR滤波器是一种线性相位滤波器,其系统函数是一个有限长度的冲激响应权重系数序列。

FIR滤波器通过对输入信号的每个样本与权重系数的乘积进行累加,输出得到滤波后的信号。

FIR滤波器具有零相位失真、线性相应特性、易于设计、易于实现等优点。

IIR滤波器是一种具有无限脉冲响应的滤波器,其系统函数是一个有理多项式。

与FIR滤波器相比,IIR滤波器具有更高的滤波效率、更低的计算复杂度和更好的逼近性,但也存在稳定性差、相位失真大等问题。

二、数字滤波器设计方法数字滤波器的设计方法主要包括滤波器性能要求的确定、滤波器类型的选择、滤波器设计的数学模型的建立、滤波器参数的计算、滤波器实现等几个方面。

在确定滤波器性能要求方面,需要考虑滤波器的通频带、阻带、通带和阻带带宽、滤波器响应曲线、阶数等方面的参数。

在滤波器类型的选择方面,需要根据滤波器的性能要求、实现难易度、计算复杂度和开销等方面的因素进行综合考虑。

在滤波器设计的数学模型的建立方面,需要根据选定的滤波器类型建立其对应的数学模型。

在滤波器参数的计算方面,需要根据滤波器的数学模型进行参数的计算和优化。

基于FPGA的IIR数字滤波器设计

摘要数字信号处理在科学和工程技术等许多领域中得到了广泛的应用,其中数字滤波器是现代数字信号处理系统的重要组成部分。

无限长单位冲激响应(IIR)数字滤波器是非常重要的一类滤波器,与有限长单位冲激响应(FIR)数字滤波器相比,IIR能够以较低的阶次获得较高的频率选择特性从而得到了广泛的应用。

本课题采用一种基于现场可编程门阵列(FPGA)的IIR数字滤波器的设计方案。

首先基于IIR数字滤波器的相关理论知识,研究了IIR数字滤波器的常用设计方法,并分析了各种IIR数字滤波器的实现结构等基本理论,由分析结果确定了所要设计的IIR数字滤波器的实现结构。

然后基于FPGA的结构特点,研究了IIR数字滤波器的FPGA设计与实现,并通过Quartus Ⅱ设计平台,采用自顶向下的模块化设计思想,将整个IIR数字滤波器分为:时序控制、延时、补码乘加和累加四个功能模块。

分别对各模块进行VHDL语言描述,并进行了仿真和综合。

仿真结果表明,本设计的IIR数字滤波器运算速度较快,系数改变灵活,有较好的参考价值。

关键词:数字滤波器;无限长单位冲激响应;现场可编程门阵列;VHDL硬件描述语言ABSTRACTDigital signal processing is widely used in lots of fields, such as in science and project technique, Digital filter is one of the important contents of digital signal process. Infiinite impulse response units (IIR) digital filter is a very important type of filters. With its good characteristic of frequency selection in lower order in comparison with finite impulse response (FIR), IIR digital filter is widely applied in modern signal processing systems. This subject is a IIR digital filter design based on the using of field programmable gate array (FPGA). Firstly, based on the analysis of IIR basic realization architectures and the related theoretic analysis, the design methods of IIR sigital filter has been discussed and the structures of a variety of IIR digital filter which can be realized has been analysised. For the results of the theoretical analysis, the final architecture and realization of IIR digital has been decided, Based on the structural characteristics of FPGA, the FPGA design and realization of IIR digital filter has been researched. By used the design plant of Quartus Ⅱ, we adopt blocking method named “Top-down ” and divide the entire IIR digital filter into four blocks, which are Clock control, Time delay, Multiply-addition and Progression. After described with VHDL,we do emulate and synthesis to each block. The result shows that, the introduced IIR digital filter runs fast, and the coefficient changes agility. It has high worth for consulting.Key Words: Digital filter; infinite impulse response units; field programmable gate array; VHDL hardware description language目录1器件简介 (1)2 IIR数字滤波器的相关理论 (4)2.1 IIR滤波器的基本理论 (4)2.1.1 IIR数字滤波器的幅频特性 (5)2.1.2 IIR数字滤波器的相频特性 (7)2.2 IIR数字滤波器的实现结构 (7)2.2.1 直接型结构 (7)2.2.2 级联型结构 (8)2.2.3并联型结构 (10)2.3 数字滤波器的有限字长效应理论 (10)2.3.1 数字表示 (11)2.3.2 输入量化 (12)2.3.3 系数量化 (13)2.3.4 乘积量化 (17)2.3.5 极限环 (19)3 IIR数字滤波器的分析设计 (21)3.1 IIR数字滤波器的模拟转换设计法 (21)3.2 IIR数字滤波器的S-Z变换设计 (21)3.2.1标准Z变换 (22)3.2.2双线性Z变换 (24)3.3 IIR数字滤波器的零极点累试法 (25)3.4 优化设计法 (25)3.5 IIR数字滤波器的硬件实现方案 (25)4 EDA技术和可编程逻辑器件 (30)4.1 电子设计自动化EDA技术 (30)4.2 可编程逻辑器件 (30)4.2.1 FPGA概要 (31)4.2.2 FPGA设计语言 (31)4.2.3 FPGA开发环境 (32)5 IIR数字滤波器的设计与仿真结果分析 (33)5.1 各模块的设计与仿真结果分析 (33)5.1.1 时序控制模块的设计与仿真结果分析 (33)5.1.2 延时模块的设计与仿真结果分析 (34)5.1.3 补码乘加模块的设计与仿真结果分析 (35)5.1.4 累加模块的设计与仿真结果分析 (36)5.1.5 顶层模块设计 (36)5.2 IIR数字滤波器的仿真与结果分析 (37)5.2.1 IIR数字滤波器的系统设计 (37)5.2.2 IIR数字滤波器的系统仿真与结果分析 (38)5.2.3 高阶IIR数字滤波器的实现 (39)6 IIR数字滤波器的硬件实现 (40)6.1 IIR数字滤波器的硬件实现平台 (40)6.1.1 硬件结构 (40)6.1.2器件介绍 (41)6.1.3 JTAG链简介 (43)6.1.4 FPGA的配置 (44)6.2 IIR数字滤波器的VHDL设计 (45)6.2.1 接口定义 (45)6.2.2 综合与仿真 (45)6.3 数字滤波器的实现 (45)结束语 (46)参考文献 (47)致谢 (48)附录1 各模块VHDL程序 (49)1器件简介数字滤波器是具有一定传输选择特性的数字信号处理装置,其输入、输出均为数字信号,实质上是一个由有限精度算法实现的线性时不变离散系统。

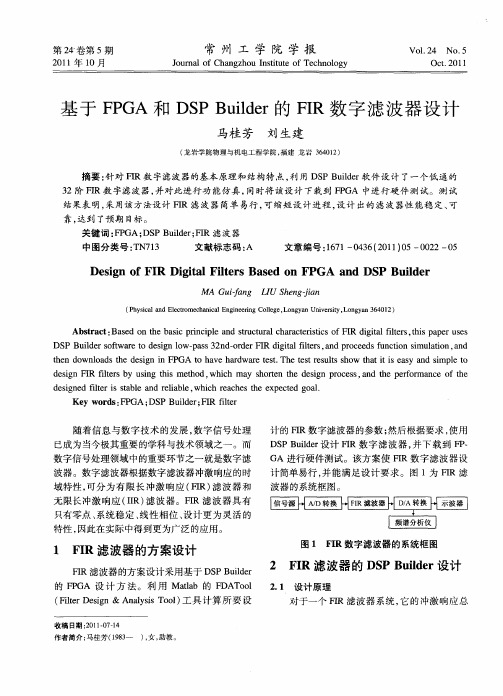

基于FPGA和DSP Builder的FIR数字滤波器设计

1 F R滤波器的方 案设计 I

FR滤 波器 的方案 设计 采用基 于 DS ule I PB i r d 的 F GA 设 计 方 法 。利 用 Mal 的 F A ol P tb a D To ( ie ein&Anls o 1工 具 计 算 所 要 设 FlrD s t g a i T o) ys

无 限长 冲 激 响 应 (I 滤 波 器 。FR滤 波 器 具 有 I R) I 只有零 点 、 系统 稳 定 、 性相 位 、 计 更 为 灵 活 的 线 设 特性 , 因此 在实 际 中得 到更 为广泛 的应 用 。

G A进行硬件测试。该方案使 F I R数字滤波器设 计简单 易行 , 能满 足设 计 要求 。图 1为 FR滤 并 I 波器 的系统 框 图。

De i n o R g t lFi e s Ba e n FPGA n S Bui r sg fFI Di ia l r s d o t a d D P l de

MA G i a g L U S egj n u- n I hn -a f i

( h s a adEet mehncl n ier gC l g , og a iesy,o g a 6 0 2 P yi l n l r c aia E gn e n ol e L nynUnvrt L n yn3 4 1 ) c co i e i

Absr c Ba e n t sc p n i l n tu t r lc a a trsi so R i ia l r ,h spa e s s t a t: s d o heba i r c p e a d sr cu a h r ce t fFI d g tlf t s t i p ru e i i c i e

收稿 日期 :0 10 — 2 1-71 4 作者简介 : 马桂 芳( 93 18 一 )女 , , 助教。

基于 FPGA 的数字滤波器设计与实现

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

基于FPGA_的数字滤波器设计

332023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview进行相乘后,再积分运算,去除时间无关的干扰信号,获I/O 资源,含一个LTC 1407A 模数转换器和一个收稿日期:2022-10-10作者简介:周钧(1987—),男,壮族,广西南宁人,硕士研究生,工程师、硬件设计师,研究方向:FPGA、网络通信。

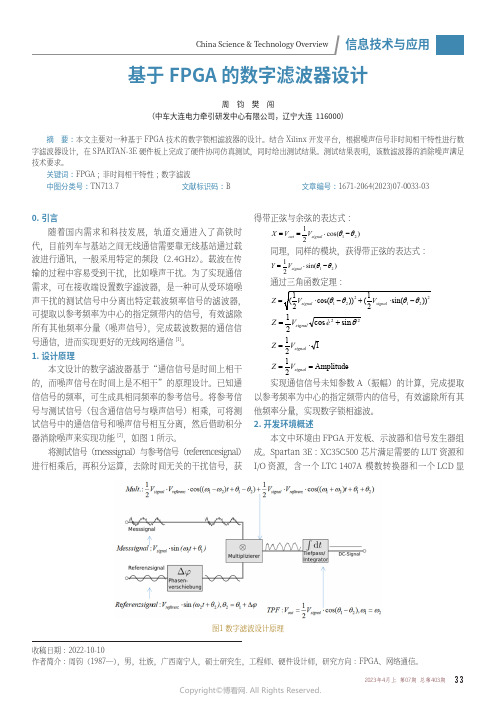

基于FPGA 的数字滤波器设计周 钧 樊 闯(中车大连电力牵引研发中心有限公司,辽宁大连 116000)摘 要:本文主要对一种基于FPGA 技术的数字锁相滤波器的设计。

结合Xilinx 开发平台,根据噪声信号非时间相干特性进行数字滤波器设计,在SPARTAN-3E 硬件板上完成了硬件协同仿真测试,同时给出测试结果。

测试结果表明,该数滤波器的消除噪声满足技术要求。

关键词:FPGA ;非时间相干特性;数字滤波图1 数字滤波设计原理342023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview示器。

示波器Tektronix TPS 2024:带宽为200MHz,最高取样速率:2.0GS/s,具有4个通道。

信号发生器HM-8030:频率50MHz 至10MHz,具备高纯度和幅度稳定性。

3.基于FPGA 的数字滤波器设计3.1 设计框架FPGA 设计框架如图2所示。

块,滤波模块和LCD 显示模块这些二级模块组成;(5)各二级模块根据功能划分,将各自功能用VHDL 进行编码设计。

二级模块经过仿真实现,在顶层模块进行结合,实现一整套系统功能。

3.3.1 模数转换设计ADC 芯片将采集的模拟信号离散化为单个离散采样值。

再将采样值转为数字值,根据板卡搭载的ADC 芯片[4]simulation 仿真产生的模拟信号可以非常接近,但是始图3 测试验证(a)测试1(b)测试2China Science & Technology Overview信息技术与应用0,4 V(max 0,223 V)(max 0,239 V)(max 0,233 V)(max 0,214 V)(max 0,234 V)352023年4月上 第07期 总第403期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

泉州师范学院毕业论文(设计)题目基于FPGA的数字低通滤波器物理与信息工程学院电子信息科学与技术专业07级学生姓名周志凯学号*********指导教师吴志伟职称讲师完成日期2011年4月教务处制基于FPGA的数字低通滤波器物理信息工程学院电子信息科学与技术专业 070303025 周志凯指导老师:吴志伟讲师【摘要】:低通滤波器是让某一频率以下的信号分量通过,而对该频率以上的信号分量大大抑制的电容、电感与电阻等器件的组合装置。

数字滤波器能够满足对于相位特性跟幅度的严格要求,能够改善模拟滤波器无法解决的电压和温度漂移还有噪声等问题。

利用FPGA,在QUARTUSⅡ平台上使用VHDL银剑描述语言改变滤波器的系数和阶数,通过结合MATLAB工具软件的辅助设计,使低通滤波器具有快速、灵活硬件资源损耗少。

【关键词】:FPGA;MATLAB;数字滤波器;QUARTUSⅡ目录1引言 (4)2 EDA技术的主要内容 (4)2.1大规模可编程器件 (4)2.2硬件描述语言 (4)2.3软件开发工具 (4)2.4实验开发系统 (5)3 FPGA简介 (5)4 MATLAB简介 (5)5 数字滤波器的工作原理 (6)6低通滤波器的基本特性 (6)7用MATLTAB设计低通滤波器 (7)7.1在MATLAB中进行仿真设计 (7)7.2运用QuatusⅡ检验滤波效果 (9)7.3结果记录 (12)8结束语 (12)致谢 (13)参考文献: (13)附录: (15)1引言随着现在科学技术的高速发展,高精度集成电路的使用,生产力有了大幅度的发展,快捷的EDA工具,使用集成化设计环境,需要更快的速度来开发出质量一流性能优良的电子产品,这对于EDA技术有了更高的要求了。

未来的EDA技术将在仿真、时序分析、集成电路自动测试、高速印刷电路板设计及开发操作平台等方面取得新的突破,向着功能强大、简单易学、使用方便的方向发展[1]。

本次设计的基于FPGA的数字低通滤波器是围绕EP2C8Q208C8芯片添加输入和输出电路而成的。

用户通过QuartusⅡ进行编程、仿真、下载到芯片实现相应的功能,简单方便,具有很高的实用价值。

2 EDA技术的主要内容EDA (Electronic Design Automation)是指利用计算机完成电子系统的设计,以计算机和微电子技术为先导,汇集了计算机图形学、逻辑学、微电子工艺和结构学以及计算数学等多种计算机应用学科最新成果的先进技术。

EDA技术一般包括以下四个方面:1.大规模可编程逻辑器件;2硬件描述语言;3软件开发工具;4实验开发系统。

2.1大规模可编程器件可编程逻辑器件(PLD)是一种由用户变成以实现某种逻辑功能的新型逻辑器件。

FPGA 和CPLD器件的应用广泛,随着EDA技术的发展成为电子设计领域的重要角色。

FPGA包括可编程逻辑单元,可编程输入/输出单元和可编程连线三个部分;而CPLD则包括可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。

他们的最明显特点是高集成度、高速度和高可靠性[2]。

2.2硬件描述语言VHDL:在电子科技工程领域里,作为IEEE的工业标准硬件描述语言,已成为通用的硬件描述语言。

Verilog:比较使用RTL级和门电路级的描述,综合过程比VHDL简单一点,在高级描述语言方面没有VHDL好。

2.3软件开发工具当前比较流行的EDA软件工具有Altera公司的quartusⅡ、Lattice 公司的ispexpert、Xilinx公司的foundation Series。

本次设计所用的软件是quartusⅡ。

Quartus II:支持原理图、VHDL和Verilog 语言文本文件以及波形与EDIF等格式的文件作为设计输入,并支持这些文件的任意形式混合设计。

它具有门级仿真器,可以进行功能仿真和时序仿真,能够产生精确的仿真结果。

在适配之后,Quartus II生成供时序仿真用的EDIF、VHDL和Verilog这三种不同格式的网表文件[3]。

它使用便捷,是最易学易用的EDA 软件,并支持主流的第三方EDA工具,支持除APEX20K系列之外所有的Altera公司的FPGA/CPLD大规模逻辑器件[4]。

2.4实验开发系统提供芯片下载电路及EDA实验/开发的外围资源,供硬件验证用。

一般有以下几个:①在实验中或者开发所需要的各种类型的基本信号发生模块;②CPLDFPGA输出信息显示模块,例如发光管的显示、数码的显示还有声响指示;③监控的程序模块,提供电路重构软配置;④目标芯片适配座。

3 FPGA简介FPGA(Field-Programmable Gate Array)是现场可编程门阵列的简称,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

FPGA的基本特点一般有以下几个方面:①采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片;②FPGA可做其它全定制或半定制ASIC电路的中试样片;③FPGA内部有丰富的触发器和I/O引脚;④FPGA是ASIC电路中设计周期最短、风险最小、开发费用最低的器件之一;⑤FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

一般来说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一[5]。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA 功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

4 MATLAB简介MATLAB 是美国MathWorks公司出品的商业数学软件,用于算法开发、数据可视化、数据分析以及数值计算的高级技术计算语言和交互式环境,主要包括MATLAB 和Simulink 两大部分。

MATLAB 一般可以用来做数值分析、数值和符号计算、控制系统的设计与仿真、工程与科学绘图、财务与金融工程、通讯系统设计与仿真、数字图像处理技术等。

5 数字滤波器的工作原理数字滤波器一般包括无限冲激响应(IIR )系统和有限冲激响应(FIR)系统。

假设输入序列是x(n),离散或者数字滤波器对单位的抽样序列()n δ的响应为h(n)。

()n δ在时域离散信号里面和系统中起的作用是和单位冲激函数在时域连续信号和系统中所起的作用是一样的。

如下图1所示。

数字滤波器的序列y(n)是这两个序列的离散卷积,即()()()k y n h k x n k ∞=∞=-∑两个序列卷积的z 变换等于个自z 变换的乘积,即Y(z)=H(z)X(z)用j T e ω代入上式,T 为抽样周期,可得Y(j T eω)=H(j T e ω)X(j T e ω) 式中X(j T e ω)和Y(j T e ω)分别为数字滤波器输入序列和输出序列的频谱,H(j T eω)是单位抽样序列响应h(n)的频谱。

因此输入序列的频谱X(j T eω)经过滤波后,变为H(j T e ω)X(j T eω),按照X(j T e ω)的特点和处理信号的目的,选取适当的H(j T e ω)使得滤波后的H(j T e ω)X(j T e ω)符合所需要的要求。

6低通滤波器的基本特性数字滤波器的差分方程表示为:10()()()N M k k i k y n b y n i a x n k ===-+-∑∑系统函数为01()()()1M k k K N ik I a z Y z H z X z b z -=-===-∑∑数字滤波器的特性通常用频率响应函数()j H e ω来描述的。

本次设计用的是低通数字滤波器如下图2所示。

图2 低通滤波器的频谱7用MATLTAB 设计低通滤波器当前数字滤波器有很多现成的高级语言设计程序,但是因为运用MATLAB 可以使得数字滤波的研究和应用更直观便捷还有高效率。

它具有融合计算、可视化、程序设计的一个交互式的环境,可以使得我们更直观而且更方便的进行研究和应用。

7.1在MATLAB 中进行仿真设计在利用MATLAB 设计低通滤波器时,通过利用FDAFOOL 工具可以非常方便的设计出数字低通滤波器,设计过程比较简单,编写的程序也不会很长,是很容易设计出来的。

FDAFOOL 是MATLAB 中的一种图形用户工具,可以为设计提供一个综合简便的图形用户界面。

本次设计的低通滤波器的指标为:模拟信号采样频率FS=3.1kHz,通带截止频率Fpass=0.8kHz,阻带截止频率Fstop=1.2kHz ,在图3界面中设置好各项参数,选择FIR 的Equiripple 滤波器,然后点击Design Filter ,就可以得到所设计滤波器的模型。

从图中可以观察其幅度响应、相位响应,也可以观察到脉冲响应、阶跃响应、滤波器的零极点绘制图和系统函数的各个系数等指标。

然后点击Targets 选项中的GenerateHDL,会出现如图4的界面。

将Filter target language设置为Verilog。

点击OK就生成对位的文件,可以用quartusⅡ软件打开以上文件进行编译、综合,最后将其下载到FPGA中即可实现低通滤波器的功能。

图3 FDATool界面图4 Genetate HDL界面7.2运用QuatusⅡ检验滤波效果用quartusⅡ打开设计好的文件如图5所示。

图5 fire原理图各个引脚锁定如图6所示。

图6 各引脚锁定图图5中运用的A/D转换模块是TLC549,D/A转换模块为TLC5615图7 TLC549的引脚图TLC各引脚功能如下【6】:REF+:正基准电压输入端,2.5V≤REF+≤Vcc+0.1。

REF-:负基准电压输入端,-0.1V≤REF-≤2.5V,且要求REF+-REF-≥1V。

ANALOG IN:模拟信号输入端,0≤ANALOG IN≤Vcc,当ANALOG IN≥REF+电压时,转换结果为全“1”(FFH),ANALOG IN≤REF-电压时,转换结果为全“0”(00H)。