fpga内部可用资源

fpga资源评估与选型

fpga资源评估与选型

FPGA(Field-ProgrammableGateArray)是一种高度可编程且可重构的硬件芯片,可以用于实现各种复杂的数字电路。

FPGA引入了可编程性的概念,使硬件设计更加灵活、高效。

在FPGA设计过程中,资源评估和选型是非常重要的环节。

资源评估是指根据设计需求,评估所需的FPGA资源,包括片上存储器、LUT(Look-Up Table)等。

在评估时需要考虑以下因素:首先,需要确定设计的复杂度以及所需的资源;其次,需要考虑FPGA 的速度、功耗以及可编程性等因素。

在选型过程中,需要考虑到FPGA的规格、性能、价格等因素。

首先,需要了解FPGA的规格,包括芯片大小、引脚数、逻辑单元数量等。

其次,需要考虑FPGA的性能,例如时钟速度、功耗、温度等因素。

最后,需要考虑FPGA的价格,这是每个设计师都必须考虑的因素之一。

为了选择适合自己的FPGA芯片,设计师可以通过以下渠道了解相关信息:首先,可以查阅FPGA厂商的官方网站了解产品信息;其次,可以参考各种技术论坛、电子书籍、设计手册等资料,以获取更全面、深入的了解。

在实际选型过程中,设计师还需要考虑到FPGA的开发环境,包括开发软件、编程语言、板子等。

此外,设计师还需要仔细评估FPGA 的可靠性、稳定性以及后续技术支持等因素。

总之,FPGA资源评估和选型是一项非常重要的任务,需要设计

师充分了解自己的设计需求和FPGA的规格、性能、价格等因素,以选择最适合自己的芯片。

通过认真评估和选型,设计师可以实现高效、可靠的FPGA设计,提高设计效率和质量。

FPGA设计中的资源分配与约束原则

FPGA设计中的资源分配与约束原则在FPGA(现场可编程门阵列)设计中,资源分配和约束原则是至关重要的。

资源分配是指如何有效地利用FPGA中的可用资源,包括逻辑单元、存储单元和IO端口等。

而约束原则则是指在设计过程中对资源进行限制和指导,以确保设计的性能、功耗和面积都能达到预期的要求。

资源分配是设计过程中的第一步,决定了设计的整体架构和实现方式。

首先要考虑的是逻辑单元的分配,包括布局和布线。

根据设计的需求和复杂性,可以选择不同的逻辑单元,如LUT(查找表)、寄存器、乘法器等。

在资源分配过程中,需要考虑到逻辑单元之间的连接和数据传输路径,以尽量减少延迟和功耗。

此外,还需要合理地分配存储单元和IO端口,以满足设计的数据存储和通信需求。

在资源分配的基础上,约束原则则是确保设计达到预期性能和质量的关键因素。

在FPGA设计中,约束可以分为时序约束和布局约束。

时序约束是指设计中信号传输路径的时序要求,包括最大延迟、最小延迟和时钟频率等。

通过时序约束,可以保证设计在指定的时钟频率下正常工作,并确保时序正确性。

布局约束则是指对设计中不同模块的布局和位置进行指导,以减少信号传输路径的延迟和功耗,提高设计的性能和效率。

在进行FPGA设计时,需要遵循以下资源分配和约束原则:1.合理利用逻辑单元:根据设计的需求选择适当的逻辑单元,以实现最优的性能和面积利用率。

合理布局逻辑单元,减少传输路径的延迟和功耗。

2.优化存储单元和IO端口分配:根据设计的数据存储和通信需求合理分配存储单元和IO端口,确保数据传输的有效性和可靠性。

3.设置严格的时序约束:对设计中的时序要求进行准确分析和设置,确保设计在指定的时钟频率下正常工作。

通过时序约束,避免时序问题和时钟冲突。

4.合理布局约束:对设计中各个模块的布局和位置进行指导,减少传输路径的延迟和功耗,提高设计的性能和效率。

通过布局约束,优化设计的物理结构和实现方式。

总之,在FPGA设计中,资源分配和约束原则是设计过程中的关键步骤。

如何分析FPGA的片上资源使用情况

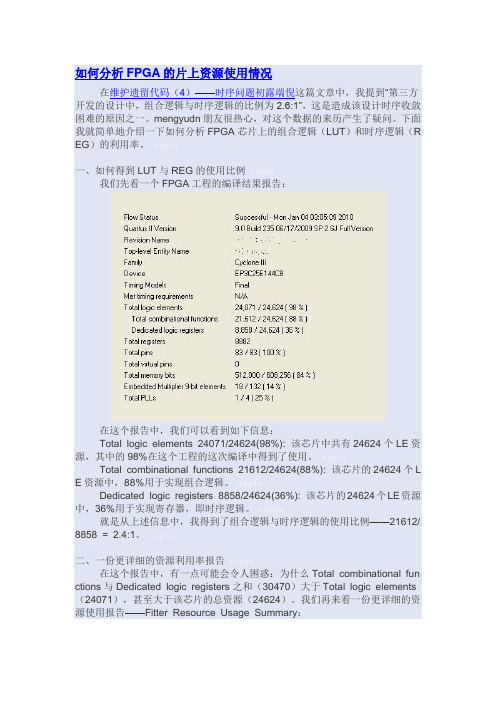

如何分析FPGA的片上资源使用情况在维护遗留代码(4)——时序问题初露端倪这篇文章中,我提到“第三方开发的设计中,组合逻辑与时序逻辑的比例为2.6:1”,这是造成该设计时序收敛困难的原因之一。

mengyudn朋友很热心,对这个数据的来历产生了疑问。

下面我就简单地介绍一下如何分析FPGA芯片上的组合逻辑(LUT)和时序逻辑(R EG)的利用率。

riple一、如何得到LUT与REG的使用比例riple我们先看一个FPGA工程的编译结果报告:在这个报告中,我们可以看到如下信息:Total logic elements 24071/24624(98%): 该芯片中共有24624个LE资源,其中的98%在这个工程的这次编译中得到了使用。

ripleTotal combinational functions 21612/24624(88%): 该芯片的24624个L E资源中,88%用于实现组合逻辑。

ripleDedicated logic registers 8858/24624(36%): 该芯片的24624个LE资源中,36%用于实现寄存器,即时序逻辑。

riple就是从上述信息中,我得到了组合逻辑与时序逻辑的使用比例——21612/ 8858 = 2.4:1。

riple二、一份更详细的资源利用率报告riple在这个报告中,有一点可能会令人困惑:为什么Total combinational fun ctions与Dedicated logic registers之和(30470)大于Total logic elements (24071),甚至大于该芯片的总资源(24624)。

我们再来看一份更详细的资源使用报告——Fitter Resource Usage Summary:这份报告包含很多信息,在这里我们只需要关心Total logic elements一项。

Total logic elements 24071/24624(98%)由三种使用情况不同的LE资源组成:仅用于实现组合逻辑的LE(Combinational with no register 15213),仅用于实现时序逻辑的LE(Register only 2459),同时用于实现组合逻辑和时序逻辑的LE(Combinational with a register 6399)。

FPGA设计中的资源约束分析与分配策略

FPGA设计中的资源约束分析与分配策略在进行FPGA设计时,资源约束分析与分配策略是非常重要的步骤。

FPGA (现场可编程门阵列)是一种灵活的数字电路器件,可以根据需要重新配置其逻辑功能,因此设计出的电路可以在硬件中实时进行配置。

然而,在设计FPGA时,需要考虑到其资源约束和合理分配策略,以避免资源的浪费和性能的下降。

资源约束分析是指在FPGA设计中,需要考虑的可用资源,如逻辑单元、存储单元、时钟资源等。

这些资源是有限的,在设计中需要合理分配和利用。

在资源约束分析阶段,设计者需要根据项目的需求和设计的复杂性确定所需资源的数量和类型。

通过对资源的约束进行分析,可以避免在后期设计过程中资源不足或过剩的问题。

在资源约束分析的基础上,设计者要制定合理的资源分配策略。

资源分配策略是指如何将有限的资源分配给不同的模块或任务,以达到最优的设计效果。

一般来说,资源分配策略需要考虑到以下几个方面:首先,需要根据设计的功能和性能需求,确定各个模块所需的资源数量。

通过对各模块的资源需求进行评估和分析,可以有效地分配资源,避免资源的浪费。

其次,要考虑到资源之间的竞争关系。

不同资源之间可能存在竞争关系,如时钟资源和逻辑资源之间的竞争。

设计者需要合理分配资源,避免资源之间的冲突,提高设计的效率和性能。

另外,要考虑到资源的时序要求。

FPGA设计中,时序约束是非常关键的,资源的分配需要满足时序要求,以保证设计的正确性和稳定性。

设计者需要根据时序要求,合理分配资源,避免时序冲突导致设计失败。

最后,要考虑到资源的动态分配。

在设计过程中,可能需要动态地分配资源,根据实际情况调整资源的分配策略。

动态资源分配可以根据设计的需要灵活调整资源的分配,以达到最优的设计效果。

总之,资源约束分析与分配策略对于FPGA设计非常重要。

通过合理的资源约束分析和资源分配策略,可以提高设计的效率和性能,避免资源的浪费和性能的下降。

设计者在进行FPGA设计时,应该重视资源约束分析与分配策略,从而设计出更优质的电路。

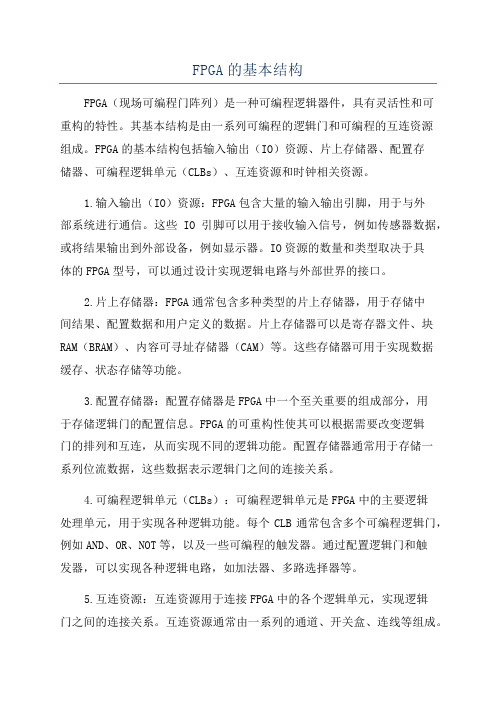

FPGA的基本结构

FPGA的基本结构FPGA(现场可编程门阵列)是一种可编程逻辑器件,具有灵活性和可重构的特性。

其基本结构是由一系列可编程的逻辑门和可编程的互连资源组成。

FPGA的基本结构包括输入输出(IO)资源、片上存储器、配置存储器、可编程逻辑单元(CLBs)、互连资源和时钟相关资源。

1.输入输出(IO)资源:FPGA包含大量的输入输出引脚,用于与外部系统进行通信。

这些IO引脚可以用于接收输入信号,例如传感器数据,或将结果输出到外部设备,例如显示器。

IO资源的数量和类型取决于具体的FPGA型号,可以通过设计实现逻辑电路与外部世界的接口。

2.片上存储器:FPGA通常包含多种类型的片上存储器,用于存储中间结果、配置数据和用户定义的数据。

片上存储器可以是寄存器文件、块RAM(BRAM)、内容可寻址存储器(CAM)等。

这些存储器可用于实现数据缓存、状态存储等功能。

3.配置存储器:配置存储器是FPGA中一个至关重要的组成部分,用于存储逻辑门的配置信息。

FPGA的可重构性使其可以根据需要改变逻辑门的排列和互连,从而实现不同的逻辑功能。

配置存储器通常用于存储一系列位流数据,这些数据表示逻辑门之间的连接关系。

4.可编程逻辑单元(CLBs):可编程逻辑单元是FPGA中的主要逻辑处理单元,用于实现各种逻辑功能。

每个CLB通常包含多个可编程逻辑门,例如AND、OR、NOT等,以及一些可编程的触发器。

通过配置逻辑门和触发器,可以实现各种逻辑电路,如加法器、多路选择器等。

5.互连资源:互连资源用于连接FPGA中的各个逻辑单元,实现逻辑门之间的连接关系。

互连资源通常由一系列的通道、开关盒、连线等组成。

通道用于传递信号,开关盒用于控制信号的选择和连接,连线用于连接逻辑门和触发器。

6.时钟相关资源:时钟相关资源用于处理时钟信号,并确保在同步系统中的正确操作。

FPGA通常包含时钟管理资源和时钟分配网络。

时钟管理资源用于产生和分配时钟信号,时钟分配网络用于将时钟信号传递到逻辑单元和存储单元。

FPGA的基本原理(详细+入门)

精选2021版课件

ห้องสมุดไป่ตู้

20

十、 FPGA的集成度

• 门阵等效门:一个门阵等效门定义为一 个两输入端的“与非”门。

• 系统门:是芯片上门的总数,是厂家指 定给器件的一个门数。

精选2021版课件

21

十一、FPGA的封装

1、引脚数:FPGA芯片总的引脚数。

2、用户I/O数:指除了电源引脚、特殊功能引脚外的引 脚,这些引脚可根据用户的需要进行配置。

l PAL 即 Programmable array logic,是70年代末80年代初由Monolithic Memories Inc。(现为AMD的一部分)首先推出。它是一种熔丝可编 程的器件,采用双极性工艺生产,可用来把几片分立的TTL电路集成 到一片PAL中。PAL是一次性编程的可编程逻辑器件。

• 当b=1时: y= s a + s =a + s

当b=1时,二选一可完成“或门”的功能。

精选2021版课件

10

2) ACT1 的逻辑模块:

• 下图为Actel公司生产的ACT1系列FPGA的逻辑模块框图,ACT1 逻辑模块由三个二选一多路选择器和一个或门组成,是一个有8个 输入一个输出的电路,它可实现两输入、三输入和四输入的与、 或门、与非、或非门、与或门、或与门等,也可实现D型锁存器, 用两个模块可实现各种类型的D触发器。

19

九、 FPGA内部的时钟网络

• FPGA内部的时钟网络

– 为时序电路提供大驱动能力、时钟歪斜小的 时钟,或者用作大驱动全局信号,如:reset, output,select signal。

– 具有时钟网络是实现同步设计的基础。

• 时钟网络数:

1:A40MX02 2:A42MX24 3:A54SX32A

fpga中的mlab资源

fpga中的mlab资源FPGA中的MLAB资源FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,它能够在硬件级别上实现逻辑功能。

在FPGA中,MLAB (Memory Logic Array Block)是一种重要的资源,它提供了可编程的存储器单元。

本文将介绍FPGA中的MLAB资源的特点、用途以及如何合理利用它们。

一、MLAB资源的特点MLAB是FPGA中的存储器资源,具有以下特点:1. 可编程性:MLAB资源可以根据设计需求进行编程,实现不同的存储器结构和功能。

2. 高密度:FPGA中的MLAB资源具有较高的存储密度,可以存储大量的数据。

3. 高速性能:MLAB资源具有快速的读写速度和响应时间,可以满足对存储器性能要求较高的应用场景。

4. 低功耗:MLAB资源在实现存储器功能的同时,具有较低的功耗特性,可以节省整个FPGA系统的能量消耗。

二、MLAB资源的应用领域MLAB资源在FPGA中的应用非常广泛,主要包括以下几个领域:1. 数据存储:MLAB资源可以用作FPGA内部的数据存储器,用于存储中间结果、配置信息等。

2. 缓存存储:MLAB资源可以用作缓存存储器,提高数据访问的效率,减少外部存储器的访问延迟。

3. 高速缓冲:MLAB资源可以用作高速缓冲存储器,提供数据的临时存储和快速访问,加快数据处理速度。

4. FIFO(First In, First Out):MLAB资源可以用作FIFO缓冲区,实现数据的有序存储和读取,解决数据传输速率不匹配的问题。

5. 内存控制器:MLAB资源可以用作内存控制器,管理FPGA系统中的外部存储器,实现数据的读写操作。

三、合理利用MLAB资源的方法为了充分利用FPGA中的MLAB资源,以下几点是值得注意的:1. 合理划分资源:根据设计需求和数据存储规模,合理划分MLAB 资源的大小和数量。

过多或过少的MLAB资源都会导致资源浪费或不足,影响系统性能。

FPGA设计中的资源优化策略

FPGA设计中的资源优化策略

在FPGA(现场可编程门阵列)设计中,资源优化策略是非常重要的。

在设计过程中,经常会遇到资源不足的问题,因此需要采取一些策略来优化资源的利用,以实现设计的最佳性能和效率。

首先,对于FPGA设计中资源的优化,需要考虑到逻辑资源、存储资源和时序资源。

逻辑资源是指FPGA中可用的逻辑单元,存储资源是指FPGA中可用的存储单元,时序资源是指设计在FPGA中的时钟周期。

在优化逻辑资源方面,可以采取逻辑综合和优化编码的方法,减少逻辑门数量,简化逻辑电路结构,从而节省FPGA中的逻辑资源。

其次,针对存储资源的优化,可以采取存储资源共享和优化存储器的方法。

存储资源共享是指多个模块共享同一个存储器,减少存储器的使用,从而节省存储资源。

优化存储器是指采取合适的存储器类型,如RAM、ROM等,以及设计有效的存储器结构,提高FPGA中存储资源的利用率。

最后,在时序资源的优化方面,可以采取时序约束和时序优化的方法。

时序约束是指给出设计中各个时序参数的限制,如时钟频率、时钟间隔等,保证设计在FPGA中能够满足时序要求。

时序优化是指通过合理的时序设计,减小时序路径的延迟,提高FPGA中时序资源的利用率。

总的来说,对于FPGA设计中的资源优化策略,需要综合考虑逻辑资源、存储资源和时序资源的优化方法,合理设计电路结构和时序约束,以提高FPGA设计的性能和效率。

通过有效的资源优化策略,可以充分利用FPGA中的资源,实现设计的最佳性能和效率。

希望以上介绍对您有所帮助,如有任何疑问,请随时与我联系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

fpga内部可用资源

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,内部集成了大量的可用资源,包括逻辑单元、寄存器、存储器等。

本文将分别介绍FPGA内部的这些可用资源。

1. 逻辑单元:FPGA内部包含大量的逻辑单元(Logic Element),用于实现各种逻辑功能。

逻辑单元通常由多个逻辑门组成,可以实现与、或、非、异或等逻辑运算。

逻辑单元可以根据需要进行编程,以实现不同的功能。

2. 寄存器:FPGA内部还包含大量的寄存器(Register),用于存储数据和状态信息。

寄存器可以存储单个数据位或多个数据位,并且可以进行读写操作。

寄存器的数量和位宽可以根据设计需求进行配置。

3. 存储器:FPGA内部还集成了各种类型的存储器,包括片上存储器(On-chip Memory)和外部存储器接口(External Memory Interface)。

片上存储器通常用于存储中间数据和程序代码,具有较快的访问速度和较小的延迟。

外部存储器接口可以连接外部存储器芯片,用于存储大容量的数据。

4. 数字信号处理器(DSP):FPGA内部还集成了一定数量的数字信号处理器(DSP),用于实现高性能的数字信号处理功能。

DSP可以进行复杂的算术运算和滤波操作,以满足各种信号处理需求。

5. 时钟管理器:FPGA内部还包含时钟管理器(Clock Manager),用于生成和分配时钟信号。

时钟信号是FPGA设计中至关重要的一部分,时钟管理器可以根据设计需求生成多个时钟信号,并对时钟进行分频、倍频等操作。

6. 通信接口:FPGA内部还提供了多种通信接口,包括UART、SPI、I2C、PCI Express等。

这些接口可以与外部设备进行数据交互,实现与外界的通信功能。

7. 乘法器:FPGA内部还集成了大量的乘法器(Multiplier),用于实现乘法运算。

乘法器可以进行定点数和浮点数的乘法运算,具有较高的计算效率和精度。

8. 时序管理器:FPGA内部还包含时序管理器(Timing Manager),用于实现时序控制和时序优化。

时序管理器可以对设计进行时序分析,优化时序路径,以满足设计的时序要求。

9. 电源管理器:FPGA内部还集成了电源管理器(Power Manager),用于对芯片的供电进行管理和控制。

电源管理器可以实现电源的开关、电压的调整等功能,以提供合适的电源供给。

10. 配置存储器:FPGA内部还包含配置存储器(Configuration Memory),用于存储FPGA的配置信息。

配置存储器可以存储逻辑电路的连接关系和功能实现方式,通过加载不同的配置信息,可以

实现不同的功能。

FPGA内部包含了丰富的可用资源,包括逻辑单元、寄存器、存储器、数字信号处理器、时钟管理器、通信接口、乘法器、时序管理器、电源管理器和配置存储器等。

这些资源可以根据设计需求进行配置和编程,实现各种复杂的逻辑功能和数字信号处理功能。

FPGA 的灵活性和可编程性使其在各种应用领域中得到广泛应用。