6264与51单片机扩展

单片机原理与应用 习题答案

习题解答第三章3-1 已知A=7AH,R0=30H(30H=A5H),PSW=80H,SP=65H,试分析下面每条指令的执行结果及对标志位的影响。

(1)ADD A,@R0;01111010+=1,00011111,(A)=1FH,Cy=1 ,AC=0,OV=0,P=1(2)ADD A,#30H;01111010+00110000=,(A)=AAH,Cy=0,AC=0,OV=1,P=0 (3)ADDC A,30H;01111010++1=1,00100000,(A)=20H,Cy=1,AC=1,OV=0,P=1(4)SUBB A,@R0;0101-1=1,,(A)=D4H,Cy=1,AC=0,OV=1,P=0(5)DA A;01111010+00000110=,(A)=80H,Cy=0,其他无变化(6)RLC A;(A)=B=F5H,Cy=0,AC=0,OV=0,P=0(7)RR A;(A)=00111101B=3DH,Cy=1,AC=0,OV=0,P=1《(8)PUSH 30H;SP=66H,(66H)=A5H(9)POP B;SP=64H,(B)=(65H)(10)XCH A,@R0;(A)=A5H,(30H)=7AH,Cy=1,OV=0,AC=0,P=0 3-4 试分析在执行完下面的程序段后,A,R0,R1,R7,SP以及片内RAM的一些单元中内容各是什么MOV SP,#65HMOV R7,#5MOV R0,#30HMOV R1,#40HLOOP:MOV A,@R1PUSH ACC$MOV A,@R0MOV @R1,AINC R0INC R1DJNZ R7,LOOP结果:(A)=(34H),(R0)=34H,(R1)=44H,(R7)=0,SP=70H ,(70H)=(44H),(30H)=(40H),…(34H)=(44H)。

3-5 已知SP=62H,(62H)=50H,(61H)=30H,问执行指令RET后,PC=,SP=并解释。

单片机大题

单片机模拟试卷001五、作图题(10分)用6264(8K*8)构成16K的数据存储系统。

要求采用线选法产生片选信号,并计算6264的地址范围。

答:WR接6264的WERD接6264的OEAB0---AB12接6264的A0---A12DB0—DB7接6264的D0—D7AB15、AB14分别接Y0和Y1地址:0000H---1FFFH;2000H---3FFFH六、设计题1.某单片机控制系统有8个发光二极管。

试画出89C51与外设的连接图并编程使它们由右向左轮流点亮。

答:图(5分) 构思(3分)MOV A,#80H (1分)UP:MOV P1,A (1分)RR A (2分)SJMP UP (1分)2.某控制系统有2个开关K1和K2,1个数码管,当K1按下时数码管加1,K2按下时数码管减1。

试画出8051与外设的连接图并编程实现上述要求。

答:图(5分) 构思(3分)程序(4分)ORG 0000HLJMP MAINORG 0003HLJMP AINT0ORG 0013HLJMP BINT1MAIN: MOV IE,#83HSETB IT0SETB IT1MOV R0,#00HMOV DPTR,#TABUP: MOV A,R0MOVC A,@A+DPTRMOV P1,ASJMP UPAINT0: INC R0CJNE R0,#10,AINT01MOV R0,#0AINT01: RETIBINT1: DEC R0CJNE R0,#0FFH,BINT11MOV R0,#9BINT11: RETI单片机模拟试卷002五、编程题(每小题4分,共20分)1.已知在累加器A中存放一个BCD数(0~9),请编程实现一个查平方表的子程序。

SQR:1NC AMOVC A,@A+PCRETTAB:DB 0,1,4,9,16DB 25,36,49,64,812.请使用位操作指令实现下列逻辑操作:BIT=(10H∨P1.0)∧(11H∨C Y)ORL C,11HMOV 12H,CMOV C,P1.0ORL C,/10HANL C,12HMOV BIT,CRET3.已知变量X存于V AR单元,函数值Y存于FUNC单元,按下式编程求Y值。

项目 一 汽车单片机原理应用(任务五 MCS-51单片机系统扩展)

(3) MCS-51单片机系统地址空间的分配 系统空间分配:通过适当的地址线产生各外部扩展器件的片 选/使能等信号就是系统空间分配。

编址:编址就是利用系统提供的地址总线,通过适当的连接, 实现一个编址惟一地对应系统中的一个外围芯片的过程。编 址就是研究系统地址空间的分配问题。

片内寻址:若某芯片内部还有多个可寻址单元,则称为片内 寻址。

2)全地址译码法

利用译码器对系统地址总线中未被外扩芯片用到的高位 地址线进行译码,以译码器的输出作为外围芯片的片选信 号。常用的译码器有:74LS139,74LS138,74LS154等。 优点是存储器的每个存储单元只有惟一的一个系统空间地 址,不存在地址重叠现象;对存储空间的使用是连续的, 能有效地利用系统的存储空间。缺点是所需地址译码电路 较多,。全地址译码法是单片机应用系统设计中经常采用 的方法。

1。程序和数据之和不大于 存储器总容量。 2。程序必须存放在低地址,

数据存放在高地址。

三、并行I/O口扩展 MCS-51单片机具有四个并行8位I/O口原理均可用做双向并行 I/O接口,但在实际应用中,可提供给用户使用的I/O口只有P1 口和部分P3口线及作为数据总线用的P0口。在单片机的I/O口 线不够用的情况下,可以借助外部器件对I/O口进行扩展 (1)概述 1)单片机I/O口扩展方法 并行I/O口扩展的目的:为外围设备提供一个输入输出通道。 ①并行总线扩展的方法 ②串行口扩展方法(只介绍总线扩展方式下I/O接口扩展方法) ③I/O端口模拟串行方法

二、存储器的扩展 存储器是计算机系统中的记忆装置,用来存放要运行的程 序和程序运行所需要的数据。单片机系统扩展的存储器可分为 程序存储器和数据存储器两种类型。

(1)MCS-51单片机对外部存储器的扩展应考虑的问题

MCS51单片机总线系统与IO口扩展

6.2.2 单片机总线扩展的编址技术

OE

LE

Dn

Qn

L

H

H

H

L

H

L

L

L

L

L

Qn-1

L

L

H

Qn-1

H

×

×

Z

地址锁存器74LS373

CLR D0-D7Q0-Q7 4 6 2 6 74LS24474LS273 E 0123456789E GG 12Q0-Q7CLKD0-D7AAAAAAAAAAA10A11A12I/O0I/O1I/O2I/O3I/O4I/O5I/O6I/O7OWCE1CE2 56? UUU P0.0-P0.7P0.0-P0.7 +5V 11 01234567 E >> QQQQQQQQ O 01234567 E DDDDDDDDL 2 U74LS373 012 YYY ABC 3 U74LS138 R AD E R P20P07P21P06P22P05P23P04P24P03P25P02P26P01P27P00 W ALE 89C51 1 U

MOV

DPTR,#0FEFFH ;确定扩展芯片地址

MOVX

A,@DPTR

;将扩展输入口内容读入累加器A

当与74LS244相连的按键都没有按下时,输入全为1,若按下某键,则所在线 输入为0。

6.2.1 单片机I/O口扩展

输出控制信号由P2.0和相“或”后形成。当二者都为0后,74LS273的控制端 有效,选通74LS273, P0上的数据锁存到74LS273的输出端,控制发光二极管 LED , 芯 片 地 址 与 74LS244 的 选 通 地 址 相 同 ( 都 是 ×××× ×××0 ×××× ××××B,通常取为FEFFH)。当某线输出为0时,相应的LED发 光。

四 MCS-51单片机存储器系统扩展

74LS373引脚

1、控制位OE: OE=0时,输出导通 2、控制位G: 接ALE 3、Vcc=+5V 4、GND接地

1 74LS373为8D锁存器,其主要特点在于:

控制端G为高电平时,输出Q0~Q7复现输入D0~ D7的状态;G为下跳沿时D0~D7的状态被锁存在Q0 ~Q7上。

MOV DPTR, #0BFFFH ;指向74LS373口地址

MOVX A, @DPTR ;读入

MOV @R0, A

;送数据缓冲区

INC R0

;修改R0指针

RETI

;返回

用74LS273和74LS244扩展输入输出接口

地址允许信号ALE与外部地址锁存信号G相连;

单片机端的EA与单片机的型号有关;

存储器端的CE与地址信号线有关。

P... 2.7 P2.0

ALE 8031

P... 0.7 P0.0

EA

PSEN

外部地址

G

锁存器

I...7

O... 7

I0 O0

A... 15

CE

A8

外部程序

存储器

A... 7 A0

D7. . . D0 OE

6264的扩展电路图

图中CS(CE2)和CE引脚均为6264的片选信号,由于该扩展电路 中只有一片6264,故可以使它们常有效,即CS(CE2)接+5V ,CE接地。6264的一组地址为0000H~1FFFH。

存储器地址编码

SRAM6264:“64”—— 8K×8b = 8KB 6264有13根地址线。 地址空间: A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 最低地址: 0 0 0 0 0 0 0 0 0 0 0 0 0 0000H 最高地址: 1 1 1 1 1 1 1 1 1 1 1 1 1 1FFFH MCS-51单片机寻址范围:64KB 26×210 = 216即16位地址线 地址空间: A15A14A13A12A11A10A9A8A7······A0 单片机

5、6264

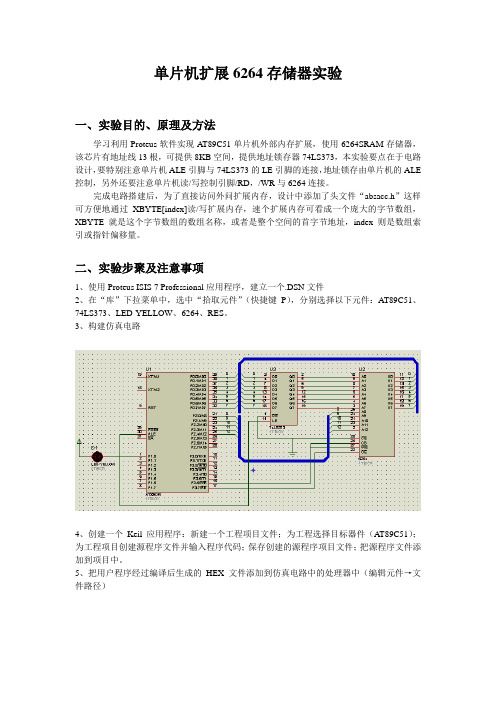

单片机扩展6264存储器实验一、实验目的、原理及方法学习利用Proteus软件实现A T89C51单片机外部内存扩展,使用6264SRAM存储器,该芯片有地址线13根,可提供8KB空间,提供地址锁存器74LS373,本实验要点在于电路设计,要特别注意单片机ALE引脚与74LS373的LE引脚的连接,地址锁存由单片机的ALE 控制,另外还要注意单片机读/写控制引脚/RD,/WR与6264连接。

完成电路搭建后,为了直接访问外问扩展内存,设计中添加了头文件“absacc.h”这样可方便地通过XBYTE[index]读/写扩展内存,速个扩展内存可看成一个庞大的字节数组,XBYTE就是这个字节数组的数组名称,或者是整个空间的首字节地址,index则是数组索引或指针偏移量。

二、实验步聚及注意事项1、使用Proteus ISIS 7 Professional应用程序,建立一个.DSN文件2、在“库”下拉菜单中,选中“拾取元件”(快捷键P),分别选择以下元件:AT89C51、74LS373、LED-YELLOW、6264、RES。

3、构建仿真电路4、创建一个Keil应用程序:新建一个工程项目文件;为工程选择目标器件(A T89C51);为工程项目创建源程序文件并输入程序代码;保存创建的源程序项目文件;把源程序文件添加到项目中。

5、把用户程序经过编译后生成的HEX文件添加到仿真电路中的处理器中(编辑元件→文件路径)三、实验仪器电路一台Proteus ISIS 7 Professional应用程序Keil应用程序四、数据记录及处理#include<reg51.h>#include<absacc.h>#define uchar unsigned charsbit LED=P1^0;void main(){uchar i;LED=1;for(i=0;i<200;i++){XBYTE[i]=i+1;}for(i=0;i<200;i++){XBYTE[i+0x0100]=XBYTE[199-i];}LED=0;while(1);}五、结果分析如果是多片6264进行扩展,并在其中使用74LS138译码器,请分析整个的电路形势,并划分内存地址的分配。

第9章 80C51单片机系统扩展技术

15

9.2.2 地址锁存器芯片

1. 锁存器74LS373

74LS373的结构及引脚

04:17

16

2. 锁存器8282

功能及内部结构与74LS373完全一样,只是其引脚的排列与 74LS373不同 ,8282的引脚如下图。

04:17

17

引脚的排列为绘制印刷 电路板时的布线提供了方便。

04:17

18

04:17

10

地址总线(AB): 由P2口提供高8位地址线, 此口具有输出锁存 的功能, 能保留地址信息。 由P0口提供低8位地址线。

数据总线(DB): 由P0口提供。 此口是双向、 输入三态控制的 8位通道口。

控制总线(CB): 扩展系统时常用的控制信号为:

ALE——地址锁存信号, 用以实现对低8位地址的锁存。

04:17

13

9.2.1 数据存储器芯片

典型型号有:6116、6264、62128、62256。+5V电源供电, 双列直插,6116为24引脚封装,6264、62128、62256为28 引脚封装。

6116:2KB 6264:8KB 62128:16KB 62256:32KB

04:17

14

04:17

3. 锁存器74LS573

输入的D端和输出的Q端也是依次排在芯片的两侧,与锁存 器8282一样,为绘制印刷电路板时的布线提供了方便。

04:17

19

9.2.3 数据存储器的扩展电路

需要考虑与80C51相连的存储芯片引脚:

80C51 CPU

存储芯片

(1)地址总线P0.0-P0.7 74LS373 (2)地址总线P2.0-P2.n-9 (3)数据总线的P0.0-P0.7

第6章 MCS-51单片机系统扩展技术

6.3 数据存储器扩展

6.3.1 静态RAM扩展电路

6.3.2 动态RAM扩展电路

返回本章首页

6.3.1 静态RAM扩展电路

常用的静态RAM芯片有6116,6264,62256等,其 管脚配置如图6-13所示。

1.6264静态RAM扩展 额定功耗200mW,典型存取时间200ns,28脚双列直插 式封装。表6-1给出了6264的操作方式,图6-14为6264静 态RAM扩展电路。

图 6 9

A EEPROM

28 17

扩 展 电 路

写入数据

不是指令

查询 中断 延时

2.2864A EEPROM 扩展

2864A有四种工作方式: (1)维持方式 (2)写入方式 (3)读出方式 (4)数据查询方式

图 6 12

28 64

返回本节

A EEPROM

扩 展 电 路

串行E2PROM简介 串行E2PROM占用引线少、接线简单,适用于作为数据存储 器且保存信息量不大的场合。 以AT93C46/56/57/66为例,它是三线串行接口E2PROM, 能提供128×8、256×8、512×8或64×16、128×16、256×16 位,具有高可靠性、能重复擦写100,000次、保存数据100年 不丢失的特点,采用8脚封装。

第6章 MCS-51单片机系统扩展技术

6.1 MCS-51单片机系统扩展的基本概念

6.2 程序存储器扩展技术

6.3 数据存储器扩展 6.4 输入/输出口扩展技术

T0 T1

时钟电路

ROM

RAM

定时计数器

CPU

并行接口 串行接口 中断系统

P0 P1 P2 P3

TXD RXD

INT0 INT1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Intel6264芯片

单片机内存扩展6264芯片

2012-5-2

1.Intel6264芯片

Intel 6264的特性及引脚信号Intel 6264的容量为8KB,是28引脚双列直插式芯片,采用CMOS工艺制造

A12~A0(address inputs):地址线,可寻址8KB的存储空间。

D7~D0(data bus):数据线,双向,三态。

OE(output enable):读出允许信号,输入,低电平有效。

WE(write enable):写允许信号,输入,低电平有效。

CE1(chip enable):片选信号1,输入,在读/写方式时为低电平。

CE2(chip enable):片选信号2,输入,在读/写方式时为高电平。

VCC:+5V工作电压。

GND:信号地。

Intel 6264的操作方式Intel 6264的操作方式由, CE1 , CE2的共同作用决定

②读出:当和CE1为低电平,且和CE2为高电平时,数据输出缓冲器选通,被选中单元的数据送到数据线D7~D0上。

2.

74LS373

有54S373 和74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号TPD PD 54S373/74S373 7ns 525mW 54LS373/74LS373 17ns 120mW 373 的输出端O0~O7 可直接与总线相连。

当三态允许控制端OE 为低电平时,Q0~Q7为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,Q0~Q7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,Q 随数据D 而变。

当LE 为低电平时,D 被锁存在已建立

的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

引出端符号:D0~D7 数据输入端OE 三态允许控制端(低电平有效)LE 锁存允许端Q0~Q7 输出端真值表:DnLEOEOnHHLHLHLLXLLQ0XXH高阻

态

作用;:首先将数据存入6264中,然后复制到0x0100内存区中,并用led显示数据。

LED_BIRY为读取结束指示灯。

总结:1.单片机中ALE是什么意思输出振荡器的六分之一频率的脉冲,可供给外部芯片做时钟Address lock enable . 地址锁存允许端。

访问外部存储器用的,比如RAM、ROM51有外部总线,16位的地址线,8为的数据线,但是地址的低8位跟数据线是重合的,因此访问的时候需要区分开低8位(P0口,高8位是P2口)地址和数据,这就需要用到ALE信号了。

访问存储器的时候,P2口输出高地址,P0输出低地址。

利用外部的锁存器(一般用74LS373)配合ALE脉冲,锁存P0地址,这时候读写信号开始起作用(WR或者RD),P0口读入或者输出数据。

在整个过程中,外部存储器的地址总线上的数据始终是稳定的,低8位地址的稳定靠的就是ALE和外部锁存器。

现在的51一般都很少用外部存储器或者相似的使用外部总线的外设可,因此现在的51单片机大多数都可以软件设置ALE脉冲的使能,由用户决定是否输出ALE脉冲,一来是降低EMI,二来是可以多一个IO口(如果ALE是复用的话)2.。