51单片机接口的扩展

合集下载

第4章MCS-51单片机系统功能扩展

74LS373结构示意图

74LS373的引脚

引脚说明如下: D7~D0: 8位数据输入端。 Q7~Q0: 8位数据输出端。 G:数据输入锁存控制端:当G为“1” 时,锁存器 输出端与输入端数据相同;当G由“1” 变“0” 时,数据输入锁存器中。 OE#: 输出允许端。

P0口与地址锁存器74LS373的连接

4.1 系统扩展概述

4.1.1 最小应用系统

图4.1 MCS–51单片机最小化系统 (a) 8051/8751最小系统结构图;(b) 8031最小系统结构图

4.1.2 单片机系统扩展的内容与方法

1.单片机的三总线结构

图4.2 MCS–51单片机的三总线结构形式

(1)以P0口作为低8位地址/数据总线。 (2)以P2口的口线作高位地址线。 (3)控制信号线。 *使用ALE信号作为低8位地址的锁存控制信号。 *以PSEN#信号作为扩展程序存储器的读选通信号。 *以EA#信号作为内外程序存储器的选择控制信号。 *由RD#和WR#信号作为扩展数据存储器和I/O口的 读选通、写选通信号。 尽管MCS-51有4个并行I/O口,共32条口线,但由于系 统扩展需要,真正作为数据I/O使用的,就剩下P1 口和P3口的部分口线。

锁存器8282 功能及内部结构与74LS373完全一样,只是其引脚的排 列与74LS373不同 ,8282的引脚如下图。

4.2.2 74LS244和74LS245芯片

在单片机应用系统中, 扩展的三总线上挂接

很多负载, 如存储器、并行接口、A/D接口、显

示接口等, 但总线接口的负载能力有限, 因此常

3) 采用地址译码器的多片程序存储器的扩展

例3 要求用2764芯片扩展8031的片外程序存储器,分配的 地址范围为0000H~3FFFH。

第7章MCS-51单片机的常用外设扩展

(2)数据线

2732的8位数据线直接与单片机的P0口相连。P0口作 为地址/数据线分时复用。

(3)控制线

CPU执行2732中存放的程序指令时,取指阶段就是对 2732进行读操作。注意,CPU对EPROM只能进行读操作, 不能进行写操作。CPU对2732的读操作控制都是通过控制线 实现的。2732控制线的连接有以下几条:

2.硬件电路 单片机与6116的硬件连接如图7-4所示。

3.连线说明

• 地址线:A0~A10连接单片机地址总线P0.0~P0.7、P2.0、P2.1、P2.2 共11根;

• 数据线:I/O0~I/O7连接单片机的数据线,即P0.0~P0.7;

• 控制线:片选端连接单片机的P2.7,即单片机地址总线的最高位A15; 读允许线连接单片机的读数据存储器控制线;

• 对于没有内部ROM的单片机或者程序较长、片内ROM容 量不够时,用户必须在单片机外部扩展程序存储器。 MCS-51单片机片外有16条地址线,即P0口和P2口,因此 最大寻址范围为64K字节(0000H—FFFFH)。

• 这里要注意的是,MCS-51单片机有一个管脚 EA跟程序存 储器的扩展有关。如果接高电平,那么片内存储器地址范 围是0000H—0FFFH(4K字节),片外程序存储器地址范 围是1000H—FFFFH(60K字节)。如果接低电平,不使 用片内程序存储器,片外程序存储器地址范围为0000H— FFFFH(64K字节)。

1. 芯片选择

单片机扩展数据存储器常用的静态RAM芯片有6116(2K×8 位)、6264(8K×8位)、62256(32K×8位)等。

根据题目容量的要求我们选用SRAM6116,采 用单一+5V供电,输入输出电平均于TTL兼容,具有 低功耗操作方式,管脚如图7-3所示。

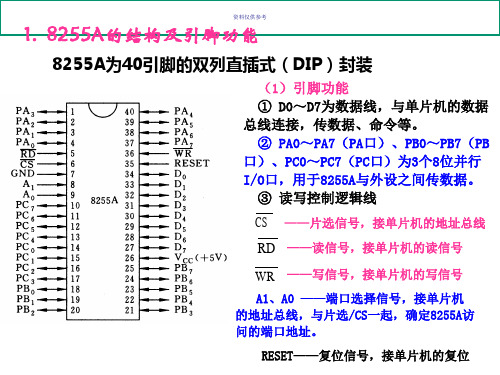

51单片机8255A扩展IO口和单片机连接

PC4

PB口

PC5 PC6

PC7

PC口低4位

14

15

16

17

13 RD

12 11 10

WR A0

A1

RESET

读写 控制 逻辑

B组 控制

③ 读/写控制逻辑

CS

接收CPU传来的控制信号,以控制8255A的操作

CS WR A1、A0 、RESET

④ 数据总线缓冲器 双向三态8位缓冲器,与单片机的数据总线直接相连

8031

8255A与资料单仅供片参考 机的连接

D7

Q7

D6

Q6

74LS373

D5

Q5

D4

Q4

D3 Q3

D2

Q2

D1

Q1

D0

Q0

G OE

WR

RD RESET PA CS

8255A

A1 A0

PB

ALE EA

D7

D6

D5

D4

PC

D3

D2

D1

D0

CS 、A1、A0接地址总线

P0.7、P0.1、P0.0经锁存器74LS373接 CS 、A1、A0

控制

数据 总线

5

② A、B组控制电路 36 9 8 A、B两组控制电路将三个端口 35

分成A、B两组。 6

RD

PB0

WR 8255A PB1

A0

PB2

A1

PB3

RESET

PB4

CS

PB5

PB6

PB7

18 19

D0-D7

20

21

22

23

24

25

缓冲

单片机io口扩展技术详解

单片机io口扩展技术详解

单片机如何扩展IO口?

首先我们先讲讲为什幺要扩展IO口。

在我们使用51单片机的时候,有时候会出现IO口不够用的情况。

比如键盘!这个时候IO口的资源就十分有限了。

按键是我们常用的器件,做某些东西的时候又不能缺少按键。

如果一个按键对应一个IO口,那幺可想而知,按键所占的IO口的数量是很大的。

单片机IO口的资源是有限的,因此我们要采取一些方法来扩展单片机的IO 口,控制按键所占的单片机IO口。

下面有几种方法可以扩展单片机的IO口:

1. 通过数据缓存器、锁存器来扩展单片机IO口。

这里采用74HC164来扩展单片机IO口。

MCS51单片机总线系统与IO口扩展

6.2.2 单片机总线扩展的编址技术

OE

LE

Dn

Qn

L

H

H

H

L

H

L

L

L

L

L

Qn-1

L

L

H

Qn-1

H

×

×

Z

地址锁存器74LS373

CLR D0-D7Q0-Q7 4 6 2 6 74LS24474LS273 E 0123456789E GG 12Q0-Q7CLKD0-D7AAAAAAAAAAA10A11A12I/O0I/O1I/O2I/O3I/O4I/O5I/O6I/O7OWCE1CE2 56? UUU P0.0-P0.7P0.0-P0.7 +5V 11 01234567 E >> QQQQQQQQ O 01234567 E DDDDDDDDL 2 U74LS373 012 YYY ABC 3 U74LS138 R AD E R P20P07P21P06P22P05P23P04P24P03P25P02P26P01P27P00 W ALE 89C51 1 U

MOV

DPTR,#0FEFFH ;确定扩展芯片地址

MOVX

A,@DPTR

;将扩展输入口内容读入累加器A

当与74LS244相连的按键都没有按下时,输入全为1,若按下某键,则所在线 输入为0。

6.2.1 单片机I/O口扩展

输出控制信号由P2.0和相“或”后形成。当二者都为0后,74LS273的控制端 有效,选通74LS273, P0上的数据锁存到74LS273的输出端,控制发光二极管 LED , 芯 片 地 址 与 74LS244 的 选 通 地 址 相 同 ( 都 是 ×××× ×××0 ×××× ××××B,通常取为FEFFH)。当某线输出为0时,相应的LED发 光。

CPLD扩展MCS-51单片机I/O接口的应用研究

成 电路 , 而给 电子系 统 设计 带米 了革命性 的变 从

2 设计要 求

设计任 务:要检 测或 执行的系 统 的外 围 I / o 状态较 多 ,而 MC 一 1 片机 的 I 接 口不足 。 S5 单 / O

器 什 选 择 : Alr 公 司 ta e MA 0 0 系 列 X7 0

标准 的数字 电路硬件 描述语 言 。而 V ro eig语言 l 是一种 很接近 C语 言 的数 字 电路硬件 描述 语言 , 只 要有 一些数字 电路和 C 语言 基础 ,就很容 易

掌握。 本文 介绍采 刖 V ro 言来扩 展 MC . l ei g语 l S5 单 片机接 口的一种 方法 。

MAX 18 (/ 引脚数 10 。 7 2S I 0 O)

Alr 可 编程器件 有很 多优 点:高性能 ,采 ta e

用C OMS技 术 ,具有低功 耗和 高速度 ;高密度

逻辑 集成 , tr 器 : 从 3 0门到 10万 r , Al a e 密度 0 0 J

使 传统 的 “自下 而上 ”的设计方法 ,变为一种 新 的 “自顶 向下 ”的 设计 方 法 。CP D 采 刖 了 L EC 2 MOS工艺 制作 。相 比于 E L 增 加 内部 连 PD

摘

要

CL P D是一种复杂可编程序逻辑 器件 ,广泛应用于 大规模 集成 电路的 系统设计 中。利用 X X A

P U 集成 环 境 , 可 以很 方 便 地 进 行硬 件 描 述语 言 的程 序 编 辑 L SI I

关键词

可编程逻辑器件 硬件描述语 言 单 片机 I0 口 /接

0 前 言 C L 是 具 备在 系统 可编 能 力 的复杂 可 PD

能集成 现有 的逻 辑器 件 ;开发 周期 短。快速 、直

2 设计要 求

设计任 务:要检 测或 执行的系 统 的外 围 I / o 状态较 多 ,而 MC 一 1 片机 的 I 接 口不足 。 S5 单 / O

器 什 选 择 : Alr 公 司 ta e MA 0 0 系 列 X7 0

标准 的数字 电路硬件 描述语 言 。而 V ro eig语言 l 是一种 很接近 C语 言 的数 字 电路硬件 描述 语言 , 只 要有 一些数字 电路和 C 语言 基础 ,就很容 易

掌握。 本文 介绍采 刖 V ro 言来扩 展 MC . l ei g语 l S5 单 片机接 口的一种 方法 。

MAX 18 (/ 引脚数 10 。 7 2S I 0 O)

Alr 可 编程器件 有很 多优 点:高性能 ,采 ta e

用C OMS技 术 ,具有低功 耗和 高速度 ;高密度

逻辑 集成 , tr 器 : 从 3 0门到 10万 r , Al a e 密度 0 0 J

使 传统 的 “自下 而上 ”的设计方法 ,变为一种 新 的 “自顶 向下 ”的 设计 方 法 。CP D 采 刖 了 L EC 2 MOS工艺 制作 。相 比于 E L 增 加 内部 连 PD

摘

要

CL P D是一种复杂可编程序逻辑 器件 ,广泛应用于 大规模 集成 电路的 系统设计 中。利用 X X A

P U 集成 环 境 , 可 以很 方 便 地 进 行硬 件 描 述语 言 的程 序 编 辑 L SI I

关键词

可编程逻辑器件 硬件描述语 言 单 片机 I0 口 /接

0 前 言 C L 是 具 备在 系统 可编 能 力 的复杂 可 PD

能集成 现有 的逻 辑器 件 ;开发 周期 短。快速 、直

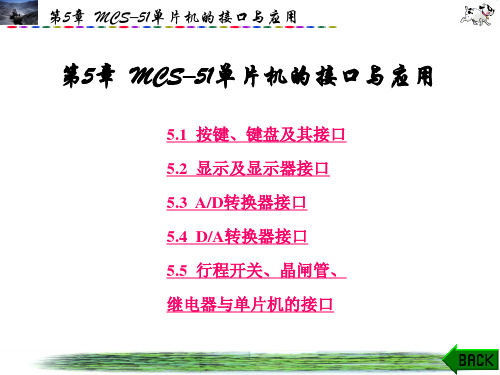

第5章 MCS–51单片机的接口与应用 99页 5.8M

(1) 用键盘连接的I/O线的二进制组合表示键码。例如用4行、

4列线构成的16个键的键盘,可使用一个8位I/O口线的高、低4 位口线的二进制数的组合表示16个键的编码,如图5.4(a)所示。 各键相应的键值为88H、84H、82H、81H、48H、44H、42H、 41H、28H、24H、22H、21H、18H、14H、12H、11H。这种键 值编码软件较为简单直观,但离散性大,不便安排散转程序的 入口地址。

第5章 MCS–51单片机的接口与应用 JNB ACC.2,K2 JNB ACC.3,K3 JNB ACC.4,K4 JNB ACC.5,K5 JNB ACC.6,K6 ;检测2号键是否按下,按下转 ;检测3号键是否按下,按下转 ;检测4号键是否按下,按下转 ;检测5号键是否按下,按下转 ;检测6号键是否按下,按下转

;0号键功能程序

;0号键功能程序执行完返回 ;0号键功能程序

JMP START

……………………… PROM7: ……………………… JMP START …

;1号键功能程序执行完返回

;7号键功能程序 ;7号键功能程序执行完返回

第5章 MCS–51单片机的接口与应用

5.1.4 行列式键盘

行列式键盘又叫矩阵式键盘。用I/O口线组成行、列结构, 按键设置在行列的交点上。例如4×4的行列结构可组成16个键 的键盘。因此,在按键数量较多时,可以节省I/O口线。 1.行列式键盘的接口 行列式键盘的接口方法有许多,例如直接接口于单片机的 I/O口上;利用扩展的并行I/O接口;用串行口扩展并行I/O口接 口;利用一种可编程的键盘、显示接口芯片8279进行接口等。 其中,利用扩展的并行I/O接口方法方便灵活,在单片机应用系

MOVX @DPTR,A

内容7_MCS-51单片机IO接口扩展设计及应用

C.为了消除按键的抖动,常用的方法有硬件和软件两种方法;

D. 8031的扩展储存器系统中,P0口要接一个8位锁存器,而P2口却不需要。

17

下面的说法错误的有()。

A. LED显示器采用动态扫描方法进行显示,任一时刻只有一位显示器被点亮;

B. RS-232C的逻辑电平与通常的TTL和MOS电平兼容,故实现与TTL或MOS电路的连接时无需外加电平转换电路;

(B)RAM式

(C)FLASHROM

(D)EPROM

47

某种存储器芯片是8KB*4/片,那么它的地址线根数是()。

(A)11根

(B)12根

(C)13根

(D)14根

48

若某存储器芯片地址线为12根,那么它的存储容量为()。

(A)1KB

(B)2KB

(C)4KB

(D)8KB

49

下面哪条指令产生信号()。

(A)MOVXA,@DPTR

D.P3

E.P0.7

28

MCS-51单片机的P0口可以作为( )使用。

A.低8位地址总线

B.高8位地址总线

C.数据总线

D.控制总线

E.一般的I/O使用

29

071-0029、ATMEL公司的AT24CXX系列EEPROM是()。

A.I C接口的EEPROM

B.SPI接口的EEPROM

C.并行接口的EEPROM

A.16D触发器

B.8D触发器

C.32位锁存器

D.16位锁存器

E.8位锁存器

15

071-0001、单片机扩展的内容有()等。

A.总线扩展

B.程序存储器扩展

C.数据存储器扩展

D.外围扩展

E.I/O口的扩展

D. 8031的扩展储存器系统中,P0口要接一个8位锁存器,而P2口却不需要。

17

下面的说法错误的有()。

A. LED显示器采用动态扫描方法进行显示,任一时刻只有一位显示器被点亮;

B. RS-232C的逻辑电平与通常的TTL和MOS电平兼容,故实现与TTL或MOS电路的连接时无需外加电平转换电路;

(B)RAM式

(C)FLASHROM

(D)EPROM

47

某种存储器芯片是8KB*4/片,那么它的地址线根数是()。

(A)11根

(B)12根

(C)13根

(D)14根

48

若某存储器芯片地址线为12根,那么它的存储容量为()。

(A)1KB

(B)2KB

(C)4KB

(D)8KB

49

下面哪条指令产生信号()。

(A)MOVXA,@DPTR

D.P3

E.P0.7

28

MCS-51单片机的P0口可以作为( )使用。

A.低8位地址总线

B.高8位地址总线

C.数据总线

D.控制总线

E.一般的I/O使用

29

071-0029、ATMEL公司的AT24CXX系列EEPROM是()。

A.I C接口的EEPROM

B.SPI接口的EEPROM

C.并行接口的EEPROM

A.16D触发器

B.8D触发器

C.32位锁存器

D.16位锁存器

E.8位锁存器

15

071-0001、单片机扩展的内容有()等。

A.总线扩展

B.程序存储器扩展

C.数据存储器扩展

D.外围扩展

E.I/O口的扩展

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.3 输入/输出接口扩展

• MCS-51系列单片机内部有4个双向的8位并行I/O端 口:P0、P1、P2和P3口。

• 在实际的应用系统中,P0口分时地作为低8位地址 线和数据线,P2口作为高8位地址线。这时,P0口 和部分或全部的P2口无法再作通用I/O口。

• P3口的一些口线首先要满足第二功能的要求。这 时就需要进行单片机I/O口的扩展。 常用的I/O扩展有以下两种形式:

B

14位

定时

计数器

C

PA0~PA7 PB0~PB7

PC0~PC7

VCC(+5 V) VSS(GND)

8155的引脚封装图

8155的内部接口图

1. 8155的内部结构

• 8155各引脚的功能为: ➢ 地址/数据线AD0~AD7(8条):是低8位地址线和数据线

的共用输入总线,常和MCS-51单片机的P0口相连,用于 分时传送地址和数据; ➢ PA0~PA7、PB0~PB7:为A、B口线,用于和外设之间传 递数据; ➢ PC0~PC5为C端口线,既可与外设传送数据,也可以作为 A、B口的控制联络线; ➢ CS:片选线,低电平有效。

39 38 37 36 35 34 33 32

R ESET

INT0 INT1 T0 T1

P1. 0

P2. 0

P2. 1

MCS-51

P2. 2 P2. 3

P2. 4

P2. 5

P2. 6

P2. 7

21 22 23 24 25 26 27 28

P1. 1 P1. 2 P1. 3 P1. 4 P1. 5 P1. 6 P1. 7

RD WR PSEN ALE/ P TXD RXD

17 16 29 30 11 10

1 11

3 4 7 8 13 14 17 18

CLR CLK

1D 2D 3D 4D 5D 6D 7D 8D

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

2 5 6 9 12 15 16 19

7 4F2 7 3

A 1

3 2

VCC

15 14

T1 T0

89C51

31

EA/VP

+ 1 0u

19 18

X1 X2

P20 P21 P22 P23 P24 P25 P26 P27

21 22 23 24 25 26 27 28

9

R ESET

1 0K

17 16

RD WR

RXD TXD ALE/ P PSEN

10 11 30 29

U?

12 13 14 15 16 17 18 19

程序为:

……………….. RAMWR:MOV R0,#30H

思考:如果要把

MOV MOV

DPTR,#7E00H R2,#50

8155 RAM中, 从地址为7E00H

RAMW:MOV A,@R0

开始的50个数据

24

25 26

AD0~AD7

27

28

CE

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

29 30 31 32 33 34 35 36

ALE RD WR RESET

PC0 PC1 PC2 PC3 PC4 PC5

37 38 39 1 2 5

TIMER IN TIMER OUT

256字节 A 静态 RAM

9

7 8 13

2D 3D 4D

4Q 5Q 6Q

12 15 16

12 13 14 15

14

5D 6D

7Q 8Q

19

1 2 3

17 18

7D

4 5 6

8D

7

8

7 4LS 2 73

74LS273引脚封装图

EA/VP X1

X2

P0. 0 P0. 1 P0. 2 P0. 3 P0. 4 P0. 5 P0. 6 P0. 7

❖ 当单片机从74LS244读取数据时应该为:

MOV DPTR,#7FFFH ;将74LS244的口地址送入DPTR

MOVX A,@DPTR ; 74LS244的端口读取数据到ACC

锁存器扩展输出口

• 利用74LS273进行输出口的扩展 VCC

1 CLR

31

11

2

19

CLK 1Q

2Q 5

18

3

6

4 1D 3Q 9

➢ RESET:复位线,通常与单片机的复位端相连。 ➢ ALE:地址锁存线,高电平有效。 ➢ IO/M:RAM或I/O口的选择线。当为0时,选中8155的256 B

RAM;当为1时,选中8155片内3个I/O端口以及命令/状态寄 存器和定时/计数器。

➢ RD和WR:读/写线,控制8155的读、写操作。 ➢ TMRIN(TI):定时/计数器的脉冲输入端。 ➢ TMROUT(TO):定时/计数器的输出信号端。 ➢ VCC:电源端。 ➢ GND:接地端。

7 4LS3 2Mຫໍສະໝຸດ S-51与74LS273的接口电路图

•74LS273是一种8D触发器器。当它的控制端信号有效且触 发端信号有效时,输入D1-D8端的数据被锁存到8D触发器中 并形成输出Q1-Q8。 ❖在上图的电路中,P2.7与WR相或后作为74LS273的锁存 信号,单片机的P0口与74LS273的8位输出端相连,所以 74LS273的地址为:7FFFH。 ❖当单片机从74LS244输出数据是应该为: MOV DPTR,#7FFFH ;将74LS244的口地址送入DPTR

I/O口 命令/状态口 PA口 PB口 PC口 定时器/计数器低字节寄存器 定时器/计数器高字节寄存器

3. 8155的命令字和状态字

❖ 芯片8155 的I/O口和定时器/计数器的工作方式可以通 过对8155的命令寄存器写入控制字来实现。

❖ 8155的命令寄存器和状态寄存器使用同一个地址。

➢ 8155的命令字 命令字主要规定了8155的I/O口和定时器的工作方式。

▪ 简单的I/O口扩展主要包括:

➢ 缓冲器扩展输入口(三态门: 74LS244、74LS245等)

➢ 锁存器扩展输出口(锁存器: 74LS273、74LS373、 74LS377等)

缓冲器扩展输入口

• 利用74LS244进行输入口的扩展

1 2 4 6 8

1G A1 A2 A3 A4

1 Y1 1 Y2 1 Y3 1 Y4

• 选通I/O方式:由PC口的低三位作联络线使用,其余位作 I/O线;输入联络线可以起选通数据锁存作用;中断时有中 断请求信号产生;各个联络线为:

➢ INTRA:中断请求输出标志。 ➢ BFA:PA口缓冲器/空输出信号。 ➢ STBA:数据选通输入信号。

4. 8155的定时器/计数器

• 8155片内的定时器/计数器是一个14位的减计数器。计数 器分为高6位和低8位寄存器,它的计数初值有程序预置。 它的格式为: 高字节寄存器(M2和M1是工作方式码)

12 13 14 15 16 17 18 19

AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

8 9 10 7 11

CE RD WR IO/ M ALE

8155

6

TMR OUT

3

TMR IN

4

R ESET

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

21

22

IO/M

23

2. 8155的RAM和I/O口地址编码

• 8155当IO/M为0时,单片机对8155的RAM进行操作,共 256B,低八位的地址为:00H—0FFH。

• 8155当IO/M为1时,单片机对8155的I/O口进行操作。 8155内部寄存器地址分配表

低八位地址 xxxxx000B xxxxx001B xxxxx010B xxxxx011B xxxxx100B xxxxx101B

M2 M1 T13 T12 T11 T10 T9 T8

低字节寄存器(T0—T13为计数器的初值)

T7 T6 T5 T4 T3 T2 T1 T0

8155定时器/计数器四种操作方式和输出波形

M2 M1

方

式

波

形

00 01 10 11

单次方波 连续方波 单个脉冲 连续脉冲

5. 8155的应用

1)8155RAM的使用 例题:假定在MCS-51单片机的内部RAM中,从30H开始 存放一组数据,字节数为50,要求将该组数据存入8155 RAM中,起始地址为7E00H。

18 16 14 12

19 11 13 15 17

2G B1 B2 B3 B4

2 Y1 2 Y2 2 Y3 2 Y4

9 7 5 3

7 4LS2 44

74LS244引脚封装图

31

19

18

9

12 13 14 15

1 2 3 4 5 6 7 8

EA/VP

X1

X2

R ESET

INT0 INT1 T0 T1

P1. 0 P1. 1 P1. 2 P1. 3 P1. 4 P1. 5 P1. 6 P1. 7

➢ 简单I/O接口芯片的扩展 ➢ 可编程I/O接口电路的扩展

4.3.1简单I/O接口芯片的扩展

▪ 简单的I/O口扩展通常是采用TTL或CMOS电路锁存器、三

态门等作为扩展芯片(74LS244、74LS245、74LS273、 74LS373、74LS377等),通过P0口来实现扩展的一种 方案。它具有电路简单、成本低、配置灵活的特点。

17 16 29 30 11 10

3 5 7 9

2 Y4 2 Y3 2 Y2 2 Y1

B4 B3 B2 B1 2G

17 15 13 11 19

• MCS-51系列单片机内部有4个双向的8位并行I/O端 口:P0、P1、P2和P3口。

• 在实际的应用系统中,P0口分时地作为低8位地址 线和数据线,P2口作为高8位地址线。这时,P0口 和部分或全部的P2口无法再作通用I/O口。

• P3口的一些口线首先要满足第二功能的要求。这 时就需要进行单片机I/O口的扩展。 常用的I/O扩展有以下两种形式:

B

14位

定时

计数器

C

PA0~PA7 PB0~PB7

PC0~PC7

VCC(+5 V) VSS(GND)

8155的引脚封装图

8155的内部接口图

1. 8155的内部结构

• 8155各引脚的功能为: ➢ 地址/数据线AD0~AD7(8条):是低8位地址线和数据线

的共用输入总线,常和MCS-51单片机的P0口相连,用于 分时传送地址和数据; ➢ PA0~PA7、PB0~PB7:为A、B口线,用于和外设之间传 递数据; ➢ PC0~PC5为C端口线,既可与外设传送数据,也可以作为 A、B口的控制联络线; ➢ CS:片选线,低电平有效。

39 38 37 36 35 34 33 32

R ESET

INT0 INT1 T0 T1

P1. 0

P2. 0

P2. 1

MCS-51

P2. 2 P2. 3

P2. 4

P2. 5

P2. 6

P2. 7

21 22 23 24 25 26 27 28

P1. 1 P1. 2 P1. 3 P1. 4 P1. 5 P1. 6 P1. 7

RD WR PSEN ALE/ P TXD RXD

17 16 29 30 11 10

1 11

3 4 7 8 13 14 17 18

CLR CLK

1D 2D 3D 4D 5D 6D 7D 8D

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

2 5 6 9 12 15 16 19

7 4F2 7 3

A 1

3 2

VCC

15 14

T1 T0

89C51

31

EA/VP

+ 1 0u

19 18

X1 X2

P20 P21 P22 P23 P24 P25 P26 P27

21 22 23 24 25 26 27 28

9

R ESET

1 0K

17 16

RD WR

RXD TXD ALE/ P PSEN

10 11 30 29

U?

12 13 14 15 16 17 18 19

程序为:

……………….. RAMWR:MOV R0,#30H

思考:如果要把

MOV MOV

DPTR,#7E00H R2,#50

8155 RAM中, 从地址为7E00H

RAMW:MOV A,@R0

开始的50个数据

24

25 26

AD0~AD7

27

28

CE

PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

29 30 31 32 33 34 35 36

ALE RD WR RESET

PC0 PC1 PC2 PC3 PC4 PC5

37 38 39 1 2 5

TIMER IN TIMER OUT

256字节 A 静态 RAM

9

7 8 13

2D 3D 4D

4Q 5Q 6Q

12 15 16

12 13 14 15

14

5D 6D

7Q 8Q

19

1 2 3

17 18

7D

4 5 6

8D

7

8

7 4LS 2 73

74LS273引脚封装图

EA/VP X1

X2

P0. 0 P0. 1 P0. 2 P0. 3 P0. 4 P0. 5 P0. 6 P0. 7

❖ 当单片机从74LS244读取数据时应该为:

MOV DPTR,#7FFFH ;将74LS244的口地址送入DPTR

MOVX A,@DPTR ; 74LS244的端口读取数据到ACC

锁存器扩展输出口

• 利用74LS273进行输出口的扩展 VCC

1 CLR

31

11

2

19

CLK 1Q

2Q 5

18

3

6

4 1D 3Q 9

➢ RESET:复位线,通常与单片机的复位端相连。 ➢ ALE:地址锁存线,高电平有效。 ➢ IO/M:RAM或I/O口的选择线。当为0时,选中8155的256 B

RAM;当为1时,选中8155片内3个I/O端口以及命令/状态寄 存器和定时/计数器。

➢ RD和WR:读/写线,控制8155的读、写操作。 ➢ TMRIN(TI):定时/计数器的脉冲输入端。 ➢ TMROUT(TO):定时/计数器的输出信号端。 ➢ VCC:电源端。 ➢ GND:接地端。

7 4LS3 2Mຫໍສະໝຸດ S-51与74LS273的接口电路图

•74LS273是一种8D触发器器。当它的控制端信号有效且触 发端信号有效时,输入D1-D8端的数据被锁存到8D触发器中 并形成输出Q1-Q8。 ❖在上图的电路中,P2.7与WR相或后作为74LS273的锁存 信号,单片机的P0口与74LS273的8位输出端相连,所以 74LS273的地址为:7FFFH。 ❖当单片机从74LS244输出数据是应该为: MOV DPTR,#7FFFH ;将74LS244的口地址送入DPTR

I/O口 命令/状态口 PA口 PB口 PC口 定时器/计数器低字节寄存器 定时器/计数器高字节寄存器

3. 8155的命令字和状态字

❖ 芯片8155 的I/O口和定时器/计数器的工作方式可以通 过对8155的命令寄存器写入控制字来实现。

❖ 8155的命令寄存器和状态寄存器使用同一个地址。

➢ 8155的命令字 命令字主要规定了8155的I/O口和定时器的工作方式。

▪ 简单的I/O口扩展主要包括:

➢ 缓冲器扩展输入口(三态门: 74LS244、74LS245等)

➢ 锁存器扩展输出口(锁存器: 74LS273、74LS373、 74LS377等)

缓冲器扩展输入口

• 利用74LS244进行输入口的扩展

1 2 4 6 8

1G A1 A2 A3 A4

1 Y1 1 Y2 1 Y3 1 Y4

• 选通I/O方式:由PC口的低三位作联络线使用,其余位作 I/O线;输入联络线可以起选通数据锁存作用;中断时有中 断请求信号产生;各个联络线为:

➢ INTRA:中断请求输出标志。 ➢ BFA:PA口缓冲器/空输出信号。 ➢ STBA:数据选通输入信号。

4. 8155的定时器/计数器

• 8155片内的定时器/计数器是一个14位的减计数器。计数 器分为高6位和低8位寄存器,它的计数初值有程序预置。 它的格式为: 高字节寄存器(M2和M1是工作方式码)

12 13 14 15 16 17 18 19

AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

8 9 10 7 11

CE RD WR IO/ M ALE

8155

6

TMR OUT

3

TMR IN

4

R ESET

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7

21

22

IO/M

23

2. 8155的RAM和I/O口地址编码

• 8155当IO/M为0时,单片机对8155的RAM进行操作,共 256B,低八位的地址为:00H—0FFH。

• 8155当IO/M为1时,单片机对8155的I/O口进行操作。 8155内部寄存器地址分配表

低八位地址 xxxxx000B xxxxx001B xxxxx010B xxxxx011B xxxxx100B xxxxx101B

M2 M1 T13 T12 T11 T10 T9 T8

低字节寄存器(T0—T13为计数器的初值)

T7 T6 T5 T4 T3 T2 T1 T0

8155定时器/计数器四种操作方式和输出波形

M2 M1

方

式

波

形

00 01 10 11

单次方波 连续方波 单个脉冲 连续脉冲

5. 8155的应用

1)8155RAM的使用 例题:假定在MCS-51单片机的内部RAM中,从30H开始 存放一组数据,字节数为50,要求将该组数据存入8155 RAM中,起始地址为7E00H。

18 16 14 12

19 11 13 15 17

2G B1 B2 B3 B4

2 Y1 2 Y2 2 Y3 2 Y4

9 7 5 3

7 4LS2 44

74LS244引脚封装图

31

19

18

9

12 13 14 15

1 2 3 4 5 6 7 8

EA/VP

X1

X2

R ESET

INT0 INT1 T0 T1

P1. 0 P1. 1 P1. 2 P1. 3 P1. 4 P1. 5 P1. 6 P1. 7

➢ 简单I/O接口芯片的扩展 ➢ 可编程I/O接口电路的扩展

4.3.1简单I/O接口芯片的扩展

▪ 简单的I/O口扩展通常是采用TTL或CMOS电路锁存器、三

态门等作为扩展芯片(74LS244、74LS245、74LS273、 74LS373、74LS377等),通过P0口来实现扩展的一种 方案。它具有电路简单、成本低、配置灵活的特点。

17 16 29 30 11 10

3 5 7 9

2 Y4 2 Y3 2 Y2 2 Y1

B4 B3 B2 B1 2G

17 15 13 11 19