指令周期表

PLC 基本指令表

NOP指令不影响程序的执行,执行数N(1-255)。

名称

助记符

目标元件

说明

取指令

LD

I、Q、M、SM、T、C、V、S、L

常开接点逻辑运算起始

取反指令

LDN

I、Q、M、SM、T、C、V、S、L

常闭接点逻辑运算起始

线圈驱动指令

=

Q、M、SM、T、C、V、S、L

驱动线圈的输出

与指令

A

I、Q、M、SM、T、C、V、S、L

单个常开接点的串联

与非指令

AN

I、Q、M、SM、T、C、V、S、L

输入信号上升沿Biblioteka 生脉冲输出负跳变EU

I、Q、M、SM、T、C、V、S、L

输入信号下降沿产生脉冲输出

空操作指令

NOP

无

使步序作空操作

一、标准触点LD、A、O、LDN、AN、ON、

LD,取指令。表示一个与输入母线相连的常开接点指令,即常开接点逻辑运算起始。

LDN,取反指令。表示一个与输入母线相连的常闭接点指令,即常闭接点逻辑运算起始。

三、输出=

=,在执行输出指令时,映像寄存器中的指定参数位被接通。

四、置位与复位指令S、R

S,执行置位(置1)指令时,从bit或OUT指定的地址参数开始的N个点都被置位。

R,执行复位(置0)指令时,从bit或OUT指定的地址参数开始的N个点都被复位。

置位与复位的点数可以是1-255,当用复位指令时,如果bit或OUT指定的是T或C时,那么定时器或计数器被复位,同时当前值将被清零。

单个常闭接点的串联

或指令

O

I、Q、M、SM、T、C、V、S、L

单个常开接点的并联

单片机89C51精确延时

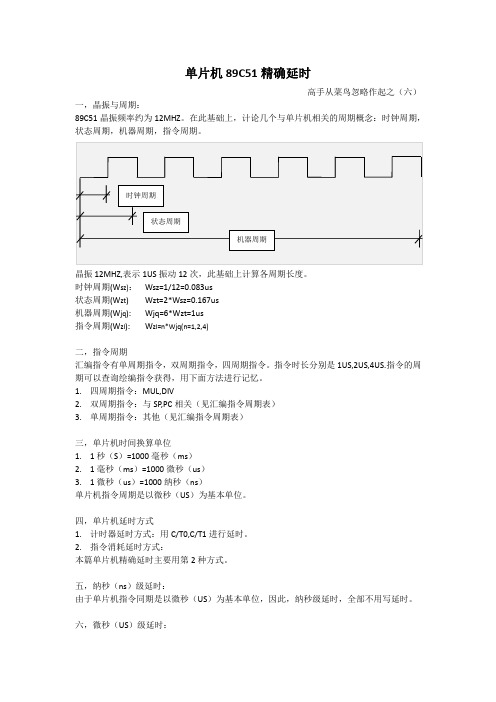

单片机89C51精确延时高手从菜鸟忽略作起之(六)一,晶振与周期:89C51晶振频率约为12MHZ。

在此基础上,计论几个与单片机相关的周期概念:时钟周期,状态周期,机器周期,指令周期。

晶振12MHZ,表示1US振动12次,此基础上计算各周期长度。

时钟周期(W sz):Wsz=1/12=0.083us状态周期(W zt) Wzt=2*Wsz=0.167us机器周期(W jq): Wjq=6*Wzt=1us指令周期(W zl): W zl=n*Wjq(n=1,2,4)二,指令周期汇编指令有单周期指令,双周期指令,四周期指令。

指令时长分别是1US,2US,4US.指令的周期可以查询绘编指令获得,用下面方法进行记忆。

1.四周期指令:MUL,DIV2.双周期指令:与SP,PC相关(见汇编指令周期表)3.单周期指令:其他(见汇编指令周期表)三,单片机时间换算单位1.1秒(S)=1000毫秒(ms)2.1毫秒(ms)=1000微秒(us)3.1微秒(us)=1000纳秒(ns)单片机指令周期是以微秒(US)为基本单位。

四,单片机延时方式1.计时器延时方式:用C/T0,C/T1进行延时。

2.指令消耗延时方式:本篇单片机精确延时主要用第2种方式。

五,纳秒(ns)级延时:由于单片机指令同期是以微秒(US)为基本单位,因此,纳秒级延时,全部不用写延时。

六,微秒(US)级延时:1.单级循环模式:delay_us_1最小值:1+2+2+0+2+1+2+2=12(US),运行此模式最少需12US,因此12US以下,只能在代码中用指定数目的NOP来精确延时。

最大值:256*2+12-2=522(US),256最大循环次数,2是指令周期,12是模式耗时,-2是模式耗时中计1个时钟周期。

延时范围:值域F(X)[12,522],变量取值范围[0,255].函数关系:Y=F(x):y=2x+12,由输入参数得出延时时间。

反函数:Y=F(x):y=1/2x-6:由延时时间,计算输入参数。

第四章 8088的总线周期和时序

第6章 输入和输出

输入和输出设备是计算机系统的重要组 成部分。

程序

输 计 入 装 置 机 算

输 出 装

信

原始 数据 信息

置

24

常用输入装置有: 键盘、扫描仪等. 常用输出装置有: CRT、打印机等. 磁盘、磁带既可做输入也可做输出. 微处理器与外设的连接都是通过输入输出 接口电路进行的。由于外设的功能多种多样, 原理不同,工作速度不同,因此接口电路也是 多种多样。 接口电路分为并行接口和串行接口. 8255A、A/D及D/A等接口将在后面介绍。

5

4.2

8088的总线

4.2.1 8088的两种组态 • 最小组态:系统中只有一片8088,其存储 容量不大,所要连的I/O端口也不多,总线 控制逻辑电路被减到最小。 • 最大组态:构成的系统较大,可能包含不 只一片微处理器,或要求有较强的驱动能 力,带有一个总线控制器8288。

6

4.2.2 8088的引脚和功能

31

2.状态信息 输入设备 用READY表示准备好否? READY=1,准备好; READY=0,未准备好。 输出设备 常用BUSY表示忙否? BUSY=1忙。 例:打印机若不忙,可送数 3.控制信号 (0或1)控制继电器的吸合与断开 或外设的启动与停止等。 状态信息、控制信号与数据是不同性质 的信息,必须区分开来,但微机只有通用的 32 IN/OUT指令。即只能:

16

4.3 最小模式下的8088时序

4.3.1 8088的读周期时序

T1

CLK IO/M A19~A16/S6~S3 A15~A8 AD7~AD0 ALE RD DT/R DEN

17

T2

高IO

T3

低M S6~S3

计算机组成原理课后答案(第二版)_唐朔飞_第八章

16. 计算机为了管理中断,在硬件上 计算机为了管理中断 管理中断, 设置? 作用? 通常有哪些设置 各有何作用 通常有哪些设置?各有何作用?对指令系 有何考虑? 统有何考虑? 计算机为了管理中断, 解:计算机为了管理中断,在硬件上 中断系统。 设有专门处理中断的机构——中断系统 设有专门处理中断的机构——中断系统。 它通常包括 中断请求寄存器、 包括: Байду номын сангаас通常包括:中断请求寄存器、中断优先 级排队器、向量编码器、 级排队器、向量编码器、中断允许触发器 EINT)、中断标记触发器(INT)、 )、中断标记触发器 (EINT)、中断标记触发器(INT)、 中断屏蔽触发器(寄存器) 功能如下: 中断屏蔽触发器(寄存器)等。功能如下: 中断请求寄存器——对中断源发来的 中断请求寄存器——对中断源发来的 一过性中断请求信号进行登记 登记; 一过性中断请求信号进行登记; 中断优先级排队器——对同时提出的 中断优先级排队器——对同时提出的 裁决, 多个中断请求信号进行裁决 多个中断请求信号进行裁决,选出一个最 紧迫的进行响应; 紧迫的进行响应;

(2)中断周期流程图如下: 中断周期流程图如下: ↓ 关中断( EINT) 关中断(0→EINT) ↓ SP→BUS→MAR SP→BUS→ ↓ SP+1→ SP+1→SP ↓ PC→BUS→MDR PC→BUS→

说 明

堆栈栈顶地址送MAR 堆栈栈顶地址送MAR 修改堆栈指针 断点送内存

↓ 存储器写(CU(-W)→ 存储器写(CU(-W)→M) 进栈 ↓A

LDA ↓ IR(X)→MAR IR( ↓ N @=1? ↓Y(间址) 间址) 存储器读( 存储器读(CU(R) →M) ↓ MDR →BUS →MAR ↓ 存储器读( 存储器读(CU(R) →M) ↓ MDR →BUS →AC ↓ 直 接 寻 址

汇编语言指令速查表

附录附录A 常用80x86指令速查表指令按助记符字母顺序排列,缩写、符号约定如下:(1) 指令中,dst, src表示目的操作数和源操作数。

仅一个操作数时,个别处也表示为opr。

(2) imm表示立即数,8/16/32位立即数记作:imm8/imm16/imm32。

(3) reg表示通用寄存器,8/16/32位通用寄存器记作:reg8/reg16/reg32。

(4) mem表示内存操作数,8/16/32等内存操作数记作:mem8/mem16/mem32等。

(5) seg表示段寄存器,CS, DS, SS, ES, FS, GS。

(6) acc表示累加器,8/16/32累加器对应AL/AX/EAX。

(7)OF, SF, ZF, AF, PF, CF分别表示为O, S, Z, A, P, C,相应位置为:字母,根据结果状态设置;?,状态不确定;-,状态不变;1,置1;0,清0;例如:0 S Z ? P -表示:OF清0,AF不确定,CF不变,其它根据结果设置。

若该栏空白,则表示无关。

(8)寄存器符号诸如(E)CX, (E)SI, (E)DI, (E)SP, (E)BP和(E)IP等,表示在16地址模式下使用16位寄存器(如CX),或在32地址模式下使用32位寄存器(如ECX)。

(9)周期数表示指令执行所需的CPU时钟周期个数,即执行时间为:周期数/主频(秒)。

(10)诸如(386+)是表示该指令只能用于80386及以后微处理器上。

·252·附录·253··254·附录·255··256·附录·257··258·附录·259·附录B 编程练习环境说明1. 编程练习软件包附带软件包x86ASM是在Microsoft的MASM 6.15软件包的基础上,加入CodeView、Win32的开发工具及Turbo C 2.0等,进行简单整理而成的,以便初学者编程练习使用。

用表格列出指令执行阶段每个节拍的功能和有效控制信号

指令执行阶段每个节拍的功能和有效控制信号一、前言在计算机科学和工程中,指令执行阶段是中央处理器(CPU)执行指令的过程。

在这个过程中,CPU按照特定的节拍(时钟周期)来完成一条指令的执行,其中每个节拍都有特定的功能和有效的控制信号。

本文将对指令执行阶段的每个节拍进行详细的分析,列出各个节拍的功能和有效控制信号,以便读者更好地理解CPU的工作原理。

二、指令执行阶段的节拍功能和有效控制信号在指令执行阶段,CPU按照不同的节拍依次完成指令的获取、译码、执行和写回等过程。

下面将对每个节拍的功能和有效控制信号进行详细描述。

1. 取指节拍(IF)取指节拍是指CPU从内存中获取下一条指令的节拍。

在这个节拍中,CPU需要执行以下功能:- 从程序计数器(PC)中读取下一条指令的位置区域- 将指令位置区域发送给内存- 从内存中获取指令内容有效的控制信号包括:- 使能程序计数器(PC):控制PC是否可以接受新的指令位置区域- 内存读使能信号:通知内存准备读取数据- 存储器位置区域选择信号:指示内存需要读取的位置区域2. 译码节拍(ID)译码节拍是指CPU对获取的指令进行译码的节拍。

在这个节拍中,CPU需要执行以下功能:- 对获取的指令进行解码,确定指令的操作类型和操作数- 从寄存器或内存中读取操作数- 确定下一条指令的位置区域有效的控制信号包括:- 寄存器读使能信号:通知寄存器准备读取数据- 内存读使能信号:通知内存准备读取数据- ALU操作类型选择信号:指示ALU需要执行的操作类型3. 执行节拍(EX)执行节拍是指CPU执行指令的节拍。

在这个节拍中,CPU需要执行以下功能:- 对操作数执行算术或逻辑运算- 计算指令的结果- 确定下一条指令的位置区域有效的控制信号包括:- ALU操作类型选择信号:指示ALU需要执行的操作类型- ALU运算使能信号:通知ALU准备执行运算- 存储器写使能信号:通知内存需要写入数据4. 写回节拍(WB)写回节拍是指CPU将执行结果写入寄存器或内存的节拍。

单片机指令表(最全)

单片机指令以A开头的指令有18条,分别为:1、ACALL addr11指令名称:绝对调用指令指令代码:A10 A9 A8 10001 A7 A6 A5 A4 A3 A2 A1 A0指令功能:构造目的地址,进行子程序调用。

其方法是以指令提供的11位地址(al0~a0),取代PC的低11位,PC的高5位不变。

操作容:PC←(PC)+2SP←(SP)+1(SP)←(PC)7~0SP←(SP)+1(SP)←(PC)15~8PC10~0←addrl0~0字节数: 2机器周期:2使用说明:由于指令只给出子程序入口地址的低11位,因此调用围是2KB。

2、ADD A,Rn指令名称:寄存器加法指令指令代码:28H~2FH指令功能:累加器容与寄存器容相加操作容:A←(A)+(Rn), n=0~7字节数: 1机器周期;1影响标志位:C,AC,OV3、ADD A,direct指令名称:直接寻址加法指令指令代码:25H指令功能:累加器容与部RAM单元或专用寄存器容相加操作容:A←(A)+(direct)字节数: 2机器周期:1影响标志位:C,AC,OV4、ADD A,@Ri ’指令名称:间接寻址加法指令指令代码:26H~27H指令功能:累加器容与部RAM低128单元容相加操作容:A←(A)+((Ri)), i=0,1字节数: 1机器周期:1影响标志位:C,AC,OV5、ADD A,#data指令名称:立即数加法指令指令代码:24H指令功能:累加器容与立即数相加操作容:A←(A)+data字节数: 2机器周期:1影响标志位:C,AC,OV6、ADDC A,Rn指令名称:寄存器带进位加法指令指令代码:38H~3FH指令功能:累加器容、寄存器容和进位位相加操作容:A←(A)+(Rn)+(C), n=0~7字节数: 1 机器周期:1 影响标志位:C,AC,OV7、ADDC A,direct指令名称:直接寻址带进位加法指令指令代码:35H指令功能:累加器容、部RAM低128单元或专用寄存器容与进位位加操作容:A←(A)+(direct)+(C)字节数: 2机器周期:1影响标志位:C,AC,OV8、ADDC A,@Ri指令名称:间接寻址带进位加法指令指令代码:36H~37H指令功能:累加器容, 部RAM低128单元容与进位位相加操作容:A←(A)+((Ri))+(C), i=0,1字节数: 1机器周期:1影响标志位:C,AC,OV9、ADDC A,#data指令名称:立即数带进位加法指令指令代码:34H指令功能:累加器容、立即数与进位位相加操作容:A←(A)+data+(C)字节数: 2机器周期:1影响标志位:C,AC,OV10、AJMP addr11指令名称:绝对转移指令指令代码:A10 A9 A8 1 0 0 0 1 A7 A6 A5 A4 A3 A2 A1 A0 指令功能:构造目的地址,实现程序转移。

指令周期机器周期等各种周期介绍

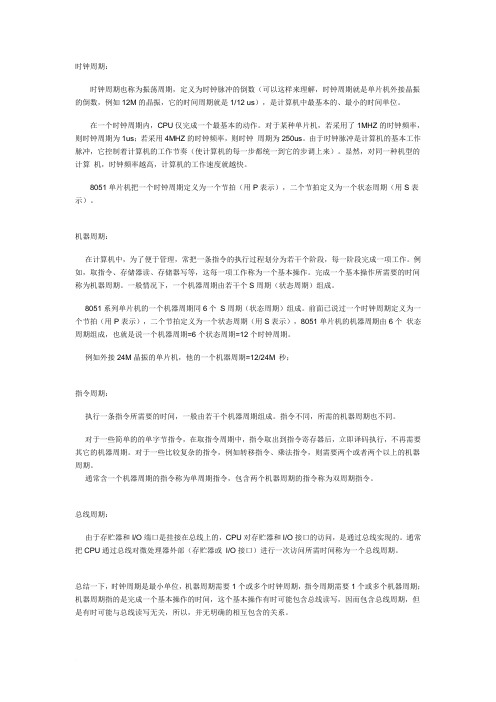

时钟周期:时钟周期也称为振荡周期,定义为时钟脉冲的倒数(可以这样来理解,时钟周期就是单片机外接晶振的倒数,例如12M的晶振,它的时间周期就是1/12 us),是计算机中最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。

对于某种单片机,若采用了1MHZ的时钟频率,则时钟周期为1us;若采用4MHZ的时钟频率,则时钟周期为250us。

由于时钟脉冲是计算机的基本工作脉冲,它控制着计算机的工作节奏(使计算机的每一步都统一到它的步调上来)。

显然,对同一种机型的计算机,时钟频率越高,计算机的工作速度就越快。

8051单片机把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。

机器周期:在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。

例如,取指令、存储器读、存储器写等,这每一项工作称为一个基本操作。

完成一个基本操作所需要的时间称为机器周期。

一般情况下,一个机器周期由若干个S周期(状态周期)组成。

8051系列单片机的一个机器周期同6个S周期(状态周期)组成。

前面已说过一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示),8051单片机的机器周期由6个状态周期组成,也就是说一个机器周期=6个状态周期=12个时钟周期。

例如外接24M晶振的单片机,他的一个机器周期=12/24M 秒;指令周期:执行一条指令所需要的时间,一般由若干个机器周期组成。

指令不同,所需的机器周期也不同。

对于一些简单的的单字节指令,在取指令周期中,指令取出到指令寄存器后,立即译码执行,不再需要其它的机器周期。

对于一些比较复杂的指令,例如转移指令、乘法指令,则需要两个或者两个以上的机器周期。

通常含一个机器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期指令。

总线周期:由于存贮器和I/O端口是挂接在总线上的,CPU对存贮器和I/O接口的访问,是通过总线实现的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

MOV direct, A

累加器送直接寻址单元

2

1

MOV Rn,#data

立即数送寄存器

2

1

MOV direct, #data

立即数送直接寻址单元

3

2

MOV@Ri, #data

立即数送内部RAM单元

2

1

MOV direct, Rn

寄存器送直接寻址单元

2

2

MOV Rn, direct

直接寻址单元送寄存器

1

2

算术运算类指令

XCH A, Rn

累加器与寄存器交换

1

1

XCH A,@Ri

累加器与内部RAM单元交换

1

1

XCHD A, direct

累加器与直接寻址单元交换

2

1

XCHD A,@Ri

累加器与内部RAM单元低4位交换

1

1

SWAP A

累加器高4位与低4位交换

1

1

POP direct

栈顶弹出指令直接寻址单元

累加器减寄存器和进位标志

1

1

SUBB A,@Ri

累加器减内部RAM单元和进位标志

1

1

SUBB A, #data

累加器减立即数和进位标志

2

1

SUBB A, direct

累加器减直接寻址单元和进位标志

2

1

DEC A

累加器减1

1

1

DEC Rn

寄存器减1

1

1

DEC@Ri

内部RAM单元减1

1

1

DEC direct

2

2

PUSH direct

直接寻址单元压入栈顶

2

2

ADD A, Rn

累加器加寄存器

1

1

ADD A,@Ri

累加器加内部RAM单元

1

1

ADD A, direct

累加器加直接寻址单元

2

1

ADD A, #data

累加器加立即数

2

1

ADDC A, Rn

累加器加寄存器和进位标志

1

1

ADDC A,@Ri

累加器加内部RAM单元和进位标志

3

2

1

1

ADDC A, #data

累加器加立即数和进位标志

2

1

ADDC A, direct

累加器加直接寻址单元和进位标志

2

1

INC A

累加器加1

1

1

INC Rn

寄存器加1

1

1

INC direct

直接寻址单元加1

2

1

INC@Ri

内部RAM单元加1

1

1

INC DPTR

数据指针加1

1

2

DA A

十进制调整11来自SUBB A, Rnmcs-51指令速查表

类别

指令格式

功能简述

字节数

周期

数据传送类指令期

MOV A, Rn

寄存器送累加器

1

1

MOV Rn,A

累加器送寄存器

1

1

MOV A,@Ri

内部RAM单元送累加器

1

1

MOV@Ri, A

累加器送内部RAM单元

1

1

MOV A, #data

立即数送累加器

2

1

MOV A, direct

直接寻址单元送累加器

1

MOV C, bit

直接寻址位送C

2

1

MOV bit, C

C送直接寻址位

2

1

CLR C

C清零

1

1

CLR bit

直接寻址位清零

2

1

CPL C

C取反

1

1

CPL bit

直接寻址位取反

2

1

SETB C

C置位

1

1

SETB bit

直接寻址位置位

2

1

ANL C, bit

C逻辑与直接寻址位

2

2

ANL C, /bit

1

2

MOVX@Ri, A

累加器送外部RAM单元(8位地址)

1

2

MOVX A,@DPTR

外部RAM单元送累加器(16位地址)

1

2

MOVX@DPTR, A

累加器送外部RAM单元(16位地址)

1

2

MOVC A,@A+DPTR

查表数据送累加器(DPTR为基址)

1

2

MOVC A,@A+PC

查表数据送累加器(PC为基址)

累加器与直接寻址单元不等转移

3

2

CJNE Rn,#data, rel

寄存器与立即数不等转移

3

2

CJNE@Ri, #data, rel

RAM单元与立即数不等转移

3

2

DJNZ Rn, rel

寄存器减1不为零转移

2

2

DJNZ direct, rel

直接寻址单元减1不为零转移

3

2

布尔操作类指令

NOP

空操作

1

2

2

MOV direct,@Ri

内部RAM单元送直接寻址单元

2

2

MOV@Ri, direct

直接寻址单元送内部RAM单元

2

2

MOV direct2,direct1

直接寻址单元送直接寻址单元

3

2

MOV DPTR, #data16

16位立即数送数据指针

3

2

MOVX A,@Ri

外部RAM单元送累加器(8位地址)

C逻辑与直接寻址位的反

2

2

ORL C, bit

C逻辑或直接寻址位

2

2

ORL C, /bit

C逻辑或直接寻址位的反

2

2

JC rel

C为1转移

2

2

JNC rel

C为零转移

2

2

JB bit,rel

直接寻址位为1转移

3

2

JNB bit,rel

直接寻址为0转移

3

2

JBC bit,rel

直接寻址位为1转移并清该位

直接寻址单元减1

2

1

MUL AB

累加器乘寄存器B

1

4

DIV AB

累加器除以寄存器B

1

4

逻辑运算类指令

ANL A, Rn

累加器与寄存器

1

1

ANL A,@Ri

累加器与内部RAM单元

1

1

ANL A, #data

累加器与立即数

2

1

ANL A, direct

累加器与直接寻址单元

2

1

ANL direct, A

直接寻址单元与累加器

直接寻址单元或立即数

3

1

XRL A, Rn

累加器异或寄存器

1

1

XRL A,@Ri

累加器异或内部RAM单元

1

1

XRL A,#data

累加器异或立即数

2

1

XRL A,direct

累加器异或直接寻址单元

2

1

XRL direct, A

直接寻址单元异或累加器

2

1

XRL direct, #data

直接寻址单元异或立即数

3

2

RL A

累加器左循环移位

1

1

RLC A

累加器连进位标志左循环移位

1

1

RR A

累加器右循环移位

1

1

RRC A

累加器连进位标志右循环移位

1

1

CPL A

累加器取反

1

1

CLR A

累加器清零

1

1

控制转移类指令

ACCALL addr11

2KB范围内绝对调用

2

2

AJMP addr11

2KB范围内绝对转移

2

2

LCALL addr16

2KB范围内长调用

3

2

LJMP addr16

2KB范围内长转移

3

2

SJMP rel

相对短转移

2

2

JMP@A+DPTR

相对长转移

1

2

RET

子程序返回

1

2

RET1

中断返回

1

2

JZ rel

累加器为零转移

2

2

JNZ rel

累加器非零转移

2

2

CJNE A, #data, rel

累加器与立即数不等转移

3

2

CJNE A, direct, rel

2

1

ANL direct, #data

直接寻址单元与立即数

3

1

ORL A, Rn

累加器或寄存器

1

1

ORL A,@Ri

累加器或内部RAM单元

1

1

ORL A,#data

累加器或立即数

2

1

ORL A,direct

累加器或直接寻址单元

2

1

ORL direct, A

直接寻址单元或累加器

2

1

ORL direct, #data