多功能车辆总线控制器中CRC编码器的设计

CRC编解码设计方案

CRC编解码设计方案第1章引言1.1 概述通信,指人与人或人与自然之间通过某种行为或媒介进行的信息交流与传递,从广义上指需要信息的双方或多方在不违背各自意愿的情况下无论采用何种方法,使用何种媒质,将信息从某方准确安全传送到另方。

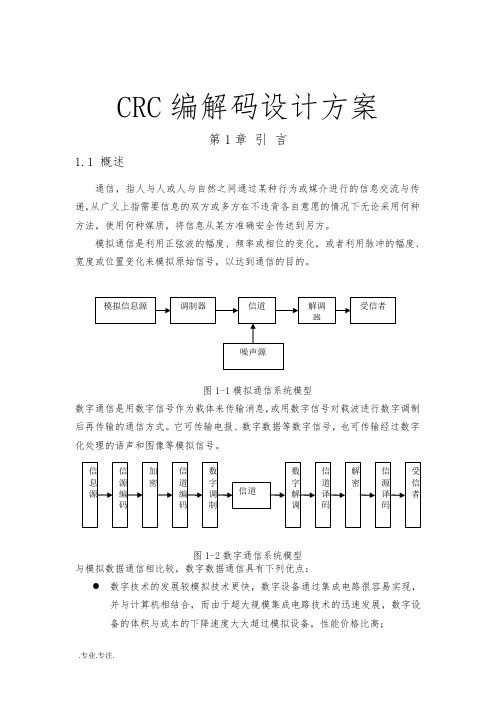

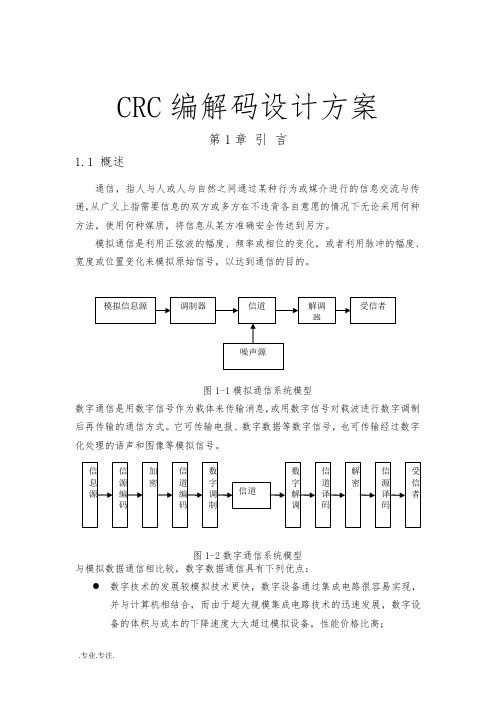

模拟通信是利用正弦波的幅度、频率或相位的变化,或者利用脉冲的幅度、宽度或位置变化来模拟原始信号,以达到通信的目的。

图1-1模拟通信系统模型数字通信是用数字信号作为载体来传输消息,或用数字信号对载波进行数字调制后再传输的通信方式。

它可传输电报、数字数据等数字信号,也可传输经过数字化处理的语声和图像等模拟信号。

图1-2数字通信系统模型与模拟数据通信相比较,数字数据通信具有下列优点:数字技术的发展较模拟技术更快,数字设备通过集成电路很容易实现,并与计算机相结合,而由于超大规模集成电路技术的迅速发展,数字设备的体积与成本的下降速度大大超过模拟设备,性能价格比高;●来自视频、声音和其他信息源的各类数据均可统一为数字信号的形式,并通过数字通信系统传输;●在长距离数字通信中可以通过中继器放大和整形来保证数字信号的完整性而不累积噪音;●以数据帧为单位传输数据,并通过检错编码和重发数据帧来发现与纠正通信错误,从而有效保证通信的可靠性;●使用加密技术可有效增强通信的安全性;●多路光纤技术的发展大大提高了数字通信的效率。

“信息社会”“信息经济”等名称越来越多的出现在我们的生活中,生活离不开信息,随着社会生产的发展,科学技术的进步,人们对传输信息的要求急剧增加.到了20世纪20年代,如何提高传递信息的能力和可靠性已成为普遍重视的课题,在传输过程中发生错误后能在收端自行发现或纠正的码。

数字信号在传输过程中,由于受到干扰的影响,码元波形变坏。

接收端收到后可能发生错误的判决。

由于乘性干扰引起的码间串扰,可以采用均衡的办法纠正.而加性的影响则需要用其他的办法解决。

在设计数字数字通信系统时,应该首先从合理选择调制制度,解调方法以及发生功率等方面考虑,使加性干扰不足以影响达到误码率的要求,在仍不能满足要求是,就要考虑采用查错控制措施了。

CRC校验的设计与实现

5.3.4 循环冗余校验的设计与实现本系统中数据通信技术占据重要地位,是保证数据采集准确性的关键。

客户端与称重仪表进行通信时,为减小产量信息在传输过程中由于电磁干扰等因素导致的错误,需进行数据校验。

数据校验方法有很多,比较传统的有:行列冗余校验、重复码校验、奇偶校验、循环冗余校验等。

本系统采用循环冗余校验(CRC )进行通信过程中的数据校验。

CRC 是一种检错能力很强的循环码,利用模2取余的原理对数据进行循环校验,计算效率高且误判概率极低,几乎为零。

从性能和开销上考虑,CRC 远优于传统的算术和校验及奇偶校验。

1.CRC 编码原理CRC 校验通常采用多项式编码的方式,参与校验的数据信息(以下简称“待校验数”)可看作一个n 阶的二进制形式的多项式,即121210...n n n n a x a x a x a ----++++。

例如,一个6位二进制数101101可表示为:54325321011011x x x x x x x x +++++=+++(为方便下文描述,把该类型的多项式称为“转换多项式()x g ”)。

CRC 的编码方式是把待校验数转变成二进制数()x t ,然后再将()x t 转变为转换多项式()x g ,令()()()R e t x R x g x ⎡⎤=⎢⎥⎣⎦(式中的[]Re 表示对中括号内的式子进行取余运算),将余数()R x 做为待校验数的CRC 校验码。

CRC 校验码具体求解步骤如下:①假设待校验数是n 位二进制形式的多项式()x t ,把()x t 转变为转换多项式()x g ,位数为n 。

在待校验数的末尾附加r 个零,则待校验数的长度变为n r +位,其对应的二进制形式的多项式变成()x t x r 。

②把()x g 和()x t x r 进行取余运算,设余数为()x y ,则()()()R e r x t x y x g x ⎡⎤=⎢⎥⎣⎦,()x y 位数为1-r 。

CRC编码器的设计

CRC编码器的设计

CRC(循环冗余校验)编码器是一种常用的错误检测编码器,其设计目标是通过增加校验位来提高数据的可靠性,以便在传输过程中检测出错误情况。

1.确定生成多项式:

CRC编码器的核心是一个生成多项式,它用于计算校验位。

生成多项式可以是任意的,在计算中应该选择与通信环境适应的生成多项式。

一般情况下,长度为n的CRC编码器使用n+1位的生成多项式,其中最高位和最低位都是1、生成多项式的选择对于CRC编码的性能有很大的影响,需要进行仔细的考虑和测试。

2.计算校验位:

校验位的计算是CRC编码器的关键步骤。

校验位的计算是通过将数据和生成多项式进行按位异或运算得到的。

具体步骤如下:

-在待发送的数据后面添加n个零(其中n是生成多项式的位数减1),得到新的数据块。

-将新的数据块除以生成多项式,得到的余数就是校验位。

3.添加校验位:

校验位计算完成后,将校验位添加到原始数据中。

校验位通常作为一个帧的最后一个字节。

4.发送数据:

将带有校验位的数据发送给接收端。

CRC编码器的性能可通过几个参数来评估,如最大错误检测能力(可以检测到的最大连续错误的位数)、最小错误检测能力(可以检测到的最小连续错误的位数)等。

这些参数与生成多项式的选择有关,因此在设计CRC编码器时,需要仔细选择生成多项式,以满足通信环境的要求。

总之,CRC编码器是一种常用的错误检测编码器,通过增加校验位来提高数据的可靠性。

设计一个有效的CRC编码器需要确定生成多项式、计算校验位、添加校验位和发送数据等步骤,并注意选择适合的生成多项式来满足通信环境的要求。

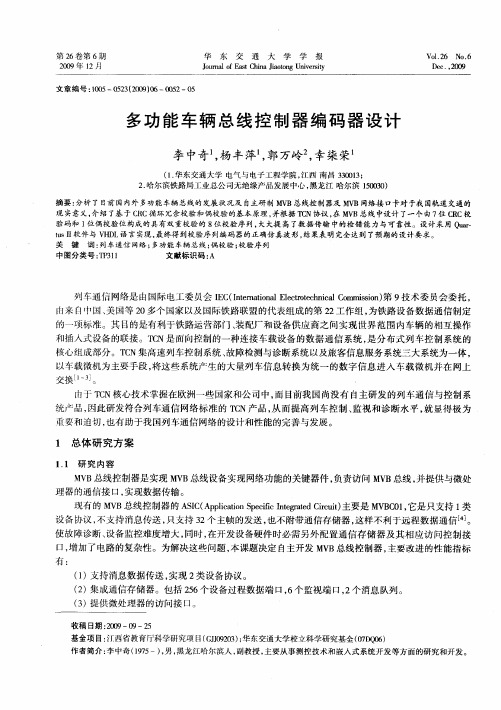

多功能车辆总线控制器编码器设计

巾于 T N核心 技术掌 握在 欧洲 一些 国家和公 司中 , 目前我 国 尚没有 自主研 发 的列 车通 信 与控 制 系 C 而 统产品, 因此研 发符合 列 车通信 网络 标 准 的 T N产 品 , 而提 高 列 车控 制 、 C 从 监视 和 诊 断水 平 , 显得 极 为 就

E, l增加 了电路 的复杂 性 。为解决 这些 问题 , 课题 决定 自主开 发 M B总线控 制器 , 本 V 主要改 进 的性 能指 标

有:

() 1 支持消息数据传送 , 实现 2 类设备协议 。 () 2 集成通信存储器。包括 26 5 个设备过程数据端 口, 个监视端 1 2 6 5, 个消息队列。 ( ) 供微处 理器 的访 问接 口。 3提

第 2 6卷第 6期

20 09年 1 2月 文 章 编 号 :05 0 2 (0 90 —05 —0 10 — 5320 }6 02 5

华

东

交

通

大

学

学

报

V 12 N . 0.6 o6 D c .0 9 e .2 0

Junlo atC iaJ oogUnvri o ra fE s hn i tn iesy a t

设 备 议 , 不支 持消息 传送 , 只支 持 3 主帧 的发送 , 不 附带通 信存储 器 , 2个 也 这样不 利 于远程 数据 通信 [ 引。 使 故 障诊 断 、 备监控 难度增 大 , 设 同时 , 在开发 设备 硬件 时必 需另 外 配置 通信 存 储 器及 其 相应 访 问控 制 接

收 稿 日期 :09 9 5 20 —0 —2

基金项 目: 汀西省教育厅科学研究项 目( J)23 ; GJ90 )华东交通大学校立科 学研 究基金 (7 Q 6 ( 0D 0 )

CAN总线中CRC编码的硬件实现

Ha d r m p e e a i n o r wa e I l m nt to f CRC c di g i En o n n CAN u b s

( e a t et fEl toi D p rm n e rnc o c s& C mp tr f G inU iesyo eh oo y, u n x 4 04, hn ) o ue ul nvri f T c nlg G a g i 1 0 C i o i t 5 a

维普资讯

2 o 年 1 月 08 o

第1 期 o

电 子 测 斌

EL cTR E 0Nl Es C T T

Oc . 0 t20 8

No. 0 1

C N 总线 中 C A RC编 码 的硬 件 实 现

陈 飞 ( 桂林工学 院电子与计算机系 桂林 5 10 ) 4 0 4

1 C C编 码 原 理 R

C C编码 的基本 思想 是利用 线性 编码理论 , R 在

发送 端根 据要传 送 的 k位二 进制 序 列 , 以一定 的规

则产 生一 个 校 验 用 的 r位监 督 码 ( 即所 谓 的 C C R

位错误 、 位填充 错误 、 固定形 式错 误 和应答 错 误 , 接

t = U

, 1 一

∑R 一[ ( ) m d g x ] g ) z x ] o E ( ) , ( 为生成多项

— U

R 一l _ R 一2 R 3

_ 一 1 -r

式 , 为 检验符 号 ; 字多 项式 为 : ( ) ∑ C R 码 cz 一 i, x

收端可 以通过 C C检 验来 发现 错误 。某 个 节点 发 R

CRC编解码设计方案

CRC编解码设计方案第1章引言1.1 概述通信,指人与人或人与自然之间通过某种行为或媒介进行的信息交流与传递,从广义上指需要信息的双方或多方在不违背各自意愿的情况下无论采用何种方法,使用何种媒质,将信息从某方准确安全传送到另方。

模拟通信是利用正弦波的幅度、频率或相位的变化,或者利用脉冲的幅度、宽度或位置变化来模拟原始信号,以达到通信的目的。

图1-1模拟通信系统模型数字通信是用数字信号作为载体来传输消息,或用数字信号对载波进行数字调制后再传输的通信方式。

它可传输电报、数字数据等数字信号,也可传输经过数字化处理的语声和图像等模拟信号。

图1-2数字通信系统模型与模拟数据通信相比较,数字数据通信具有下列优点:数字技术的发展较模拟技术更快,数字设备通过集成电路很容易实现,并与计算机相结合,而由于超大规模集成电路技术的迅速发展,数字设备的体积与成本的下降速度大大超过模拟设备,性能价格比高;●来自视频、声音和其他信息源的各类数据均可统一为数字信号的形式,并通过数字通信系统传输;●在长距离数字通信中可以通过中继器放大和整形来保证数字信号的完整性而不累积噪音;●以数据帧为单位传输数据,并通过检错编码和重发数据帧来发现与纠正通信错误,从而有效保证通信的可靠性;●使用加密技术可有效增强通信的安全性;●多路光纤技术的发展大大提高了数字通信的效率。

“信息社会”“信息经济”等名称越来越多的出现在我们的生活中,生活离不开信息,随着社会生产的发展,科学技术的进步,人们对传输信息的要求急剧增加.到了20世纪20年代,如何提高传递信息的能力和可靠性已成为普遍重视的课题,在传输过程中发生错误后能在收端自行发现或纠正的码。

数字信号在传输过程中,由于受到干扰的影响,码元波形变坏。

接收端收到后可能发生错误的判决。

由于乘性干扰引起的码间串扰,可以采用均衡的办法纠正.而加性的影响则需要用其他的办法解决。

在设计数字数字通信系统时,应该首先从合理选择调制制度,解调方法以及发生功率等方面考虑,使加性干扰不足以影响达到误码率的要求,在仍不能满足要求是,就要考虑采用查错控制措施了。

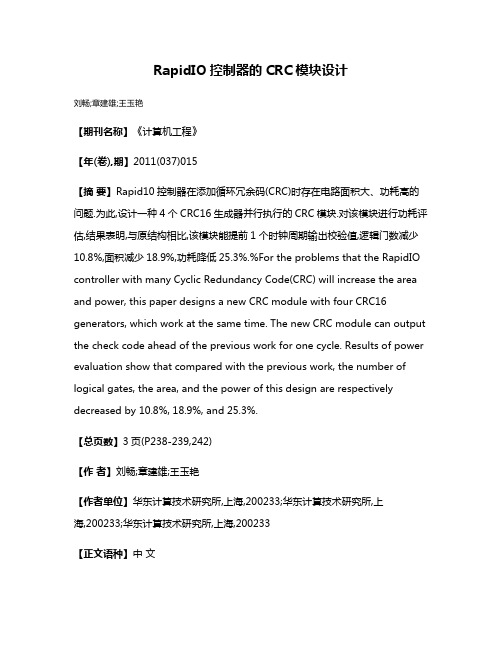

RapidIO控制器的CRC模块设计

RapidIO控制器的CRC模块设计刘畅;章建雄;王玉艳【期刊名称】《计算机工程》【年(卷),期】2011(037)015【摘要】Rapid10控制器在添加循环冗余码(CRC)时存在电路面积大、功耗高的问题.为此,设计一种4个CRC16生成器并行执行的CRC模块.对该模块进行功耗评估,结果表明,与原结构相比,该模块能提前1个时钟周期输出校验值,逻辑门数减少10.8%,面积减少18.9%,功耗降低25.3%.%For the problems that the RapidIO controller with many Cyclic Redundancy Code(CRC) will increase the area and power, this paper designs a new CRC module with four CRC16 generators, which work at the same time. The new CRC module can output the check code ahead of the previous work for one cycle. Results of power evaluation show that compared with the previous work, the number of logical gates, the area, and the power of this design are respectively decreased by 10.8%, 18.9%, and 25.3%.【总页数】3页(P238-239,242)【作者】刘畅;章建雄;王玉艳【作者单位】华东计算技术研究所,上海,200233;华东计算技术研究所,上海,200233;华东计算技术研究所,上海,200233【正文语种】中文【中图分类】TP303【相关文献】1.基于串行RapidIO协议的信息传输模块的设计与实现 [J], 高颖;曹峰;李兵强;常晨晨;2.采用窗口映射机制的RapidIO控制器设计 [J], 段小虎3.基于串行RapidIO协议的信息传输模块的设计与实现 [J], 高颖;曹峰;李兵强;常晨晨4.基于RapidIO协议的高速数据互联模块设计 [J], 上官珠;范国忠;高文昀5.通用RapidIO控制器的DMA高速传输方案设计 [J], 沈俊材因版权原因,仅展示原文概要,查看原文内容请购买。

CRC码生成与校验电路的设计与实现

CRC码生成与校验电路的设计与实现CRC码(Cyclic Redundancy Check)是一种常用于错误检测的校验码。

在数据通信和存储领域广泛应用。

CRC码生成与校验电路的设计与实现是指设计并搭建能够正确生成和校验CRC码的电路。

本文将从CRC码的原理、设计方案、实现步骤以及一些应用举例进行详细说明。

一、CRC码的原理CRC码利用除法操作来生成校验码,基本原理如下:1.以二进制形式将待传输或存储的数据进行编码表示。

2.选定一个固定的生成多项式G(x)。

3.将编码后的数据与生成多项式进行除法运算,得到余数,将余数添加到编码数据末尾,形成含有校验码的编码数据。

4.接收端根据相同的生成多项式进行除法运算,得到余数,如果余数为零,则认为数据传输或存储没有错误,否则,认为有错误发生。

二、CRC码的设计方案根据CRC码的原理,我们可以进行如下的设计方案:1.确定生成多项式。

生成多项式的选择非常重要,通常使用CRC-16或CRC-32等标准的生成多项式。

不同的生成多项式会导致CRC码的性能不同,可以根据需要进行选择。

2.确定初始寄存器值。

初始寄存器值决定了CRC码的初始状态,常见的初始值为全1或全0。

3.实现生成多项式的除法运算。

可以利用硬件电路或软件算法来实现多项式的除法运算。

硬件电路比较高效,适合于大规模的数据传输或存储系统。

三、CRC码的实现步骤CRC码的实现一般包括以下步骤:1.初始化寄存器值为初始值。

2.读入待编码数据。

3.将待编码数据与寄存器值进行异或操作。

4.判断待编码数据的最高位是否为1,如果为1,则将生成多项式与寄存器值进行异或操作,否则,寄存器值左移一位。

5.重复以上步骤,直到所有待编码数据被处理完毕。

6.将最终的寄存器值添加到编码数据末尾,形成含有校验码的编码数据。

四、CRC码的应用举例CRC码广泛应用于数据通信和存储领域,以下是一些应用举例:1.以太网通信:在以太网通信中,CRC码用于检测数据在传输过程中的错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

科 技l { l 论坛

第五 柯 鹏 ( 东公诚 通 信 建 设 监 理有 限公 司 , 东 广 州 5 0 1 ) 广 广 16 0

多功能车辆总线控制器中C C编码器的设计 R

摘 要 : 了降低 T N (ri o mu i t n N tok 的数 据 误 码 率 , 为 C Tan C m nc i e r) ao w 需要 采 用一 种 高性 能 的 差错 控 制 方 法。 环 冗余 校 验 ( R ) 循 C C 由于 编码 简 单且 高效 , 是一种最常见 的信道编码方法。根据 T N协议 , T N MV C 在 C B总线 中一个由 7位 C C校验码和 1 R 位偶校验位 构成 的具有双 重校验 的 8

住校验序列。按照 M B总线中帧的格式不同, V 选择 串行算法实现 。最终得到校验序 列编码 器的正确仿真波形, 并在 F G P A硬件上 实现。

关 键 词 :P A;R 偶 校 验 ; F G C C; 多功 能 车辆 总线 控 制 器

T N是 由连接 一个车厢 内各种设 备的车 C 厢总线和连接一列车 内各车厢总线 的列车总线 组成 。 中多功能车辆总线 MV ( tu co 其 B Mui nt n f i V ci u ) eh e B s是一种高可靠性 的实时通信总线 , l 主要用于车辆 电气设备互联通信。为满足通信 的准确性与可靠性 ,在总线 中设计一个具有很 强的检错纠错能力的校验序列显得尤为重要。 1 验编 码 原 理 校 11C C校 验 . R 循 环 冗余 校 验 码 ( RC码 , R = yl C C C Cci c R d n a c hc )是通信领域 中常用的一种 e udn y C ek 线性分组差错校验码 ,其特征是信息字段和校 验字段的长度可 以任意选定 。C C是利用除法 R 及余数 的原理来作错误 侦测 ( r rD tcn ) E r e t g o ei 的。 RC码信息字段为 K位, C 校验字段为 R位, 因此的编码码字长度为 N (= + ) N K R。其中信息 字段是需要校验 的信息数据 。( 见图 1 ) C RC校验可以 10 0 %地检测出所 有奇数个 随机错误和长度小于等于 r( 为 g 的阶数 ) r () 的突发错误 。所 以, R C C的生成 多项式 的阶数 越高 , 误判 的概率就越小 , 同时电路设计也 就 但 越复杂 。 本文中 , B总线需要依照帧的类 型、 MV 帧长不 同, 校验位会有所不 同。 1 . , 校验(C 2奇 偶 E C) 奇, 偶校验是数据传送时采用的一种校正 数据错误 的一种方式 ,分为奇校验和偶校验两 种1 3 1 中偶校验是数据传送时 , 。其 当实际数据 中 …’ 1 的个数为偶数的时候 , 这个校验位就是 … , 0’ 否则这个校验位就是 … ’ 1 。奇校验与之相反 。 2控制器总体设计 MV C在 数据链 路层 上处理 帧的接 收与 B 发送 ,依靠物理层发送和接收具有电气特征 的 电信号 ; 同时为网络层提供过程数据、 消息数据 的变 量 接 口 , 该接 口采 用 通 讯 存储 器 实 现 。图 2 为本项 目设计 的 M C内部 结构框图 , VB 由曼彻 斯 特编解码模块 , 发送 , 接收缓冲器 , 配置寄存 器 ,通讯存储器 T 以及 主控制单元等部分组 M 成。 MV C通 过 物 理 层 提 供 的 双 线 冗 余 连 接 B MV 接 收 C U 的访 问 控 制 , 而 实 现 MV B, P 从 B上 获取和发送设备数据 ,同时通过访问监视数据 实现对 MV B的管理 。 发送数据时 , U将帧数据从 T MC M读出并 写到发送缓冲器 中,再由编码器读出并完成编 码校验等功能后发送到 MV B总线 上; 接收时解 码器完成对输人帧译码并检验其有效性 ,把数 据存放到相应 的通讯存储器中,从而完成接收 数据的过程。 另外 , B MV C可 根 据 配置 实 现 总 线 主与总线从的功能 ,实现数据链路层以及一部 分传输层 的数据处理 ,并通过通讯存储器来 与

循 IC 6 8 0 5 fr a c s F E 0 7 — om t l s T2的 规 定 , a 按

信息位 (位 )式 R

图 2 MV C结 构框 图 B

串l 日

如下的生成多项式计算 : x=7x Sx 1 g()x +2 。 + +x + C C校验方式 分为 串行和并行两种 ,串行方 R 式简单但 是耗时较长 ,而并行方式算法 复杂 但只适合等长信息位校验 。由于 M B中帧数 V 据长度是 不断变 化的 , 但帧数据长度较短 , 因 此本文采用串行方式 。 C C校验码生成 电路采用线性反馈移位 R 寄存器来实现 ,也就是通用的 C C串行算法 R 实现电路 。 如图 3 所示。 每一个寄存器保存一

上 层 软 件 交互 。

在第 1 已说 明 , B总线需要依 照帧 节 MV l 的类型 、 帧长不 同, 校验位会 有所不同 。如主 帧为 1 6位 , 其后 加 8位校 验 ; 而从 帧的 长度 有 1 、2 6 、2 6 3 、4 1 8或 2 6位 ,每 6 5 4位数 据后 包含一个 8位 的校验位 , 不足 6 4位数据的也 附加 8 位校验位 。 位的校验序列 由 7 C C 8 位 R 校验码和一位偶校验位扩展构成 ,最终的校 验位由所得 的 8位数据反向发送I l I 。 31C C校验设计 . R 首先进行 C C校验。 R 在国际标准 中, 根据 生成多项式 gx 的不同 , R () C C又可分为 几种 标准。 文中, 本 7位 C C校验码 的运算公式遵 R