TN92驱动板原理图

门极驱动板原理简单说明

门极驱动板原理说明香港地铁门极驱动板主要为逆变器IGBT模块提供各IGBT管的门极驱动电路,并为IGBT管提供故障检测功能。

该板由三相完全相同的电路组成(R相,S相,T相),每一相有A、B两路分别对应每一相的上管与下管。

下面取其中一相(T相)进行说明:T相电路主要由三个功能块构成:1. 门极驱动板电源电路;为门极驱动提供电源。

2. 门极驱动板脉冲分配电路;控制T相上管与下管的开通关断时间,死区时间及最小导通时间等。

3. 门极驱动板故障检测电路。

当某管通过电流过大时能及时检测到,并采取对该管的保护措施。

下面分别对以上三个功能进行详细描述:1.门极驱动板电源电路门极驱动板电源电路主要为IGBT管提供+15V及-6V的门极导通,关断电源,同时也为门极驱动板上各芯片提供工作电源。

该板通过变压器T21及T22实现高压端与低压端的隔离,其中变压器T21的次边电路为TB管提供电源,变压器T22的次边电路为TA管提供电源。

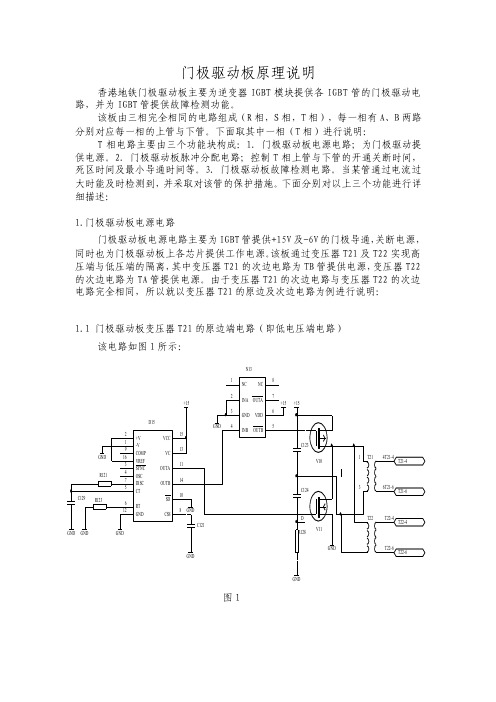

由于变压器T21的次边电路与变压器T22的次边电路完全相同,所以就以变压器T21的原边及次边电路为例进行说明:1.1 门极驱动板变压器T21的原边端电路(即低电压端电路)该电路如图1所示:图1该电路主要由PWM 控制器D15,场效应管驱动器N13及场效应管V10,V11构成,为变压器次边提供电源。

当D15芯片(PWM 控制器)的15脚输入+15V 电压时,此芯片开始工作,在其输出口11脚(OUTA )与14脚(OUTB)产生如图2所示电压波形:图2电容C123,C124上的电压通过变压器T21,T22的原边及场效应管V11放电。

当OUTB(D15-14)脚输出高电平时, 场效应管驱动器 N13-5脚输出低电平,场效应管V10导通;此时OUTA(D15-11)脚输出低电平,场效应管V11关断。

15V 电压通过场效应管V10,变压器T21,T22的原边对电容C123,C124进行充电。

OUTA 与OUTB 间的死区时间T 用于防止场效应管V10,V11的同时导通。

校园一卡通系统中RFID读写器的设计

校园一卡通系统中RFID读写器的设计欧阳宏志;肖玉明【摘要】为了加速校园信息化建设,实现校园一卡通系统,设计了RFID读写器.首先概述了RFID读写器的基本原理及结构框架,并对MFRC522芯片做了简单的介绍和说明,然后给出了实际的电路原理图及天线计算方法,并根据关键寄存器的设置给出了对Mifare卡完成读写基本功能的流程图,完成了基本的身份识别和电子钱包等应用.结果表明,读写器读写数据准确,易于扩展,有一定的发展空间.【期刊名称】《电子设计工程》【年(卷),期】2014(022)016【总页数】4页(P109-112)【关键词】校园一卡通;RFID;读写器;MFRC522【作者】欧阳宏志;肖玉明【作者单位】南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001【正文语种】中文【中图分类】TN92射频识别(Radio Frequency Identification,RFID)技术是一种非接触自动识别技术,利用射频信号通过空间耦合(电感或电磁耦合)实现无接触信息传递并通过所传递的信息达到识别目的。

近年来,随着校园数字化、信息化建设的逐步深入,校园内的各种信息资源整合已经进入全面规划和实施阶段,校园一卡通以结合学校正在进行的统一身份认证、人事、学工等应用系统建设,通过共同的身份认证机制,实现数据管理的集成与共享。

校园一卡通系统已经成为校园信息化建设有机的组成部分。

RFID技术的广泛应用,让师生使用一张卡就能够在校内消费、考勤、就医、借书以及办理其他所有事务,从而实现“一卡在手,走遍校园”。

本文设计的RFID读写器系统以STC89C52单片机作为主控芯片,选用高度集成的非接触式读写芯片MFRC522与ISO 14443A/Mifare卡进行无线通信,通过芯片内部发送器驱动读写器天线与Mifare卡和应答机进行通信,同时接收器部分提供一个功能强大和高效的解调和译码电路,用来处理Mifare卡和应答机的信号,实现读卡过程中的防冲撞处理和对卡内E2PROM块内容的读写等功能。

PC929驱动详解

一、驱动电路(由PC923、PC929组合)的构成和电路原理:图4。

9 由PC923、929构成的驱动电路上图为东元7200MA变频器U相的驱动电路图。

15kW以下的驱动电路,则由PC923、PC929经栅极电阻直接驱动IGBT,中、大功率变频器,则由后置放大器将驱动IC输出的驱动脉冲进行电流放大后,再输入IGBT的G、E极。

驱动电路的电源电路,是故障检测的一个重要环节。

不但要求其输出电压范围满足正常要求,而且要求其具有足够的电流(功率)输出能力——带负载能力。

每一相的上、下IGBT驱动电路,因IGBT的触发回路不存在共电位点,驱动电路也需要相互隔离的供电电源。

由开关电源电路中的开关变压器N1绕组输出的交流电压,经整流滤波成直流电压后,又由R68、ZD1(10V稳压管)简单稳压电路处理成正18V和负10V两路电源,供给驱动电路。

电源的OV(零电位点)线接入了IGBT和E极,驱动IC的7、8脚则接入了28V的电源电压。

光电耦合器的输入、输入侧应有独立的供电电源,以形成输入电流和输出电流的通路。

PC2的2、3脚输入电流为+5V*提供。

此处供电标记为+5V*,是为了和开关电源电路输出的+5V相区分。

+5V*供电电路见下图图4。

10。

该电路可看作一简单的动态恒流源电路,R179为稳压管ZD7的限流电阻,稳压管的击穿电压值为3。

5V左右。

基极电流回路中稳压电路的接入,使流过Q8发射结的Ib维持一恒定值,进而使动态Ic也近似为恒定值。

忽略Q8的导能压降,电路的静态输出电压为+5V,但动态输出电压值取决于所接负载电路的“动态电阻值”,而动态输出电流总是接近于恒定的,这就使得驱动电路内部发光二极管能维持一个较为恒定的光通量,从而使传输脉冲信号的“陡峭度”比较理想,使传输特性大为改善。

图4.10 驱动光耦输入侧供电电路由CPU主板来的脉冲信号,经R66加到PC2的3脚,在输入信号低电平期间,PC2形成由+5V*、PC2的2、3脚内部发光二极管、信号源电路到地的输入电流通路,PC2内部输出电路的V1三极管导通,PC2的6脚输出高电平信号(18V峰值),经R65为驱动后置放大电路的Q10提供正向偏流,Q10的导通将正供电电压经栅极电阻R91引入到IGBT的G极,IGBT开通;在输入信号的高电平期间,PC2的3脚也为+5V高电平,因而无输入电流通路,PC2内部输出电路的V2三极管导通,6脚转为负压输出(10V峰值),也经R65为驱动后置放大电路的Q11提供了正向偏流,Q11的导通将供电的负10V电压——IGBT的截止电压经栅极电阻R91引入到IGBT的G极,IGBT关断。

伺服驱动器接线原理图说课讲解

SIGN-

CN2-25

屏蔽地线

FG

屏蔽地线端子

SD15M位置/模拟量控制方式标准接线

SD20MN/SD30MN/SD50MN/SD75MN位置/模拟量控制方式标准接线

相关标签:驱动器,伺服驱动器,

的公共端

DG

控制信号输出端子(除CZ外)的地线公共端

CN2-17

编码器A相信号

AOUT+

Type5

P,S

1.编码器A、B、Z信号差分驱动输出(26LS31输出,相当于RS422);

2.非隔离输出(非绝缘)。

CN2-16

AOUT-

CN2-22

编码器B相信号

BOUT+

Type5

P,S

CN2-10

BOUT-

P,S

CN2-24

编码器Z相信号

ZOUT+

Type5

P,S

CN2-11

ZOUT-

P,S

CN2-2

编码器Z相集电极开路输出

CZ

Type6

P,S

1.编码器Z相信号由集电极开路输出,编码器Z相信号出现时,输出ON(输出导通),否则输出OFF(输出截止);

2.非隔离输出(非绝缘);

3.在上位机,通常Z相信号脉冲很窄,故请用高速光电耦合器

电缆长度较长时,应使用多根芯线并联,减小线路压降。

CN1-1

CN1-2

CN1-3

CN1-4

CN1-16

电源公共地

0V

CN1-24

编码器A+输入

A+

Type4

与伺服电机光电编码器A+相连接

CN1-12

编码器A-输入

A-

与伺服电机光电编码器A-相连接

驱动板原理图

驱动板原理图驱动板是指用于控制电机或其他执行器的电路板,它可以根据输入信号来控制输出的电流、电压等参数,从而驱动执行器按照预定的轨迹或规律进行运动或工作。

在各种自动化设备中,驱动板都扮演着至关重要的角色。

下面我们将介绍驱动板的原理图及其相关知识。

首先,驱动板的原理图通常由电源部分、控制部分和驱动部分组成。

电源部分主要包括电源输入端子、整流滤波电路、稳压电路等,其作用是为整个驱动板提供稳定的工作电压和电流。

控制部分则包括微处理器、输入/输出接口电路、逻辑控制电路等,其作用是接收外部信号,并根据预设的逻辑进行处理和判断,最后控制驱动部分的工作。

驱动部分包括功率放大电路、输出端子等,其作用是根据控制部分的指令,输出相应的电流或电压,驱动执行器进行工作。

其次,驱动板的原理图中,电源部分的设计要保证电压稳定、纹波小、噪声小。

通常会采用整流滤波电路、稳压电路等来实现这一目标。

控制部分的设计则需要考虑信号的输入和处理,因此需要包括输入/输出接口电路、逻辑控制电路等。

这些电路要能够稳定可靠地接收和处理外部信号,并输出控制信号给驱动部分。

驱动部分的设计则需要考虑输出功率和电流的大小,需要根据具体的执行器来选择合适的功率放大电路和输出端子。

最后,驱动板的原理图设计需要考虑整个系统的稳定性、可靠性和安全性。

在电源部分,需要考虑过压、过流、短路等保护电路的设计,以保护整个系统不受损坏。

在控制部分,需要考虑输入信号的滤波和去抖动,以保证系统的稳定性和可靠性。

在驱动部分,需要考虑输出端子的过流、过压保护,以保护执行器不受损坏。

此外,还需要考虑系统的接地和屏蔽,以保证系统的安全性和抗干扰能力。

总而言之,驱动板的原理图设计涉及到电源、控制和驱动等多个方面,需要综合考虑整个系统的稳定性、可靠性和安全性。

只有在这些方面都得到充分考虑的情况下,才能设计出高质量的驱动板原理图,从而保证整个系统的正常工作。

LCD VCOM电压作用

(1) VCOM是LCD的公共电压

(2) VCOM由于物理结构,每个LCD可能不一样

(3) 调节VCOM,根据图像效果,挑一个最OK的值。。

液晶本身感受到的电压是VCOM与Gamma电压之间的压差。但实际上,每一灰阶是由vcom与两正负周期的Gamma voltage组成。所以当正负周期的压差不一样时,就会产生FLICKER(闪烁,抖动)的现象

在LCD面板上主要的电压变化来源有三个:分别是gate driver电压变化,source driver电压变化,以及common电压变化。而这其中影响最大的就是gate driver电压变化(经由Cgs或是Cs)

Байду номын сангаас

source driver的设计制造来说,需要越高电压的工作范围,制程与电路的复杂度相对会提高,成本也会因此而加高

如果一直显示静止的图像,液晶电极上的电压就会一直不变,当撤销电压时,液晶很难回复原状,容易造成液晶损坏。解决这问题的方法就是改变液晶的控制电压的极性,也就是说即使是静止的图像,液晶电极上的电压也一直在翻转。一般的LCD都采用行翻转的形式,通过改变公共端的电压极性VCOM而达到翻转的目的。TCON?IC一般会送出一个M或者POL的信号,我们用这个信号产生VCOM,一般的转换电路使用非们或者运方电路。通过调节VCOM的DC端,我们可以改变LCD的色彩,调节AC端,可以改变LCD的对比度。也许是由于行翻转的缘故,有的LCD会产生水平的条纹(Flicker现象)

TFT电路驱动原理

由CPU通过LCD接口送来的视频信号及时钟经过TCON的时序转换,RGB数据经过D/A转换送到SOURCE

PC929驱动详解

一、驱动电路(由PC923、PC929组合)的构成和电路原理:图4。

9 由PC923、929构成的驱动电路上图为东元7200MA变频器U相的驱动电路图。

15kW以下的驱动电路,则由PC923、PC929经栅极电阻直接驱动IGBT,中、大功率变频器,则由后置放大器将驱动IC输出的驱动脉冲进行电流放大后,再输入IGBT的G、E极。

驱动电路的电源电路,是故障检测的一个重要环节。

不但要求其输出电压范围满足正常要求,而且要求其具有足够的电流(功率)输出能力——带负载能力。

每一相的上、下IGBT驱动电路,因IGBT的触发回路不存在共电位点,驱动电路也需要相互隔离的供电电源。

由开关电源电路中的开关变压器N1绕组输出的交流电压,经整流滤波成直流电压后,又由R68、ZD1(10V稳压管)简单稳压电路处理成正18V和负10V两路电源,供给驱动电路。

电源的OV(零电位点)线接入了IGBT和E极,驱动IC的7、8脚则接入了28V的电源电压。

光电耦合器的输入、输入侧应有独立的供电电源,以形成输入电流和输出电流的通路。

PC2的2、3脚输入电流为+5V*提供。

此处供电标记为+5V*,是为了和开关电源电路输出的+5V相区分。

+5V*供电电路见下图图4。

10。

该电路可看作一简单的动态恒流源电路,R179为稳压管ZD7的限流电阻,稳压管的击穿电压值为3。

5V左右。

基极电流回路中稳压电路的接入,使流过Q8发射结的Ib维持一恒定值,进而使动态Ic也近似为恒定值。

忽略Q8的导能压降,电路的静态输出电压为+5V,但动态输出电压值取决于所接负载电路的“动态电阻值”,而动态输出电流总是接近于恒定的,这就使得驱动电路内部发光二极管能维持一个较为恒定的光通量,从而使传输脉冲信号的“陡峭度”比较理想,使传输特性大为改善。

图4.10 驱动光耦输入侧供电电路由CPU主板来的脉冲信号,经R66加到PC2的3脚,在输入信号低电平期间,PC2形成由+5V*、PC2的2、3脚内部发光二极管、信号源电路到地的输入电流通路,PC2内部输出电路的V1三极管导通,PC2的6脚输出高电平信号(18V峰值),经R65为驱动后置放大电路的Q10提供正向偏流,Q10的导通将正供电电压经栅极电阻R91引入到IGBT的G极,IGBT开通;在输入信号的高电平期间,PC2的3脚也为+5V高电平,因而无输入电流通路,PC2内部输出电路的V2三极管导通,6脚转为负压输出(10V峰值),也经R65为驱动后置放大电路的Q11提供了正向偏流,Q11的导通将供电的负10V电压——IGBT的截止电压经栅极电阻R91引入到IGBT的G极,IGBT关断。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A

1nF(NC) 1nF(NC) 1nF(NC) 1nF(NC)

1nF(NC) 1nF(NC) 1nF(NC) 1nF(NC)

1nF(NC) 1nF(NC) 1nF(NC) 1nF(NC) Vgl

1

Vgl GND

1

GND GND0

1

GND

Rev 0.2 1 of 1

5

4

3

2

1 2 3 4

J6 C43 C44 C45

TSXP TSYP TSXM TSYM J7 C46

1 2 3 4

TSXP TSYP TSXM TSYM J9 C55 C54 C52 C53

1 2 3 4

TSXP TSYP TSXM TSYM BL C51 C50 C48 C49

1

BL Vcom

1

Vcom AVdd

1

AVdd Vgh

1

Vgh

1.VCLK时钟线尽量短,不弯曲,靠近末端加电容,不形成天线辐射 2.HS,VS信号尽量短,靠近末端加电容,不形成天线辐射 3.40P接口位置上拉,50接口位置上拉,保证LCD线拉直不弯曲 4.去掉50P座子上多余的复位信号

Title <LCD_8"> Size A3 Date: Document Number <1> Monday, April 23, 2012 Sheet

RESET VD1 VD3 VD5 VD7 VD9 VD11 VD12 VD14 VD16 VD18 VD20 VD22 SDA VFRAME VCLK TSXM

1

2 3

2

2

R9 100K

LX GND VOout EN

5 4

C15

1 1

0 R8

2 2

C13 10uF C14 100nF

VDD33V

TSYM

1

VDD_IN1 VDD_IN2 VD0 VD1 VD2 VD3 VD4 VD5 VD6 VD7 GND0 VD8 VD9 VD10 VD11 VD12 VD13 VD14 VD15 GND1 VD16 VD17 VD18 VD19 VD20 VD21 VD22 VD23 GND2 LCD_PWR I2CSDA I2CSCL VM VFRAME VLINE VCLK TSXM TSXP TSYM TSYP

2

D4

1

2 1K,1%

Vgl -7v---1mA -6.8-7.1V

B

2

TOUCH 8"

SHUTDOWN VDD GND INT SDA SCL NC NC NC NC

J8

1

1 2 3 4 5 6 7 8 9 10

2

STD VDD33V INT SDA SCL

3 2

RN5 1uF D8 10.4v--32mA 2 C19 100nF C20 100nF L4 4.7uH VDD5V

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49

VDD_5V VDD_5V RESET VD1 VD3 VD5 VD7 VD9 VD11 VD12 VD14 VD16 VD18 VD20 VD22 GND I2CSDA 35 VS VCLK 41 TSXM 45 TSYM 49

VDD5V

1 2 2 2 2 1 2

J3 C5 10uF/16V

D

BL

1

1 2

J5

2

D10 SMB58

C37 10uF

C38 R26 100nF 100K

6

2

1

VD0 VD1 VD2 VD3 VD4 VD5 VD6 VD7 VD8 VD9 VD10 VD11 VD12 VD13 VD14 VD15 VD16 VD17 VD18 VD19 VD20 VD21 VD22 VD23

LCD 7/8"

C12 C11 D2 + R10 100nF 2 30pF(NC) 330pF(NC) 330pF(NC)

10K

2

1

3K,1%

1nF(NC) 1nF(NC) 1nF(NC) 1nF(NC)

R25

0

2

C27

C28

C29

1 1

2 2

INT STD VDD33V AVdd

1

R13

1

1

1uF

1 2 3 4

J4 C26

B

TSXP TSYP TSXM TSYM

U/D GND VCC GND VCC

R/L VCC GND GND VCC TSYM TSYP

Scanning direction Up to down, left to right Down to up, right to left Up to down, right to left Down to up, left to right 0 R24

1

VD0 VD2 VD4 VD6 VD8 VD10 VD13 VD15 VD17 VD19 VD21 VD23 LCD_PWR SCL VLINE TSXP TSYP

C

1

1

1

XC9216A33CMR

1

2

2

1

2

33nF(NC)

CON4

LCD_50P

VDD33V VCLK VFRAME VLINE D7 MBR0530 RESET D3 1uF DAN217 C30 C31 100nF 20-22V 20.6V C17 1uF 3V稳压管 1 -11v R11 -10V CN1 CN2 CN3 C16

5

4

3

2

1

VDD5V

VDD33V MODE:DE/SYNC mode select, Normally pull high. H: DE mode. L: HS/VS mode. CON1 1 RN2 BL 2 NC0 NC1 3 10K(NC) 4 NC2 5 NC3 3.8V Vcom 6 GND0 5.5mA VDD33V 7 Vcom1 8 VCC MODE 9 MODE VM 10 DE VFRAME 11 VS R3 VLINE 12 HS VD7 13 B7 10K VD6 14 B6 VD5 15 B5 VD4 16 B4 VD3 17 B3 VD2 18 B2 VD1 19 B1 VD0 20 B0 VD15 21 G7 VD14 22 G6 VD13 23 G5 VD12 24 G4 VD11 25 G3 VD10 26 G2 VD9 27 G1 VD8 28 G0 VD23 29 R7 VD22 30 R6 VD21 31 R5 VDD33V VDD33V VD20 32 R4 VD19 33 R3 VD18 34 R2 VD17 35 R1 RN3 R7 VD16 36 R0 10K(NC) 10K 37 GND1 VCLK 38 DCLK 39 GND2 L/R 40 L/R U/D 16v 41 U/D Vgh -7v 42 Vgh Vgl 10.4v 43 Vgl AVdd 44 AVdd R12 RN4 RESET 45 RESET 10K 10K(NC) 46 NC4 Vcom DITHB=1,18bit 47 Vcom2 DITHB=0,24bit 48 DITHB 49 GND3 50 NC5 NC6 L5 4.7uH D9 CON2 BL 1N5822 U1 CON2

C

LCD_PWR SDA SCL VM VFRAME VLINE VCLK TSXM TSXP TSYM TSYP

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

15K,1% 15K+ C32 100nF

1

C47 100nF

R18 R14 Vcom

1

2

D6 4.3V稳压管

AVdd

DAN217 1 0

3 1

MBR0530 R17

CON4

10uF

1

3

C18

1

DAN217

D5

2

C21 C22

1

1

R19 6K8+ 8K2

C33 1uF

C34 100nF

Vgh C23 100nF

LCD_40P

FSE EN SS

FB

1

2

7 3 8

5

VDD5V

J1

2

C35

1

R28 10K

R27 10K

R22 69.9K,1%

GND

1

COMP

1

2.2nF

2

LCD_PWR

VDD5V

R21 10K,1%

2

R23 100K

MP1542 C36 10nF

J2

2

4

2

R20 15K

VDD5V

C9 C10 100nF S2 10uF 1 Vin VDD33V L3 10uH

CON50

VDD_5V GND VD0 VD2 VD4 VD6 VD8 VD10 GND VD13 VD15 VD17 VD19 VD21 VD23 LCD_PWREN I2CSCL ENABLE HS 40 GND TSXP GND TSYP GND

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50

2

R15 C25 330K 22pF

1

1K,1% 16.4V--0.5mA C24 100nF