DSPTMS320LF240x片内外设

TMS320C200系列寄存器初始化

TMS320LF240X系列DSP使用时,在掌握了其工作原理和过程之后,就要熟练使用DSP自带的一些资源如:IO口、DSRM、SRAM、EVA、,EVB、SCI、SPI、ADC和WD等等;对这些资源的使用很重要的一点就是对其合理配置和初始化,初始化的关键就是对其相关寄存器的设置,设置寄存器必须了解各位的含义,记住每位的含义是不大现实的;为此,我们专门设计了DSP初始化子程序,注明每个模块所用到的寄存器以及每位的含义,以方便设计。

;Init_DSP.asm.text;----------------------------------------------------------; function: Init DSP DSP初始化子程序; input: ------; output: ------; usege: aCC;==========================================================DSP_Init:;==========================================================; DSP系统初始化;----------------------------------------------------------;ST0------; 15~~13 12 11 10 9 8~~0;ST0 ARP OV OVM 1 INTM DP; 15~13 12 11 10 9 8~5 4 3~2 1~0;ST1 ARB CNF TC SXM C 1 XF 1 PM; ARB---辅助寄存器指针缓冲器:当ARP被加载到ST0,除了使用LST指令外,原有的; ARP值被复制到ARB中;当通过LST#1指令加载ARB时,也把相同的ARB; 值复制到ARP ;; ARP----辅助寄存器指针:ARP选择间接寻址时当前的辅助寄存器AR;当ARP被加载; 时,原有的ARP值被复制到ARB寄存器中;在间接寻址时,ARP可由存储器; 相关指令改变,也可由LARP,MAR,和LST指令改变;当执行LST#1指令; 时,ARP也可加载每ARB相同的值; C---- 进位位:此位在加法结果产生进位时被置为1,或在减法结果产生借位时被清0; 否则,除了执行带有16位移位的ADD或SUB指令外,C在加法后被清除或在减; 法后被设置;在ADD或USB指令时,ADD仅可对进位位进行置位而SUB仅可; 对进位位进行清除,而不会对进位位产生其他影响;移1位和循环指令也可影响; 进位位C,以及SETC、CLRC和LST指令也可影响C;条件转移、调用和返回; 指令可以根据C的状态进行执行;复位时C被置1; CNF----片内DARAM配置位:若CNF=0,可配置的双口RAM区被映射到数据存储空; 间;若CNF=I,可配置的双口RAM区被映射到程序存储空间;CNF位可通过; SETC CNF,CLRC CNF和LST指令修改;R/S/复位时CNF置为0; DP---- 数据存储器页指针:9位的DP寄存器与一个指令字的低七位一起形成一个16; 位的直接寻址地址; INTM---中断模式位:当INTM被置为0时,所有的未屏蔽中断使能;当它被置1,; 所有可屏蔽中断禁止;; OV---- 溢出标志位:该位保存一个被锁存的值,用以指示CALU中是否有溢出发生;; 一旦发生溢出,OV位保持为1直到下列条件中的一个发生时才能被清除; OVM----溢出方式位:当OVM=0时,累加器中结果正常溢出;当OVM=1时,根据; 遇到溢出的情况,累加器被设置为它的最大正值或负值;SETC指令和; CLRC指令分别对该位进行置位和复位;; PM----乘积移位方式:; 若PM=00,乘法器的32位乘积结果不移位直接装入CALU;; 若PM=01,PREG输出左移1位后装入CALU,最低位LSB以0填充;; 若PM=10,PREG输出左移4位后装入CALU,最低位LSB以0填充;; 若PM=11,时PREG输出进行符号扩展右移六位; SXM----符号扩展方式位:当SXM一1时,数据通过定标移位器传送到累加器时将产; 生符号扩展;SXM=0将抑制符号扩展;SXM位对某些指令没有影响;; TC---- 测试/控制标志位:在下述情况之一,TC位被置1:由BIT或BITT指令测; 试的位为1;当利用NORM指令测试时,累加器的两个最高有效位"异或"; 功能为真;条件转移、调用和返回指令可根据TC位的条件来执行;; BIT、BITT、CMPR、LST和NORM指令影响TC位; XF---- XF引脚状态位:该位决定XF引脚的状态;SETCXF指令可对位XF进行置位,; 而CLRCXF指令可对其进行清0;复位时XF置1;SCSR1------系统控制和状态寄存器1---地址7018H ; D15---保留位; D14---CLKSRC。

内容3--德州仪器(TI)的系列DSP

通过PB总线完成数据传递

PB总线能把存储在程序空间的数据操作 数(如系数表)传送到乘法器和加法器 中进行乘/累加运算,或者在数据移动指 令(MVPD和READA)中传送到数据空 间。这种能力再加上双操作数读的特 性,支持单周期3操作数指令的执行,如 FIRS指令。

21:51:26

21:51:26

15

第二部分 DSP硬件结构

在这一部分中,我们介绍:

TMS320LF240X的 硬件结构 TMS320VC3X的硬 件结构 TMS320C6201的 硬件结构 重点介绍: TMS320C54XX硬 件结构特点 ★

21:51:26 17

§2-1 TMS320LF240X的硬件 结构

各大公司定点DSP性能比较

21:51:26

13

浮点DSP的性能比较

21:51:26

14

DSP主要供应商的网站

德州仪器(TI):http:\\, http:\\ 模拟器件(ADI): http:\\ 郎讯科技:http:\\ 莫托罗拉:http:\\

21:51:26 11

定点DSP与浮点DSP

在DSP运用中的数据保真性很重 要,因此在定点DSP中必须要特别 考虑运算过程中可能出现的溢出等 情况。在定点DSP中,累加器一般 比存储器字长大,并特别设置了溢 出模式位,可以选择在溢出情况下 的处理方法,从而尽量降低数据失 真。

21:51:26 12

57

ALU框图:

21:51:26

58

累加器:

累加器ACCA和ACCB存放从ALU或乘 法器/加法器单元输出的数据,累加器也 能输出到ALU或乘法器/加法器中。

21:51:26

59

第1讲 TI DSP概述

8-level hardware stack

Repeat count

2 status registers

Peripheral Bus

WD Timer CAN SCI SPI

A/D Converter

10 bits, 16 channels

精选课件ppt

10

C2000™: 参数选择列表

‘F240 ‘C240 ‘F241 ‘C242 ‘F243 ‘LF2402 ‘LC2402 ‘LC2404 ‘LF2406 ‘LC2406 ‘LF2407

16 500ns

Yes Yes Yes 41 Yes Yes 3.3V 144 LQFP Today

$10.45

**C28x Broad Sampling Mid 2001**

精选课件ppt

11

F2810/F2812: 业界最强大的控制专用DSP

Code security

TMX today, TMS Production mid 2003

Program Flash 32K words

Program / Data / I/O Buses

C2xx DSP Core

Event Man2aTgimerers

2 5timCeorms pares 58cPomWpMarOesutputs 8 PDWeMadoubtapnudtslogic Dea3dInbpauntdClaopgticures 3 in2puQtEcPapctuhraensnels

Yes Yes Yes 41 Yes No 3.3V 100 LQFP Today

$9.95

30/40

32K 2.5K

4 10/16 6/4

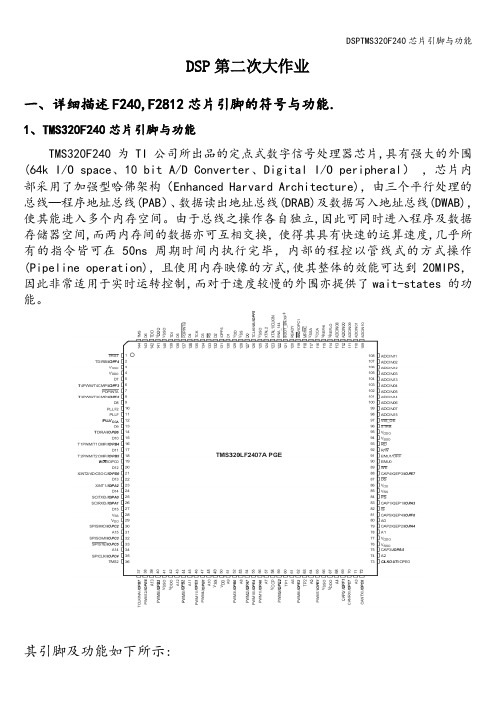

DSPTMS320F240芯片引脚与功能

DSP第二次大作业一、详细描述F240,F2812芯片引脚的符号与功能.1、TMS320F240芯片引脚与功能TMS320F240为TI公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral),芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间。

由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功能。

其引脚及功能如下所示:2、TMS320F2812芯片引脚与功能德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motorcontrol, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。

针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C语言的环境中搭配汇编语言来撰写程序。

值得一提的是,F28xDSP核心支持特殊的IQ—math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。

F28x 系列DSP预计发展至400MHz,目前已发展至150MHz的Flash型式。

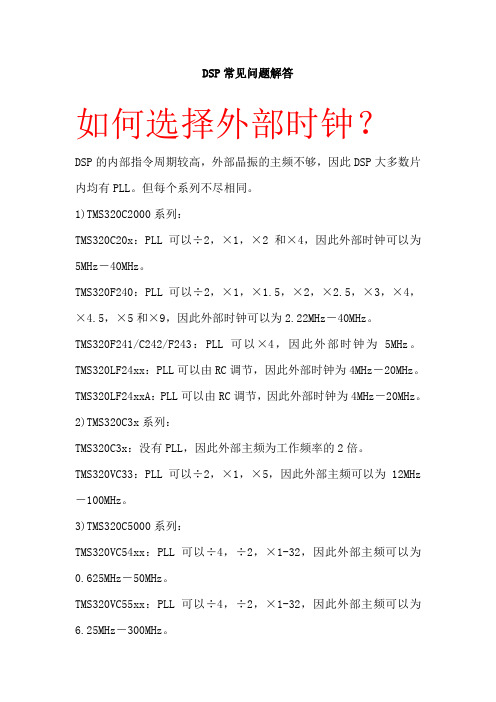

DSP常见问题解答

DSP常见问题解答如何选择外部时钟?DSP的内部指令周期较高,外部晶振的主频不够,因此DSP大多数片内均有PLL。

但每个系列不尽相同。

1)TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部时钟可以为5MHz-40MHz。

TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部时钟可以为2.22MHz-40MHz。

TMS320F241/C242/F243:PLL可以×4,因此外部时钟为5MHz。

TMS320LF24xx:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

TMS320LF24xxA:PLL可以由RC调节,因此外部时钟为4MHz-20MHz。

2)TMS320C3x系列:TMS320C3x:没有PLL,因此外部主频为工作频率的2倍。

TMS320VC33:PLL可以÷2,×1,×5,因此外部主频可以为12MHz -100MHz。

3)TMS320C5000系列:TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为0.625MHz-50MHz。

TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主频可以为6.25MHz-300MHz。

4)TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主频可以为11.8MHz-300MHz。

TMS320C67xx:PLL可以×1和×4,因此外部主频可以为12.5MHz-230MHz。

240X概述

调制解调器、网络系统、中心局交换机、数字音频广 播设备等;C67x是32位浮点芯片,可用于基站数字 波束形成、图像处理、语音识别和3D图形等。 2.1.1 TMS320C2000系列 TMS320C2000系列DSP将闪存、10位A/D、CAN(控制器 局域网)接口等各种片内外设集成在一起,主要包 括TMS320C20x、TMS320C240x及TMS320C28x等产品。 1. TMS320C20x系列 TMS320C20x系列主要用于电话、数字相机、嵌入式家 电设备等。

事件管理器B(EVB) CAP4/QEP3/IOPE7: CAP5/QEP4/IOPF0: CAP6/IOPF1: PWM7/IOPE1∼PWM12/IOPE6: T3PWM/T3CMP/IOPF2: T4PWM/T4CMP/IOPF3: TDIRB/IOPF4:通用计数器方向选择(EVB) 1:加计数;0:减计数; TCLKINB/IOPF5:通用计数器(EVB)外部时钟输入

DS

地址、数据、存储器控制信号 A0-A15: D0-D15: DS*:外部数据空间选通; PS*:外部程序空间选通; IS*:外部I/O空间选通; R/W*:读写选通,指明与外围器件信号的传送方向; W/R*/IOPC0:为R/W*的反; WE*:对外部3个空间写;

RD*:对外部3个空间读; STRB* :外部存储器选通; READY: 插入等待状态; MP/MC* :微处理器/微计算机(控制器)方式选择 ENA_144:=1,使能外部信号; =0,无外部存储器。 VIS_OE*:可视输出可能。 可视输出的方式下,外部数据总线为输出时,该引 脚有效,可用作外部编码逻辑,以防止数据总线冲 突。

事件管理器A(EVA) CAP1/QEP1/IOPA3:捕捉输入1/正交编码脉冲输入; CAP2/QEP2/IOPA4: CAP3/IOPA5: PWM1/IOPA6:比较PWM输出或通用IO; PWM2/IOPA7: PWM3/IOPB0: PWM4/IOPB1:

DSP TMS320F240芯片引脚与功能

DSP第二次大作业一、详细描述F240,F2812芯片引脚的符号与功能。

1、TMS320F240芯片引脚与功能TMS320F240为TI公司所出品的定点式数字信号处理器芯片,具有强大的外围(64k I/O space、10 bit A/D Converter、Digital I/O peripheral) ,芯片内部采用了加强型哈佛架构(Enhanced Harvard Architecture),由三个平行处理的总线─程序地址总线(PAB)、数据读出地址总线(DRAB)及数据写入地址总线(DWAB),使其能进入多个内存空间。

由于总线之操作各自独立,因此可同时进入程序及数据存储器空间,而两内存间的数据亦可互相交换,使得其具有快速的运算速度,几乎所有的指令皆可在50ns 周期时间内执行完毕,内部的程控以管线式的方式操作(Pipeline operation),且使用内存映像的方式,使其整体的效能可达到20MIPS,因此非常适用于实时运转控制,而对于速度较慢的外围亦提供了wait-states 的功能。

其引脚及功能如下所示:2、TMS320F2812芯片引脚与功能德州仪器所生产的TMS320F2812 数字讯号处理器是针对数字控制所设计的DSP,整合了DSP 及微控制器的最佳特性,主要使用在嵌入式控制应用,如数字电机控制(digital motor control, DMC)、资料撷取及I/O 控制(data acquisition and control, DAQ)等领域。

针对应用最佳化,并有效缩短产品开发周期,F28x 核心支持全新CCS环境的C compiler,提供C 语言中直接嵌入汇编语言的程序开发介面,可在C语言的环境中搭配汇编语言来撰写程序。

值得一提的是,F28xDSP 核心支持特殊的IQ-math 函式库,系统开发人员可以使用便宜的定点数DSP 来发展所需的浮点运算算法。

F28x 系列DSP预计发展至400MHz,目前已发展至150MHz的Flash型式。

DSP课件第二章TMS320LF240x硬件结构

当片内外设产生中断时,CPU响应中断并执行相应的中断服务程序 对片内外设进行操作。

05

TMS320LF240x的电源管理和低功耗

模式

电源管理单元

电源管理单元(PMU)是TMS320LF240x芯片中的一个重要组成部分,负责控制芯 片的电源供应和功耗管理。

PMU包含多个电源域,可独立控制各个电源域的开启和关闭,以实现灵活的功耗管 理。

较

他设备进行数据交换,可配 置为发送或接收模式。

器

比较器用于检测电压或电平 是否达到预设值,输出电平

可配置为高或低,常用于 PWM控制或阈值检测。

看门 狗定 时器

片内外设的访问方式

直接访问

通过特定的寄存器地址直接读写片内外设的控制寄存器和数据寄 存器。

间接访问

通过特定的寄存器地址读写片内外设的控制寄存器来配置片内外设, 再通过数据寄存器进行数据传输。

PMU还具有过压和欠压保护功能,以确保芯片在异常电源条件下能够安全运行。

低功耗模式

TMS320LF240x支持多种低功 耗模式,以便在不需要时降低芯

片功耗。

低功耗模式通过关闭不需要的内 部时钟和电源域来实现功耗降低。

在低功耗模式下,芯片的某些功 能将被禁用,但仍可以响应外部 事件或中断,并在必要时唤醒。

需求。

输入输出电平

02

TMS320LF240x的输入输出电平一般为CMOS电平,能够与

TTL和CMOS电路兼容。

驱动能力

03

TMS320LF240x的驱动能力较强,能够驱动较大规模的外部电

路。

封装形式

• TMS320LF240x的封装形式一般为塑封或陶瓷封装,具体 取决于应用需求和生产厂家。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

看门狗(WD)定时器模块用来监视软件和硬件操作,在软件进入 一个不正确的循环或者CPU出现暂时性异常时,WD定时器溢出以产 生一个系统复位。大多数芯片的异常操作和CPU非正常工作的情况 都能通过看门狗的功能清除和复位。因此看门狗的监视功能可增强 CPU的可靠性,以确保系统运行的安全和稳定。

(1)WD计数寄存器(WDCNTR)——地址7023h

8位WD计数寄存器存放WD计数器的当前值D7~D0。WDCNTR 是一个只读寄存器,复位后为0,写寄存器无效。由预定标器的输出 提供计数时钟。

(2)WD复位关键字寄存器(WDKEY)——地址7025h

当55h及紧接其后的AAh(复位关键字)写入WDKEY时,将清除 WDCNTR。 其 他 任 何 值 的 结 合 写 入 或 写 入 任O复用控制寄存器

I/0复用控制寄存器用来控制多路选择器,选择功能复用引脚是作 为特殊功能(MCRx.n=1)还是通用I/0功能(MCRx.n=0)。

2、数据和方向控制寄存器

1、端口A数据和方向控制寄存器 (PADATDIR) ——地址7098h D15~D8 AnDIR——定义IOPAn(n:7~0)引脚的方向和电平。

WDCLK=(CLKOUT)/512 当CLKOUT=40MHz时,WDCLK=78125Hz是一个典型值。 除 HALT 低 功 耗 模 式 外 , 无 论 片 内 任 一 寄 存 器 的 状 态 如 何 。 WDCLK都将使能WD定时器功能。

WD模块的结构框图

WD模块有3个控制寄存器对其进行控制和管理:

1、 看门狗(WD)定时器模块的结构

看门狗(WD)定时器模块的结构如下图所示。WD模块的所有寄 存器都是8位长,该模块与CPU的16位外设总线的低8位相连。

看 门 狗 定 时 器 的 时 钟 ( WDCLK) 是 一 个 低 频 时 钟 , 由 CPU 的 CLKOUT产生。当CPU处于低功耗模式IDLE1和IDLE2时,仍能保证 看门狗继续计数。仅当看门狗使能时,WDCLK才有效。WDCLK的 频率由下式计算:

8 位 WDKEY 是 一 个 可 读 写 寄 存 器 , 复 位 后 为 0 。 读 该 寄 存 器 WDKEY并不返回最近的关键字值,而是返回WDCR的内容。

(3)WD定时器控制寄存器(WDCR)——地址7029h

8位WDCR用来存放看门狗配置的控制位。

2、 看门狗(WD)定时器的操作

( 1 ) 、 WD 计 数 器 ( WDCNTR) 溢 出 或 向 WD 复 位 关 键 字 寄 存 器 (WDKEY)写入一个不正确的值

当系统不正常时,也就不能给WDKEY写入正确值使WDCNTR清0, 则WDCNTR将计满溢出,并在一个WDCLK(或用WDCLK除以预定标因 子)时钟后发生系统复位操作。

任何其他次序的写入55h和AAh值或写入其他值都不能使WDCNTR 清0,从而使系统复位。

(2)、使用WD检查位 WD定时器控制寄存器(WDCR)的检查位(WDCHK2~WDCHK0)一直 和一个二进制常量101相比较。如果WD检查位与这个值不匹配,就会产 生一个系统复位。所以一旦软件执行了错误的WDCR写操作或一个外部 激励干扰(例如电压尖峰或其他干扰源)破坏了WDCR的内容,即除101以 外的任何值写到WDCR的D5~D3位都会产生一个系统复位。 注意,向WDCR写入值时必须包括写到D5~D3的值101。 当系统上电复位时,看门狗就被使能。WD定时器被缺省为最快的 WD速率。一旦复位由内部释放,CPU就开始执行程序,同时WD定时器 就开始计数。因此为了避免过早发生复位,应在程序刚开始时就对WD进 行配置。

3、程序举例

(1)IOPx0~ IOPx7(x=A、B、C、E、F)轮流设置低电平输出

当系统正常工作时,WD计数器WDCNTR以WD控制寄存器所选的 速 率 进 行 增 计 数 , 在 WDCNTR 溢 出 前 , 只 要 给 复 位 关 键 字 寄 存 器 WDKEY 写 入 一 个 正 确 值 ( 先 写 入 5 5 h, 紧 接 着 写 入 AAh) 就 可 以 使 WDCNTR清0,即从0开始计数而不会产生溢出。

9.2 数字输入/输出(I/O)模块

LF240x采用哈佛结构,有3个独立的空间:程序空间、数据空间和 I/O空间。3个空间对外共用一个16位地址总线和一个16位数据总线,并 以3个片选线、和区分不同空间。其中,I/O空间可接外部设备,是 LF240x与外部设备联系的接口。

数字I/O模块也具有连接外部设备的功能,是LF240x除I/O空间外另 一个与外部设备联系的接口。

0 定义对应的引脚IOPA7~IOPA0为输入。 1 定义对应的引脚IOPA7~IOPA0为输出。 D7~D0 IOPAn——I/O引脚名(n:7~0)。 如果AnDIR=0即引脚IOPAn(n:7~0)为输入时, 0 对应的I/O引脚输入的值为低电平。 1 对应的I/O引脚输入的值为高电平。 如果AnDIR=1即引脚IOPAn(n:7~0)为输出时, 0 设置相应的引脚使其输出为低电平。 1 设置相应的引脚使其输出为高电平。

控制两种功能的选择。

(2)数据和方向控制寄存器(PxDATDIR,x=A,B,C,D,E,F)

当引脚作为通用I/O时,用来控制选择各I/O引脚的数据方向(输入 还是输出)和当前引脚对应的电平(高或低)。读通用I/O引脚的电平或 向引脚输出电平,实际上是对相应的寄存器(PxDATDIR)进行读写操 作。

LF240x有41个数字I/O口,其中绝大多数具有另一功能,“另一功能” 都是SCI、SPI等片内外设模块的功能引脚。数字I/O口是第二功能。

LF240x有41个数字I/O口,所有这些共享引脚的功能可通过数 字I/O模块中的9个16位控制寄存器来控制。

控制寄存器可以分为两类。

(1) I/O复用控制寄存器(MCRx,x=A,B,C)