集成电路PLL后端设计研究与实现

毕业设计论文:PLL锁相环电路

1摘 要随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。

本次毕业设计的主要任务是,采用0.180.18μμm CMOS 工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL 锁相环电路,设计重点为PLL 锁相环电路的版图设计,设计工具为Laker 。

本论文介绍了PLL 锁相环电路的基本原理以及其完整的版图设计结果。

本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。

求。

关键词:PLL 锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.180.18μμm CMOS 工艺工艺AbstractWith the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly.The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the . The design focus on the layout of the PLL circuit, and the design tools is the Laker.This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements.Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process目 录 (11)摘 要.............................................................................................................................. (22)Abstract .......................................................................................................................... (44)第1章 绪论................................................................................................................ (44)1.1 锁相技术的发展.............................................................................................. (44)1.2 锁相环路的主要特性......................................................................................1.3 PLL锁相环的应用领域 (5)第2章 基于CMOS锁相环的电路设计 (7)2.1 锁相环的基本组成.......................................................................................... (77) (77)2.2 锁相环工作原理.............................................................................................. (88)2.3 鉴相器..............................................................................................................2.3.1 鉴频鉴相器(PFD) (9) (110)2.3.2 鉴频鉴相器设计.................................................................................. (110)2.4 环路滤波器....................................................................................................11 (11)2.5 压控振荡器....................................................................................................第3章 关于COMS锁相环的版图设计 (12) (112)3.1 电路设计........................................................................................................3.2 版图设计........................................................................................................ (112) (113)3.2.1 版图设计规则检查.............................................................................. (113)3.2.2 注意事项..............................................................................................3.3 锁相环的版图设计........................................................................................ (115) (117)第4章 结束语............................................................................................................ (118)参考文献...................................................................................................................... (119)致谢..............................................................................................................................第1章 绪论1.1锁相技术的发展 锁相技术起源于20世纪30年代,提出无线电调幅信号的锁相同步检波技术。

PLL设计关键基础及基本参数确定方法

PLL设计关键基础及基本参数确定方法PLL(锁相环)是一种电路设计技术,用于将输入信号的频率和相位合成为与参考信号相同的输出信号。

它在各种应用领域中具有广泛的应用,包括通信系统、数据传输、时钟发生器、频率合成器等。

1.建立模型:确定所需的频率范围和准确度,并选择适当的振荡器作为参考信号源。

建立时钟和相位比较器的模型,以及低通滤波器等组成部分的模型。

2.频率范围和准确度:确定PLL所需的输出频率范围和准确度。

这取决于具体的应用需求,如通信系统中需要的频率范围和准确度。

一般来说,更高的频率范围和准确度要求会导致设计更复杂的PLL电路。

3.反馈环:选择适当的反馈环型式,如基本PLL、全数字PLL或混合模拟数字PLL。

这取决于应用需求和设计复杂度。

基本PLL适用于频率较低的应用,但对相位噪声较敏感。

全数字PLL则采用数字环路滤波器,具有更高的鲁棒性和可控性。

4. 相位锁定范围(Phase Locked Loop Range):确定PLL的相位锁定范围,即输入信号的相位偏移量。

这取决于具体应用中的信号变化范围和要求。

较大的相位锁定范围会导致更高的设计复杂度。

5.闭环带宽:确定PLL的闭环带宽,即相位比较器输出与输出信号的相位偏差之间的关系。

较大的闭环带宽可以提供更高的锁定速度,但可能会导致更高的相位噪声。

6. 电源抑制比(Power Supply Rejection Ratio,PSRR):确定PLL对电源噪声的抑制能力。

电源噪声可能会影响PLL的性能,因此需要设计合适的滤波器和抑制电源噪声的能力。

7.噪声性能:确定PLL对输入信号噪声和环路滤波器自身噪声的敏感度。

这取决于环路滤波器的设计和反馈环的类型。

一般来说,全数字PLL 具有更好的噪声性能。

8.稳定性和抖动:确定PLL的稳定性和抖动性能。

PLL需要能够在各种工作条件下保持稳定,不受温度、电源变化等因素的影响。

抖动性能衡量了PLL输出信号的时钟稳定性。

adisimpll锁相环设计过程

adisimpll锁相环设计过程锁相环(Phase-Locked Loop,PLL)是一种常用于时钟和信号恢复的电子电路。

它可以将输入信号的频率、相位和幅度与参考信号进行比较,然后通过调整其内部振荡器的频率和相位来保持与参考信号的同步。

在现代电子系统中,锁相环已成为许多应用的核心部件,例如通信系统、数据转换和数字信号处理等。

锁相环的设计过程通常包括以下几个主要步骤:1.确定锁相环的规格要求:首先需要确定系统的特定需求,包括输入和输出信号的频率范围、带宽、相位噪声要求以及抖动限制等。

这些规格要求将直接影响锁相环的设计参数和性能。

2.选择合适的锁相环架构:根据系统的特定需求,选择适合的锁相环架构。

常见的锁相环架构包括基于电压控制振荡器(Voltage-Controlled Oscillator,VCO)的基本锁相环、带自由运行振荡器(Free-Running Oscillator)的环-环(Ring-Oscillator)锁相环和数字控制振荡器(Digital-Controlled Oscillator,DCO)的混合锁相环等。

3.设计相位频率检测器:锁相环中的相位频率检测器(Phase-Frequency Detector,PFD)用于比较参考信号和反馈信号的相位和频率差异,并将其转化为控制信号。

常见的PFD电路包括EXOR门和带有多频偏的PFD等。

4.设计环路滤波器:设计环路滤波器用于平稳化锁相环的控制信号。

环路滤波器通常采用低通滤波器结构,能够滤除高频噪声和不稳定性。

5.设计振荡器:根据系统的频率范围和性能要求,设计合适的振荡器。

常见的VCO设计包括压控晶体振荡器(Voltage-Controlled Crystal Oscillator,VCXO)和频率可调振荡器(Voltage-Controlled Oscillator,VCO)。

6.设计控制电路:根据锁相环的设计需求,设计合适的控制电路。

《应用于LVDS的锁相环电路研究》

《应用于LVDS的锁相环电路研究》一、引言随着科技的快速发展,现代电子设备在速度、准确性和效率等方面有着更高的需求。

在此背景下,锁相环(PLL)电路因其能够提供精确的频率和相位同步功能,在通信、数据传输和时钟恢复等领域得到了广泛应用。

而LVDS(低电压差分信号)作为一种高速、低噪声的数据传输技术,与锁相环电路的结合更是为高速数据传输提供了可靠的技术支持。

本文将针对应用于LVDS 的锁相环电路进行深入研究。

二、LVDS技术概述LVDS是一种用于高速数据传输的低电压差分信号技术。

其优点包括低功耗、低噪声、高数据速率以及高抗干扰能力等。

LVDS信号传输过程中,通过差分驱动器和接收器将数据以差分形式进行传输,大大提高了数据的稳定性和可靠性。

三、锁相环电路的基本原理锁相环电路是一种能够自动调整输出信号的频率和相位,使其与输入信号保持一致或特定关系的电路。

它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。

鉴相器用于检测输入信号与输出信号之间的相位差;环路滤波器则用于滤除鉴相器输出中的高频噪声和干扰,为压控振荡器提供稳定的控制电压;压控振荡器则根据控制电压调整其输出频率和相位。

四、应用于LVDS的锁相环电路设计在LVDS系统中,锁相环电路的作用是恢复和同步接收到的数据时钟信号。

针对LVDS的特殊需求,锁相环电路设计需考虑以下因素:1. 高速性能:为适应LVDS的高速数据传输需求,锁相环电路应具备高速响应和快速锁定能力。

2. 低噪声:LVDS系统要求低噪声信号传输,因此锁相环电路应具备低噪声性能。

3. 稳定性:为保证数据的准确传输,锁相环电路应具有良好的稳定性。

根据上述要求,应用于LVDS的锁相环电路设计可以采取以下策略:五、锁相环电路的硬件设计在设计针对LVDS系统的锁相环电路时,我们需要综合考虑硬件架构和元件选择。

鉴相器是电路的核心部分之一,应选择具有高灵敏度和低噪声特性的鉴相器,以准确检测输入信号与输出信号的相位差。

锁相环电路设计

锁相环电路设计PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

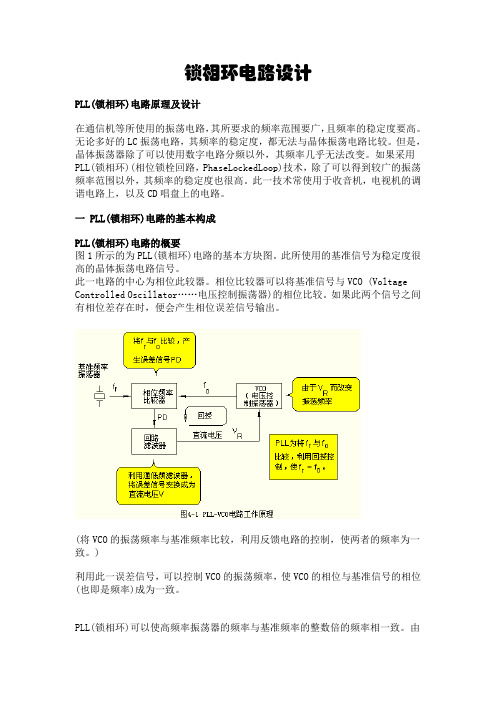

一 PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

如果有相位差存在时,便会产生正或负的脉波输出。

PLL设计关键基础及基本参数确定方法

PLL设计关键基础及基本参数确定方法PLL (Phase-Locked Loop) 是一种广泛应用于电子电路和通信领域的反馈控制系统。

它常被用于生成稳定的时钟信号、频率合成、信号调制和解调等应用。

PLL的设计基础包括如下几个关键要素:1. Voltage-Controlled Oscillator (VCO,压控振荡器):VCO是PLL中最重要的组件之一,它的频率输出受到控制电压的影响。

在PLL中,VCO用来将输入信号的频率与参考时钟频率进行比较调节,从而输出稳定的频率信号。

根据应用的要求,选择恰当的VCO类型和工作频率范围非常重要。

3. Loop Filter (环路滤波器):环路滤波器用来滤除PD输出中的高频噪声,并提供平滑的控制电压给VCO。

它由一个或多个滤波器组成,可以使用电容和电阻等元件实现。

设计环路滤波器需要综合考虑相位噪声、上升时间、锁定时间和抗干扰能力等因素。

4. Divide-by-N Counter (除N计数器):除N计数器控制输出信号的频率与参考时钟信号之间的整数倍关系。

通过改变N的值,可以实现频率合成和频率分频。

除N计数器可以使用预置计数器、可编程计数器或振荡器和计数器组成的结构。

确定PLL的基本参数和性能要考虑以下几个方面:1. 幅值环路带宽 (Loop Bandwidth):决定了PLL的跟踪速度和抗噪声能力。

较大的环路带宽可以提高跟踪速度,但可能导致更高的相位噪声。

选择合适的环路带宽要综合考虑设计的应用需求。

2. 锁定时间 (Lock Time):是指PLL从失锁状态到稳定锁定状态所需的时间。

较短的锁定时间可以提供更好的动态性能和抗抖动能力。

锁定时间和环路带宽之间存在着一定的折衷关系。

3. 输出频率范围 (Output Frequency Range):PLL的输出频率范围取决于VCO的工作频率范围和除N计数器的最大除数。

选择合适的VCO和除N计数器是确保输出频率范围的关键。

《基于FPGA的PLL+DDS的频率合成器》范文

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着通信技术的飞速发展,频率合成器作为电子系统中的关键部件,其性能和稳定性直接影响到整个系统的性能。

本文将详细介绍一种基于FPGA(现场可编程门阵列)的PLL(锁相环)+DDS(直接数字合成器)的频率合成器,并对其设计原理、实现方法及性能优势进行深入探讨。

二、PLL+DDS频率合成器的工作原理PLL+DDS频率合成器通过将PLL与DDS结合,利用两者的优势来达到高精度、高稳定性的频率输出。

PLL模块主要负责跟踪和生成参考频率,而DDS模块则能够快速生成多种频率的波形。

FPGA作为核心控制器,负责协调PLL和DDS模块的工作,实现频率的合成和输出。

三、设计实现1. 硬件设计在硬件设计方面,PLL+DDS频率合成器主要包含FPGA、PLL模块、DDS模块以及输出电路等部分。

其中,FPGA作为核心控制器,负责协调整个系统的运行。

PLL模块采用高精度的锁相环电路,以实现稳定的参考频率输出。

DDS模块则采用数字方式生成多种频率的波形。

2. 软件设计在软件设计方面,需要编写FPGA的程序代码来实现对PLL 和DDS模块的控制。

通过配置FPGA的IO口,实现对PLL和DDS模块的驱动和控制。

同时,还需要编写相应的算法程序,以实现频率的合成和输出。

四、性能优势基于FPGA的PLL+DDS频率合成器具有以下优势:1. 高精度:PLL和DDS的结合使得频率合成器具有高精度的频率输出。

2. 高稳定性:通过PLL模块的锁相环电路,可以实现稳定的参考频率输出,从而提高整个系统的稳定性。

3. 快速响应:DDS模块采用数字方式生成波形,具有快速响应的特点,可以快速调整输出频率。

4. 灵活性:FPGA的可编程性使得频率合成器具有很高的灵活性,可以方便地实现多种功能的扩展和升级。

五、应用领域基于FPGA的PLL+DDS频率合成器在通信、雷达、电子测量等领域具有广泛的应用。

例如,在通信系统中,它可以为基站提供稳定的射频信号;在雷达系统中,它可以为雷达提供精确的扫描频率;在电子测量领域,它可以用于信号源的生成和测试等。

单芯片高集成高速pcie加密卡设计和实现

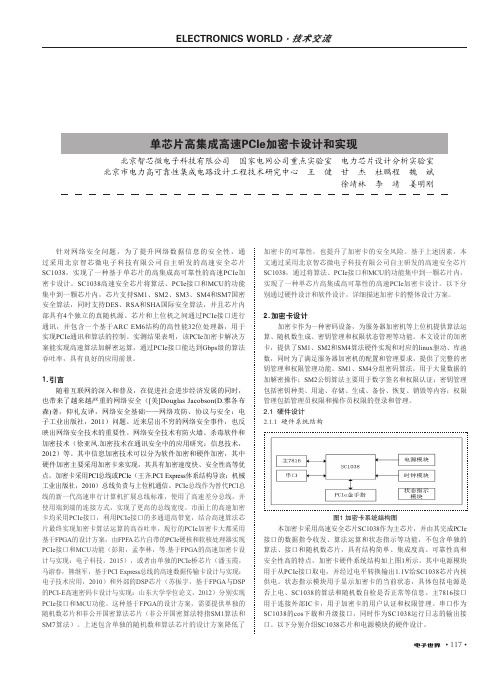

• 117•针对网络安全问题,为了提升网络数据信息的安全性,通过采用北京智芯微电子科技有限公司自主研发的高速安全芯片SC1038,实现了一种基于单芯片的高集成高可靠性的高速PCIe加密卡设计。

SC1038高速安全芯片将算法、PCIe接口和MCU的功能集中到一颗芯片内,芯片支持SM1、SM2、SM3、SM4和SM7国密安全算法,同时支持DES、RSA和SHA国际安全算法,并且芯片内部具有4个独立的真随机源。

芯片和上位机之间通过PCIe接口进行通讯,并包含一个基于ARC EM6结构的高性能32位处理器,用于实现PCIe通讯和算法的控制。

实测结果表明,该PCIe加密卡解决方案能实现高速算法加解密运算,通过PCIe接口能达到Gbps级的算法吞吐率,具有良好的应用前景。

1.引言随着互联网的深入和普及,在促进社会进步经济发展的同时,也带来了越来越严重的网络安全([美]Douglas Jacobson(D.雅各布森)著,仰礼友译,网络安全基础——网络攻防、协议与安全:电子工业出版社,2011)问题。

近来层出不穷的网络安全事件,也反映出网络安全技术的重要性。

网络安全技术有防火墙、杀毒软件和加密技术(徐亚凤.加密技术在通讯安全中的应用研究:信息技术,2012)等。

其中信息加密技术可以分为软件加密和硬件加密,其中硬件加密主要采用加密卡来实现,其具有加密速度快、安全性高等优点。

加密卡采用PCI总线或PCIe(王齐.PCI Express体系结构导读:机械工业出版社,2010)总线负责与上位机通信。

PCIe总线作为替代PCI总线的新一代高速串行计算机扩展总线标准,使用了高速差分总线,并使用端到端的连接方式,实现了更高的总线宽度。

市面上的高速加密卡均采用PCIe接口,利用PCIe接口的多通道高带宽,结合高速算法芯片最终实现加密卡算法运算的高吞吐率。

现行的PCIe加密卡大都采用基于FPGA的设计方案,由FPFA芯片自带的PCIe硬核和软核处理器实现PCIe接口和MCU功能(彭阳,孟李林,等.基于FPGA的高速加密卡设计与实现:电子科技,2015),或者由单独的PCIe桥芯片(潘玉霞,马游春,熊继军,基于PCI Express总线的高速数据传输卡设计与实现:电子技术应用,2010)和外部的DSP芯片(苏振宇,基于FPGA与DSP 的PCI-E高速密码卡设计与实现:山东大学学位论文,2012)分别实现PCIe接口和MCU功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路 P L L后端设计研究与实现

摘 要: 本 文分析 了集成电路锁相 环 电路 的原理 , 通过 对 电路 的研 究对后端设 计进行分析 , 明确版 图设 计要 点 , 以试 图

使后端设计 对会 影响模 块性能等 方面加 以改善。

关键 字: 集成电路 ; P L L ; 版 图设 计

十分 注意 。

叠

的频率可 能与输 出信号 的频率 相差很大 ,此 时 P F D和 电荷泵 改变控制 电 压, 使输 出信号逼近输入信 号。当输入信号频率 和输出信号频率足够接近 时, P F D就被 当作 鉴相器 , 进 行相位锁定 。当相位差 降到零并且 电荷泵保 持相对空 闲时 , 环路就锁定 了。图一是 电荷泵锁相环 结构系统模型框 图。

性, 在某些 场合 ( 如频率 综合信号 源或 固态信号 源等 ) 得到 了非 常广泛韵

应用 。 而P L L 对版 图设计的要求非常高 , 成 功的 P L L 设计可 以说一半 以上 要归 功于版 图设计 。 1 镇相环结构 下面 就用一个 比较典型 的 P L L结构来说 明电路 中需要后 端设计需要

电荷泵 的功能是把 P F D的两个 电压输 出转化成 为电流差输 出 , 输出 电流的平 均值与 P F D的输入差成正 比。 图二 中采用 M O S 开关来 实现电荷 泵 的充放电 。 M1和 M2为电流源 , 它们为环路滤波器提供恒定 的充放电电 流; M 3和 M 4 为电压控制 M O S 开关 ,它们负责控制充 电或放 电通路 的打 开 和断开 ; V B 2 和V B 1 分别为 M1 和M 2 的栅极偏置 电压 ,他们分别 由两 个基 准电压源提供 。可 以在 D O WN和 M 3 的栅极之间插入一 个互补传 输 门, 使延 迟时间相等 。 在此 电路 中 , M O S 开关 的尺寸必须要考虑 , 开关 应尽 量小 , 同时 P管 和 N管的寄生效应要尽量一致 。 所 以在绘制版 图的时候要

出信 号频率 的稳 定度 的一个 描述 ( 频率 的精 度取决于输入 的参考时钟 信 号 的频率精度 ) , 相位噪声是 从频域 的角度 对输 出信号频谱 纯度 的一个 描

述 。两者是相互关联 的。

2版圈设计

2 . 1电荷 泵

考虑 的要 点 。 一般使 用的 P L L采用的是 电荷泵 型锁相环 , 环路 由鉴频鉴相

2. 2 VCo

压控 振荡器包 含 V , I 转换 电路与 电流控制振 荡器两 部分 , V , I 转换 电 路将 控制 电压转换 为控制 电流 , 以控制延 时单元 载波提取 、 时钟恢复 时, 则 环路的主要 的噪声源是 频率 。 这里 提供一 个例子 : C C O的设计 采用 了 四个 环形连 接的差 分延迟 单 输入 端的信道 高斯 白噪声 ; 环路用 于信号发生 器 ( 时钟产生 / 倍频 ) 时, 输

寸 的不断减小 ,使得 C M O S锁相环 的总体 性能在成熟 的基础 上继续得 以 提 高 。采用 C M O S 工艺是未 来的低功耗低 成本大规模 数模混合 集成 芯片 的发展趋 势 。电荷泵结构 的锁相环( C P P L L ) 可以说是混合 锁相环的一种 , 由于具有几乎 等于零 的相位 误差 、宽 的锁 定范 围和较 快的锁定 时间等特

天津 樊丽春 李群 贾文龙

引 ■

入 信号通 常是低噪声 的标 准信号源 ,主要 的噪声源是压 控振荡器 的内部

噪声 。

锁相 技术从 3 O 年代开始 发展 , 至今已有 7 O 多年 的历史 。目前 P L L中

的主流还是用 C MO S 工艺实 现的 。虽然 C M O S 工艺本 身的 晶体 管的截止 频率 不高 , 但 是由于研究 的深入 以及新 结构 的提 出 , 深亚微米 工艺特征 尺

器( P F D ) 、 电荷泵 ( C P ) 、 压控 振荡 器( v c o) 、 分频 器 ( D i v ) 、 环 路滤 波器 以 及 电荷泵控制电路组成 。这种结构 的锁相环 可以检测输入输 出的跳变 , 检 测相 位差或频率 差 , 并相应 地启动 电荷 泵。当环路 开始工作 时 , 输入信号

图一 电荷 泵锁相环结构时钟发 生器 系统模型框 图

其环路增益 为 :

…

薯

l 十 分

, r ,

器丽 ‘

这是一 个三 阶系统 , 我们称 之为三阶 电荷 泵锁相环 , 它有一个 零点跟 三个极 点 。在不 同的应用场合 ,环路各种 噪声与干扰 的强度有很 大 的不

图二 克服开关延时影 响的电荷泵 电路

与相位 噪声一样 , 输 出抖动依赖 于 V C O的抖动 、 锁相环输入信号 的抖 动 以及环路 的环路带宽 。对于数据和时钟恢复 的应用 , 输 入信 号的抖动往

往 是主要 的 , 因此 , 对 于这样 的场 合就需要 锁相 环的环路 带宽尽 可能低 ; 而当锁相环应用于 时钟综合 时 ,锁相环的输 出抖动主要取决于 V C O的抖 动, 此时 , 高的环路带宽有 助于减小总 的锁相环的输 出抖 动。实际上 抖动 和相 位噪声 只是 对同一 问题 的两种描述方 法 ,抖动是从 时域 的角度对 输