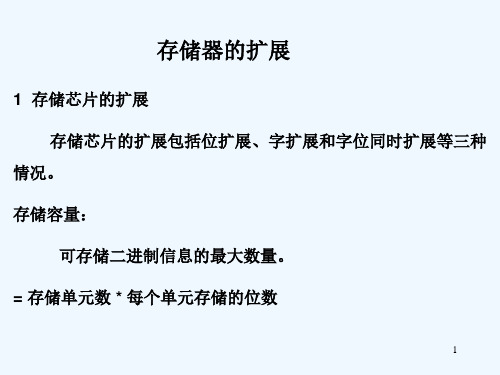

存储器的扩展

计算机存储器的容量与扩展方式

计算机存储器的容量与扩展方式计算机存储器是计算机硬件中的一个重要组成部分,用于保存和处理数据。

随着计算机应用的不断发展,存储器的容量也在不断扩展,以满足对大量数据的存储和处理需求。

本文将详细介绍计算机存储器的容量与扩展方式,包括存储器的基本概念、计算机存储器的分类以及存储器扩展的不同方式。

一、存储器的基本概念1. 存储器的定义:存储器是计算机中用于保存数据的设备,它具有读写功能,可以实现对数据的存储和读取操作。

2. 存储单元:存储器是由许多存储单元组成的,每个存储单元可以存储一个字节(8位)的数据。

3. 存储器的访问速度:存储器的访问速度快,是因为它与计算机的主控制器之间通过总线相连,数据传输的速度较快。

二、计算机存储器的分类1. 内部存储器:也称为主存储器或随机访问存储器(RAM),它是计算机中最常用的存储器。

内存的容量直接决定了计算机可以同时处理的数据量大小。

2. 外部存储器:也称为辅助存储器或外部存储器(ROM),它一般用于长期存储数据,不易丢失。

常见的外部存储器包括硬盘、磁带等。

三、计算机存储器的扩展方式1. 增加存储芯片:通过增加存储芯片的数量,可以扩展计算机的存储容量。

这种方式适合于内部存储器的扩展,可以通过在计算机主板上增加内存插槽来实现。

但是,增加存储芯片的方式不适用于外部存储器的扩展。

2. 使用存储扩展卡:存储扩展卡是一种插入计算机主板上扩展槽的卡片,可以增加计算机的存储容量。

这种方式适合于用于扩展计算机的内部存储器,例如添加额外的硬盘。

3. 利用网络存储:通过网络连接,将计算机与其他设备连接起来,可以利用其他设备的存储空间。

这种方式适合于扩展计算机的外部存储空间,例如使用网络存储设备(NAS)。

4. 使用云存储:云存储是一种将数据存储在互联网上的方式,可以通过互联网将数据上传到云存储服务提供商的服务器上,实现数据的存储和访问。

这种方式适合于扩展计算机的外部存储空间,可以随时随地访问数据。

存储器扩展仿真实验报告

一、实验目的1. 理解存储器扩展的基本原理和方法。

2. 掌握位扩展和字扩展的技巧。

3. 利用仿真软件实现存储器扩展,并验证其功能。

二、实验环境1. 仿真软件:Logisim2. 硬件设备:电脑三、实验原理1. 存储器扩展的基本原理存储器扩展是指将多个存储器芯片组合在一起,以实现更大的存储容量或更高的数据位宽。

存储器扩展主要有两种方式:位扩展和字扩展。

(1)位扩展:当存储芯片的数据位小于CPU对数据位的要求时,可以通过位扩展方式解决。

位扩展时,将所有存储芯片的地址线、读写控制线并联后与CPU的地址线和读写控制线连接,各存储芯片的数据总线汇聚成更高位宽的数据总线与CPU的数据总线相连。

(2)字扩展:当存储芯片的存储容量不能满足CPU对存储容量的要求时,可以通过字扩展方式来扩展存储器。

字扩展时,将所有存储芯片的数据总线、读写控制线各自并联后与CPU数据总线、读写控制线相连,各存储芯片的片选信号由CPU高位多余的地址线译码产生。

2. 存储器扩展的方法(1)位扩展:选择合适的存储芯片,将多个存储芯片的数据总线并联,连接到CPU的数据总线上。

(2)字扩展:选择合适的存储芯片,将多个存储芯片的数据总线、读写控制线分别并联,连接到CPU的数据总线和读写控制线上。

同时,使用译码器产生片选信号,连接到各个存储芯片的片选端。

四、实验步骤1. 创建一个新的Logisim项目。

2. 在项目中添加以下模块:(1)存储芯片模块:选择合适的存储芯片,如RAM或ROM。

(2)译码器模块:根据存储芯片的数量和地址线的位数,选择合适的译码器。

(3)数据总线模块:根据位扩展或字扩展的要求,设置数据总线的位数。

(4)地址线模块:根据存储芯片的数量和地址线的位数,设置地址线的位数。

3. 连接各个模块:(1)将存储芯片的数据总线连接到数据总线模块。

(2)将存储芯片的地址线连接到地址线模块。

(3)将译码器的输出连接到各个存储芯片的片选端。

(4)将存储芯片的读写控制线连接到CPU的读写控制线上。

存储器扩展实验

实验一存储器扩展实验

1 实验目的

1)、熟悉存储器扩展方法。

2)、掌握存储器的读/写

2 实验预习要求

1)、复习教材中存储器扩展的有关内容,熟悉存储器扩展时地址总线、控制总线及数据总线的连接方法,

了解静态RAM的工作原理。

2)、预先编写好实验程序。

3 实验内容

1)、连接电路

2)、编写程序,将字母‘A’~‘Z’循环存储在扩展的SRAM 62256存储器芯片D8000H开始的单元中,然

后再将其从62256中读出并在屏幕上显示。

4 实验提示

1)、62256芯片的容量为32K⨯8位,芯片上的地址引脚A0~A14(共15根)连接至系统的地址总线A1~A15,用来对片内32K个存储单元进行寻址。

片选信号CS接至实验台的MY0。

芯片上的8个数据引脚D0~D7直接与系统的数据引脚相连。

控制信号RD、WR分别连接到实验台的MRD#和MWR#。

写操作时,芯片上的控制信号CS=0,WR=0,RD=1;读操作时,CS=0,RD=0,WR=1。

2)、实验程序流程图如图所示。

5 实验报告要求

1)、根据流程图编写实验程序,并说明在实验过程中遇到了哪些问题,是如何处理的。

2)、总结存储器系统的基本扩展方法。

3)、写出实验小结,内容包括实验心得(收获)、不足之处或今后应注意的问题等。

第5章 单片机存储器扩展

11000000000000000~1101111111111111,即C000H~DFFFH;

11100000000000000~1111111111111111,即E000H~FFFFH。

•采用地址译码器的多片程序存储器的扩展(译码法)

例3 要求用2764芯片扩展8031的片外程序存储器,分配的地

21×210 = 211

地址空间: A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 最低地址: 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0000H 07FFH

最高地址: 1

MCS-51单片机寻址范围:64KB

26×210 = 216即16位地址线

地址空间: A15A14A13A12A11A10A9A8A7··A0 单片机 ·· ·· × × × × × A10A9A8A7··A0 6116 ·· ·· 2KB

25 = 32

上式中:“×”表示0或1。

即单片机地址空间中包含有32个2KB。某片6116占据的是哪 2KB不能确定——地址浮动。 只有限定A15··A11的取值才能确定6116在系统中的地址 ·· ·· 范围。如,P2.5 = 1 ,选中6116的/CS线。设P2.7 P2.5 P2.4 P2.3 假定全为1

例2 使用两片2764扩展16 KB的程序存储器,采用线选法选

中芯片。扩展连接图如图所示。以P2.7作为片选,当P2.7=0时,

选中2764(1);当P2.7=1时,选中2764(2)。因两根线(A13、A14)

未用,故两个芯片各有22=4个重叠的地址空间。它们分别为

用两片2764 EPROM的扩展连接图

则: 6116地址范围是B800H ~ BFFFH。

存储器扩展-

A9~ A0

WE CS R A M2 2114

I /O1~ I /O4

A9~ A0

WE CS R A M3 2114

I /O1~ I /O4

D7~ D4 WR

字位同时扩展连接图

I /O1~ I /O4 WE CS

R A M4 2114 A9~ A0

A9~ A0 WE CS

R A M4 2114 I /O1~ I /O4

RAM1 2114 I/O1~I/O4

I/O1~I/O4 WE CS

RAM2 2114 A9~A0

A9~A0 WE CS

RAM2 2114 I/O1~I/O4

I/O1~I/O4 WE CS

RAM3 2114 A9~A0

A9~A0 WE CS

RAM3 2114 I/O1~I/O4

I/O1~I/O4 WE CS

A11

A10

译码器

1

2

3

4

A9~A0 CPU

1 CS

1K×4

WE I/O1~4

2 CS

1K×4

WE I/O1~4

D7~D4

D3~D0

1 CS

1K×4

WE I/O1~4

2 CS

1K×4

WE I/O1~4

D7~D4

D3~D0

WE D7~D0

D7~D0

D7~D0

D7~D0

字位同时扩展构成4K×8存储器电路连接示意图

3

2. 字扩展(地址范围)

字扩展用于存储芯片的位数满足要求而字数不够的情况,是

对存储单元数量的扩3 展。

A15

2-4 译

2

码1

单片机存储器扩展

单片机存储器扩展在单片机的应用中,常常会遇到内部存储器容量不足的情况。

这时候,就需要对单片机的存储器进行扩展,以满足系统对存储容量的需求。

单片机的存储器可以分为程序存储器和数据存储器。

程序存储器用于存储单片机运行的程序代码,而数据存储器则用于存储程序运行过程中的数据。

当单片机内部的存储器无法满足应用需求时,就需要通过外部扩展来增加存储容量。

在进行存储器扩展之前,我们需要了解单片机的存储器寻址方式。

不同的单片机可能有不同的寻址方式,但通常都包括直接寻址、间接寻址和变址寻址等。

了解寻址方式对于正确进行存储器扩展至关重要。

对于程序存储器的扩展,常用的方法是使用外部只读存储器(ROM),如 EPROM(可擦除可编程只读存储器)、EEPROM(电可擦除可编程只读存储器)等。

扩展时,需要将外部 ROM 与单片机的地址总线、数据总线和控制总线正确连接。

地址总线用于指定存储器的地址,数据总线用于传输数据,控制总线则用于控制存储器的读写操作。

以常见的 8051 单片机为例,它的地址总线为 16 位,可以寻址64KB 的存储空间。

如果要扩展 32KB 的程序存储器,我们可以选用一片容量为 32KB 的 EPROM 芯片,如 27256。

将 EPROM 的地址线 A0A14 与单片机的地址总线 A0 A14 相连,数据线 D0 D7 与单片机的数据总线 D0 D7 相连。

控制总线中的片选信号(CS)通常通过地址译码器来产生,以确保在特定的地址范围内选中该 EPROM 芯片。

在数据存储器的扩展方面,常用的是外部随机存取存储器(RAM),如静态 RAM(SRAM)和动态 RAM(DRAM)。

SRAM 速度较快,但价格相对较高;DRAM 价格较低,但需要不断刷新。

同样以 8051 单片机为例,如果要扩展 8KB 的数据存储器,可以选用一片 6264 SRAM 芯片。

连接方式与程序存储器扩展类似,地址线和数据线分别与单片机的对应总线相连。

存储器的扩展原理

存储器的扩展原理

存储器的扩展原理主要是通过增加存储芯片的数量来扩大存储容量。

由于单片存储芯片的容量有限,难以满足实际需求,因此需要将多片存储芯片连接在一起,以组成容量更大的存储器。

扩展存储器的方式主要有位扩展和字扩展两种。

位扩展是在位数方向上扩展,而字扩展是在字数方向上扩展。

在位扩展中,需要将多个存储芯片的位数相加,以增加数据线的数量。

例如,如果要将一个1K x 4位的存储芯片扩展

为1K x 8位的存储芯片,可以采用两片1K x 4位的存储芯片,并将它们连接在一起。

这样,两个芯片共用相同的片选信号,同时被选中,每个芯片进行读或写4位数据,两个芯片合在一起就是8位数据。

在字扩展中,需要将多个存储芯片的字数相加,以增加地址线的数量。

例如,如果要将一个1K x 8位的存储芯片扩展为2K x 8位的存储芯片,可以采用两片1K x 8位的存储芯片,并将它们连接在一起。

这样,两个芯片共用相

同的片选信号和数据线,同时被选中,每个芯片存储一个字的数据,两个芯片合在一起就是两个字的数据。

总之,通过位扩展和字扩展的方式,可以将多个存储芯片连接在一起,以组成容量更大的存储器,以满足实际需求。

存储器扩展实验报告

存储器扩展实验报告存储器扩展实验报告引言:存储器是计算机系统中至关重要的组成部分,对于数据的存储和读取起着至关重要的作用。

在计算机科学领域中,存储器扩展是一项重要的技术,可以提高计算机系统的性能和容量。

本实验旨在通过对存储器扩展的探索和实践,深入了解存储器的工作原理和扩展方法。

一、存储器的基本原理存储器是计算机中用于存储和检索数据的硬件设备。

它可以分为主存储器和辅助存储器两种类型。

主存储器是计算机系统中最重要的存储器,它用于存储正在运行的程序和数据。

辅助存储器则用于存储大量的数据和程序,常见的辅助存储器包括硬盘、光盘和闪存等。

二、存储器的扩展方法存储器的扩展方法有很多种,本实验主要探索两种常见的扩展方法:内存条扩展和虚拟内存扩展。

1. 内存条扩展内存条扩展是通过增加计算机内部的内存条数量来扩展存储器容量的方法。

在实验中,我们使用了两根相同规格的内存条,将其插入计算机主板上的内存插槽中,从而增加了系统的内存容量。

通过这种扩展方法,我们可以提高计算机的运行速度和处理能力。

2. 虚拟内存扩展虚拟内存是一种将计算机内存和硬盘空间结合起来使用的技术。

在实验中,我们通过调整计算机系统的虚拟内存设置,将部分数据和程序存储在硬盘上,从而扩展了存储器的容量。

虚拟内存的扩展方法可以有效地提高计算机的性能和运行效率。

三、实验过程与结果在实验中,我们首先进行了内存条扩展的实践。

通过将两根内存条插入计算机主板上的内存插槽中,我们成功地扩展了计算机的内存容量。

在进行实际操作时,我们注意到计算机的运行速度明显提高,程序的加载和执行时间也大大缩短。

接着,我们进行了虚拟内存扩展的实验。

通过调整计算机系统的虚拟内存设置,我们将部分数据和程序存储在硬盘上。

在实际操作中,我们发现虚拟内存的扩展使得计算机可以同时运行更多的程序,且不会出现内存不足的情况。

这大大提高了计算机的运行效率和多任务处理能力。

四、实验总结与心得通过本次实验,我们深入了解了存储器的工作原理和扩展方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表6.6 图6.16中各芯片地址空间分配表

地址 片号

1

A15A14

00 00

A13A12A11…A1A0

000…00 111…11

说明

最低地址(0000H) 最高地址(3FFFH)

2

01 01

000…00 111…11

最低地址(4000H) 最高地址(7FFFH)

3

10 10

000…00 111…11

图中将8片2114芯片分成了4组(RAM1、RAM2、RAM3和 RAM4),每组2片。组内用位扩展法构成1K8的存储模块,4个 这样的存储模块用字扩展法连接便构成了4K8的存储器。用 A9A0 10根地址线对每组芯片进行片内寻址,同组芯片应被同 时选中,故同组芯片的片选端应并联在一起。本例用2–4译码器 对两根高位地址线A10A11译码,产生4根片选信号线,分别与各 组芯片的片选端相连。

2.字扩展

字扩展用于存储芯片的位数满足要求而字数不够的情况,是

对存储单元数量的扩展。图6.18给出了用4个16 K8芯片经字扩展

构成一个64K8存储器系统的连接方法。

3

A15

2-4 2 译

码1

A14

器0

A0

CE

CE

CE

CE

16×8

16×8

16×8

16×8

… … … … …

(1)

(2)

(3)

(4)

A13

A9~ A0

WE CS R A M1 2114

I/ O1~ I/ O4

A9~ A0

WE CS R A M2 2114

I/ O1~ I/ O4

A9~ A0

WE CS R A M3 2114

I/ O1~ I/ O4

A9~ A0

WE CS R A M4 2114

I/ O1~ I/ O4

D7~ D4 WR

图6.19 字位同时扩展连接图

2.存储器与数据总线的连接

对于不同型号的CPU,数据总线的数目不一定相同,连接时 要特别注意。

8086 CPU的数据总线有16根,其中高8位数据线D15D8接存 储器的高位库(奇地址库),低8位数据线D7D0接存储器的低位库 (偶地址库),根据BHE(选择奇地址库)和A0(选择偶地址库)的不同 状态组合决定对存储器做字操作还是字节操作。图6.20给出了由 两片6116(2K8)构成的2K字(4K字节)的存储器与8086 CPU的连 接情况。

6.4 存储器的扩展

6.4.1 存储芯片的扩展 存储芯片的扩展包括位扩展、字扩展和字位同时扩展等三种

情况。

1.位扩展 位扩展是指存储芯片的字()数满足要求而位数不够,需对每 个存储单元的位数进行扩展。图6.17给出了使用8片8 K1的RAM 芯片通过位扩展构成8K8的存储器系统的连线图。

由于存储器的字数与存储器芯片的字数一致,8 K=213,故只 需13根地址线(A12A0)对各芯片内的存储单元寻址,每一芯片只 有一条数据线,所以需要8片这样的芯片,将它们的数据线分别 接到数据总线(D7D0)的相应位。在此连接方法中,每一条地址 线有8个负载,每一条数据线有一个负载。位扩展法中,所有芯 片都应同时被选中,各芯片CS端可直接接地,也可并联在一起, 根据地址范围的要求,与高位地址线译码产生的片选信号相连。 对于此例,若地址线A0A12上的信号为全0,即选中了存储器0号 单元,则该单元的8位信息是由各芯片0号单元的1位信息共同构 成的。

WE

WE8 有16 K8位芯片组成64 K8位的存储器

图中4个芯片的数据端与数据总线D7D0相连;地址总线低 位地址A13A0与各芯片的14位地址线连接,用于进行片内寻址; 为了区分4个芯片的地址范围,还需要两根高位地址线A14、A15 经2–4译码器译出4根片选信号线,分别和4个芯片的片选端相连。 各芯片的地址范围见表6.6。

3.字位同时扩展

在实际应用中,往往会遇到字数和位数都需要扩展的情况。

若使用lk位存储器芯片构成一个容量为MN位(M>l,N>k) 的存储器,那么这个存储器共需要(M/l)(N/k)个存储器芯片。 连接时可将这些芯片分成(M/l)个组,每组有(N/k)个芯片,组内 采用位扩展法,组间采用字扩展法。

图6.19给出了用2114(1K4)RAM芯片构成4K8存储器的连 接方法。

6.4.2 存储器与CPU的连接

CPU对存储器进行访问时,首先要在地址总线上发地址信号, 选择要访问的存储单元,还要向存储器发出读/写控制信号,最后 在数据总线上进行信息交换。因此,存储器与CPU的连接实际上 就是存储器与三总线中相关信号线的连接。

1.存储器与控制总线的连接

在控制总线中,与存储器相连的信号线为数不多,如 8086/8088最小方式下的M/IO(8088为M/IO)、RD和WR,最大方式 下的MRDC、MWTC、IORC和IOWC等,连接也非常简单,有时 这些控制线(如M/IO)也与地址线一同参与地址译码,生成片选信 号。

最低地址(8000H) 最高地址(BFFFH)

4

11 11

000…00 111…11

最低地址(C000H) 最高地址(FFFFH)

可以看出,字扩展的连接方式是将各芯片的地址线、数据 线、读/写控制线并联,而由片选信号来区分各片地址。也就是 将低位地址线直接与各芯片地址线相连,以选择片内的某个单 元;用高位地址线经译码器产生若干不同片选信号,连接到各 芯片的片选端,以确定各芯片在整个存储空间中所属的地址范 围。

可以看出,位扩展的连接方式是将各芯片的地址线、片选 CS、读/写控制线相应并联,而数据线要分别引出。

地址总线 A0 A12

控制总线 CS WR

D7

数据总线

… …

…

8

7

6

1

2

3

4

5

I/O

I/O

I/O

I/O

I/O

8 K×1

I/O I/O

CS WR I/O

D0

图6.17 用8K1位芯片组成8K8位的存储器

A1 1

2- 4

译码器

A1 0

D3~ D0

A9~ A0

I/ O1~ I/ O4

WE CS R A M1 2114 A9~ A0

I/ O1~ I/ O4

WE CS R A M2 2114 A9~ A0

I/ O1~ I/ O4

WE CS R A M3 2114 A9~ A0

I/ O1~ I/ O4

WE CS R A M4 2114 A9~ A0

8位机和8088 CPU的数据总线有8根,存储器为单一存储体 组织,没有高低位库之分,故数据线连接较简单。