基于Verilog的DDS设计与显示

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器的设计和实现引言在电子领域中,正弦信号是一种重要的基础信号,被广泛应用于通信、音频、视频等各个领域。

而DDS(Direct Digital Synthesis)直接数字合成技术则是一种通过数字方式生成高精度、高稳定性的正弦波信号的方法。

本文将详细介绍基于FPGA的DDS正弦信号发生器的设计和实现。

设计目标本次设计旨在实现一个可配置频率范围广泛且精度高的DDS正弦信号发生器。

具体设计目标如下: 1. 实现频率范围可调节,覆盖从几Hz到数十MHz; 2. 提供高精度的频率控制,满足特定应用场景对频率稳定性和相位精度的要求; 3. 支持模数转换器(DAC)输出,并能够通过外部接口控制输出幅值; 4. 使用FPGA作为主要硬件平台,以满足高速计算和灵活配置需求。

系统架构基于FPGA的DDS正弦信号发生器主要由以下几个部分组成: 1. 数字控制模块(Digital Control Module):负责接收外部输入的频率、相位和幅值等参数,并将其转换为对DDS核心模块的控制信号; 2. DDS核心模块(DDS Core Module):根据接收到的控制信号,通过数学运算生成正弦波形的离散采样值; 3. 数字模拟转换模块(Digital-to-Analog Converter, DAC):将DDS核心模块输出的数字采样值转换为模拟电压信号; 4. 输出放大器(Amplifier):用于放大DAC输出的电压信号,并通过外部接口提供可调节幅值的正弦波输出。

DDS核心模块设计DDS核心模块是整个系统中最关键的部分,它负责根据输入参数生成正弦波的离散采样值。

下面是DDS核心模块设计中需要考虑的几个关键要素:相位累加器相位累加器是DDS核心模块中最基础且重要的组件之一。

它根据输入的频率和时钟信号,在每个时钟周期内累加相位增量,从而实现相位连续变化。

相位累加器可以使用一个定点数或浮点数寄存器来表示,并通过固定步长进行相位递增。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

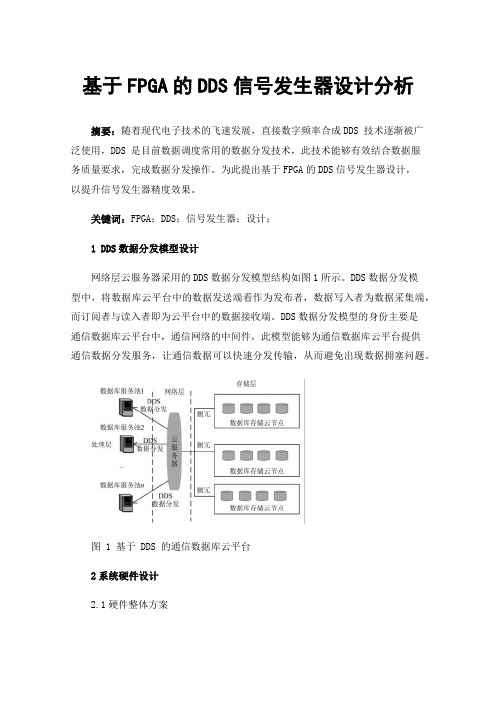

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于fpga的dds正弦信号发生器的设计和实现

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用数字信号处理技术实现。

下面是一个基本的设计和实现步骤:

1. 确定系统需求:首先,确定所需的输出信号频率范围、分辨率和采样率等系统参数。

这些参数可以根据实际应用来确定。

2. 设计正弦表:根据系统需求,设计一个包含所需频率范围内所有可能的正弦波的正弦表。

可以使用固定小数点表示法来表示正弦表中的采样值。

3. 设计相位累加器:使用一个32位计数器作为相位累加器,其计数速度由所需的输出信号频率和FPGA时钟频率决定。

每个时钟周期,计数器值自动增加到下一个相位值。

4. 选择相位值:使用相位累加器的值在正弦表中查找对应的相位值,并将其作为输出信号的采样值。

5. 数字输出:将采样值经过DAC(数字模拟转换器)转换为模拟信号,并将其输出。

6. 配置FPGA:将设计好的数字电路加载到FPGA芯片中,并配置FPGA内部的寄存器、时钟和IO管脚等。

7. 测试和调试:对设计好的系统进行测试和调试,确保输出信号的频率、精确度和稳定性符合要求。

这是一个基本的设计和实现步骤,具体的实现方法和细节可能因FPGA型号、工具和应用需求而异。

在实际应用中,还可以加入滤波器、幅度控制、相位调制等功能以满足更多需求。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

(完整word版)基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计摘要:利用FPGA芯片及D/A转换器,采用直接数字频率合成技术,设计并实现了一个频率、幅值可调的信号发生器,同时阐述了该信号发生器的工作原理、电路结构及设计思路。

经过电路调试,输出波形达到技术要求,证明了该信号发生器的有效性和可靠性。

0 引言信号发生器作为一种基本电子设备广泛的应用于教学、科研中,因此从理论到工程对信号的发生进行深入研究,有着积极的意义.随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA 的DDS信号发生器设计,实现了满足预定指标的多波形输出。

可产生不同频率、幅度的正弦波、三角波、矩形波信号,仿真和实测结果均证实了其灵活性和可靠性。

1 函数信号发生器的原理和设计1.1 函数信号发生器的结构图1为DDS信号发生器系统结构框图.系统以FPGA芯片为信息处理核心,主要完成数字频率合成、D/A转换、选择滤波、功率放大、LCD显示等功能。

频率控制字M送入32位的累加器进行累加运算,截取32位累加器的第24到第30位作为ROM的地址,ROM在累加器的控制下,输出8位的数字波形数据,经过DAC0832转换为模拟量,因为DAC0832输出的是电流的形式,所以通过电压转电流电路转换为电压形式的模拟波形,但其中还含有大量的高频成分,为了输出频率纯净的信号波形,再通过一个二阶的有源低通滤波器。

最后为了调节输出信号的峰峰值,再引入一个幅度调节电路。

根据直接数字频率合成理论将系统的频率分辨率及输出频率写为:其中fclk和N为系统时钟和位宽,M为频率控制字,利用信号相位与时间成线性关系的特性,直接对所需信号进行抽样、量化和映射,输出频率可调的信号波形。

基于FPGA的DDS设计报告

DDS设计报告摘要:DDS信号发生器能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA的DDS信号发生器设计,实现了满足预定指标的多波形输出。

同时采用STM32来进行控制频率,幅度的输入以及对波形类型,频率,幅度值进行显示,从而很好地实现了人机交界。

关键字:DDS信号发生器FPGA STM32 频率幅度值目录1.系统设计 (3)1.1设计要求 (3)1.1.1任务 (3)1.1.2要求 (3)1.1.3说明 (3)1.2总体设计方案……………………………………………………………………………………………………..1.2.1设计思路…………………………………………………………………………………………………1.2.2方案论证与比较……………………………………………………………………………………….1.2.3系统组成…………………………………………………………………………………………………..2.单元硬件电路设计………………………………………………………………………………………………………2.1电路的设计…………………………………………………………………………………………………….2.2……………………………………………………………………………………………………..2.3………………………………………………………………………………………………………2.4……………………………………………………………………………………………………….3.软件设计……………………………………………………………………………………………………………………..3.1软件设计与硬件设计的关系…………………………………………………………………………………3.2部分程序设计…………………………………………………………………………………………………..3.3部分程序设计………………………………………………………………………………………………….4.系统测试…………………………………………………………………………………………………………………………4.1测试使用的仪器…………………………………………………………………………………………………….4.2指标测试和测试结果…………………………………………………………………………………………….4.3结果分析………………………………………………………………………………………………………………..5.结论………………………………………………………………………………………………………………………………. 参考文献………………………………………………………………………………………………………………………………附录1 主要元器件清单……………………………………………………………………………………………………附录2 电路原理图及印刷板图……………………………………………………………………………………….附录3 程序清单………………………………………………………………………………………………………………..1.系统设计1.1设计要求1.1.1设计任务设计并制作一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由用户编辑的特定波形形状。

基于Verilog+HDL的DDS设计与仿真

基于Verilog HDL的DDS设计与仿真直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。

它采用全数字技术,并从相位角度出发进行频率合成。

随着微电子技术和数字集成电路的飞速发展,以及电子工程领域的实际需要,DDS 日益显露出优于传统频率合成技术的一些性能,高分辨率、极短的频率切换时间、相位噪声低、便于集成等,逐步成为现代频率合成技术中的佼佼者。

目前,DDS的设计大多是应用HDL(Hardware Description Language)对其进行逻辑描述。

整个设计可以很容易地实现参数改变和设计移植,给设计者带来很大的方便。

Verilo g HDL就是其中一种标准化的硬件描述语言,它不仅可以进行功能描述,还可以对仿真测试矢量进行设计。

Altera公司开发的QuartusⅡ设计软件,提供了Verilog HDL的设计界面以及编译平台,并且该公司还集成了可供程序下载的FPGA器件CYCLONEⅡ系列芯片,这样大大缩短了DDS的设计周期。

1 DDS的设计原理DDS的原理图如图1所示。

DDS实现频率合成主要是通过查表的方式进行的。

正弦查询表是一个只读存储器(ROM),以相位为地址,存有1个或多个按0°~360°相位划分幅值的正弦波幅度信息。

相位累加器对频率控制字进行累加运算,若需要还可以加入相位控制字,得到的结果作为正弦波查询表的地址。

正弦查询表的输出为数字化正弦幅度值,通过D/A转换器转化为近似正弦波的阶梯波,再通过低通滤波器滤除高频成分和噪声最终得到一个纯正度很高的正弦波。

1.1 建模如图2所示正弦波y=sin(2πx),若以f量化的量化频率对其幅度值进行量化,一个周期可以得到M=f量化个幅度值。

将这些幅度值按顺序存入到ROM。

相位累加器在参考时钟的驱动下,每来1个脉冲,输出就会增加1个步长相位增量X,输出数据作为地址送入ROM 中,读出对应的幅度值形成相应的波形。

基于Verilog的DDS设计及仿真

系 统 设计 采用 美 国Xilinx公 司的xc4vsx35实现 频 率为 4M 的四路 波形 分 别为 :正 、余 弦 ,方波 以及三 角波波 形 ,时 钟为 lOOM 。 2.1 系统Verilog源 程 序

输 入 的控 制 字 为32bit(经 计 算为 171798690),输 出20bit四路信 号 分别 为 :正 、余 弦 ,方 波 以及三 角波 波 形 , 以及reset,cein,wein控 制 输入 的信号 。

module DDS(datain,wein,clkin,cein,reset,cosin,sin,rect,trip);

·198 · 电 子 世 界

input[3 1:0]datain;//频 率控 制字

input w ein;

input clkin;

input cein;

inpu t reset;

output【19:0]eosein; //余 弦输 出 output[19:0]sin; //iE弦输 出 out put【19:0]trip; //三角 波输 出

out put[19:0]rect; //TJ波 输 出

reg[3 1:0]ADD—A; reg[3 1:0】ADD_B; reg[19:0]cose_DR; reg[19:0]sine DR;

. elk(elk) dout(trip—D));

endm odule

2.2 ROM定 制

r

在 编 译源 程 序 前 , 必须 首 先 完 成存 放 波 形数 据 ROM 的定 制 。

利 用 MATLAB计 算 出波 形 幅 度 的浮 点 值 , 并量 化 16比特 的定 点 波

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件描述语言课程设计题目:基于Verilog的DDS设计与显示学院:自动化工程学院专业:信号与信息处理年级:2012级姓名:黄山2013年1 月19 日1.设计要求设计一个DDS 信号发生器,能够产生三角波,要求频率、相位可调。

实现VGA 显示波形和参数。

要求用DE2-70开发板完成。

设计要求:一、DDS 信号发生器设计要求:(1) 频率两档可调; (2) 峰峰值两档可调;二、VGA 波形和字符显示设计要求:(1) 用红色显示2个周期波形; (2) 在屏幕下方显示字符库。

2.设计原理及分析一)DDS 原理(以正弦信号为例)对于正弦信号发生器,它的输出可以用下式来描述:(1)其中,S OUT 是指该信号发生器的输出信号波形,f OUT 指输出信号对应的频率。

上式的表述对于时间t 是连续的,为了用数字逻辑实现该表达式,必须进行离散化处理,用基准时钟clk 进行抽样,令正弦信号的相位θ为tf out πθ2=(2)在一个clk 周期Tclk ,相位θ的变化量为clkout clk out f f T f /22ππθ==∆(3)为了对θ∆进行数字量化,把2π切割为2N 由此,每份clk 周期的相位增量θ∆用量化值(4) 且θ∆B 为整数。

sin(2)=sin()out out S A f t A πθ=22NB θθπ∆∆≈⋅2Nout CLKf B f θ∆≈⋅(5)显然,信号发生器的输出可描述为:(6)其中θK-1指前一个clk 周期的相位值,同样得出(7)由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值,为用于累加的相位增量量化值θ∆B 决定了信号的输出频率f OUT ,并呈现简单的线性关系。

直接数字合成器DDS 就是根据上述原理而设计的数控频率合成器,主要由相位累加器、相位调制器、正弦ROM 查找表、和DAC 构成。

如图1中相位累加器、相位调制器、正弦ROM 查找表是DDS 结构中的数字部分,由于具有数控频率合成的功能,可称为NOC(Numerically Controlled Oscillators)。

BK0BK1BK2BK3BKI0BKI1BKI2BKI3Q0MULTA幅值输入Q图1 DDS 信号发生器结构二)VGA 显示原理常见的计算机显示器有CRT ( Cathode Ray Tube ,阴极射线管)显示器和液晶显示器,本次设计针对CRT 显示。

CRT 中的阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生RGB 三基色,合成一个彩色像素。

用逐行扫描的方式显示图像。

扫描从屏幕左上方开始,从左到右,从上到下,进行扫描。

每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,1sin(+)k outk S A B B θθ-∆=Nk θπθB k2211∙=--并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

图2 扫描轨迹其中蓝色– 行正程,红色 – 行逆程;正程显示(实线),逆程消隐(虚线)1.VGA 显示标准VGA 标准共有5个信号:R (红色)、G (绿色)、B (蓝色)、HS (行同步)、VS (场同步)支持640*480分辨率图3 VGA 显示标准(行)表1 行扫描时序行扫描时序(单位:像素,即输出一个像素的时间)Ta Tb Tc Td Te Tf Tg 时间 9640864088800正程轨迹图场逆程扫描轨迹图4 VGA显示标准(场)表2 场扫描时序场扫描时序(单位:行,即输出一行的时间)Ta Tb Tc Td Te Tf Tg 时间225848082525VGA显示标准时钟频率:25.175MHz(输出像素的频率)行频:31469Hz场频:59.94Hz (每秒图像刷新频率, 约60Hz)2.时序处理分别将场同步信号和行同步信号做时间近似处理表3 对行同步做近似处理行扫描时序(单位:us)Ta Tb Tc Td Te Tf Tg时间 3.8 1.60.325.40.30.3前项之和5.7us26us表4 对场同步做近似处理场扫描时序(单位:行)Ta Tb Tc Td Te Tf Tg时间225848082525作近似处理2忽略480忽略482这样,便可通过计数分频得到行同步信号和场同步信号。

下面以开发板的50Mhz 时钟信号为例,得到32Khz的行同步信号和64hz的长同步信号图5 时序处理图三)波形显示原理要显示波形,需要将波形数据存入存储器(简称wave_RAM )。

wave_RAM 中可以写入读出波形数据。

下面将以幅值为256的正弦波为例,阐明波形显示原理。

图6 波形显示结构图每个时钟沿到来,从存储器中读出一个数,通过判断x_cnt 与addr 的关系以及y_cnt 与data 的关系是否满足条件,控制屏幕上以x_cnt 和y_cnt 为坐标的像素点的颜色值。

其中,x_cnt 与addr 的关系以及y_cnt 与data 的关系如下图7所示。

图7 波形显示像素位置与存储器地址之间关系x_cnt 与存储器地址对应;若高度等于数据值,则该处颜色为红色。

关键算法如下:若在(m,n)处开始显示波形26分频2分频482分频50Mhz 25Mhz31Khz 64hz clk vga_clk HS VS 系统时钟像素时钟行同步信号场同步信号当x_cnt=m时,addr=0若y_cnt=n-data,则rgb=010;当x_cnt=m+1时,addr=1若y_cnt=n-data,则rgb=010;… …当x_cnt=m+i时,addr=i若y_cnt=n-data,则rgb=010;四)字符显示原理要显示字母、数字、符号、汉字等,需要自建字库(以后简称Char_ROM)。

Char_ROM中存放字模数据。

字模尺寸自行设定,例如英文字母、数字等可设置为16行*8列像素,汉字可设置为16行*16列像素。

图8 字符库端口图1.字模库设计以16行*8列的字模1的设计及存储为例。

图9 字模库设计举例字库容量:地址线与所有字符所占列数(决定于字符数量)有关,数据线与一个字符所占行数有关。

该例中数据线位数为16bit,地址为2bit。

2.字符显示思路:1)确定屏幕显示起始位置,屏幕显示起始位置由行列计数值决定。

2)求Char_ROM地址Char_ROM起始地址由所要显示的字符决定(可将地址用宏定义的方法与字符关联)。

3)读取该地址对应的数据4)确定数据位和像素位置的关系数据位和像素位置的关系由行计数值、起始行数、字符所占行数决定。

5)显示颜色,RGB 赋值若数据为1,则对应位置上的RGB 赋值为字符色,否则RGB 值赋值为背景色。

至此,DDS 及VGA 显示的原理介绍结束,下面开始进行系统设计及程序编写仿真。

三、系统设计实现由于实验时间有限,在实际设计时并未对所生成波形做移相与改变幅值的处理,整体设计思路如下图10所示。

Sin_ROM计数分频计数分频Char_ROM条件判断赋值条件判断+DQ>>>频率字vga_clkNNMaddraddrcharRGBHSVS xccclk字符输出DDS 发生器,波形输出图10 系统设计思路一) 参数设计本次实验中所生成的正弦波共采样256个点,存储器采用8位地址线,数据为16bit 。

设N 为18位,M 为地址线位数为8位,频率字θ∆B =(000000010000000000)2,则当输入时钟为vga_clk=25Mhz 时,由DDS 原理部分公式可推知当输出DDS 输出频率f OUT =100Khz 。

由于显示屏幕大小为640*480,需要显示两个周期的波形共256*2=512个点,设置屏幕显示横向范围为50到561,纵向范围为100到300;字符显示范围为横向50到305,纵向310到325。

二) 各模块实现程序及仿真结果1.DDS模块程序如下:module DDS1(CLK ,CTR,Q);input CLK;input CTR;//input [17:0] BK0; //频率设置字//input [3:0] A; //幅值设置字//input [2:0] BKI0; //初相位设置字output [7:0] Q; //DDS数字量输出wire [17:0] BK0;wire [17:0] BK1;wire [17:0] BK2;wire [17:0] BK3;wire [7:0] addr;wire [7:0] Q0;wire [7:0] Q1;reg [7:0] Q2;assign BK0=17'b000000010000000000;assign BKI2 = BK2[17:10];//取N位的高M位DFF32 DDF1 (CLK,BK0,BK1);ADD ADD1(CLK,BK1,BK2,BK3);DFF32 DDF2 (CLK,BK3,BK2); //相位累加器ROM10 ROM1 (BKI2,CLK,Q0);//正弦ROM查找表ROM10tri ROM2 (BKI2,CLK,Q1);always @(posedge CLK)if (CTR) Q2 <= Q0;else Q2 <= Q1;assign Q = Q2;endmodule仿真结果如下图11所示图11 DDS模块仿真结果2.vga显示模块module ddsvga (vga_clk,clk,hs,vs,blank_n,red, green, blue, sync_n);input clk;output hs,vs;output blank_n;output[9:0] red;output[9:0] green;output[9:0] blue;output sync_n;output vga_clk;wire r,g,b;wire [3:1] grb;wire vs,hs,sync_n_r;wire fclk,cclk;wire clk_div;wire [7:0] addr;wire [7:0] data;wire [4:0] addrchar;wire [15:0] datachar;integer i;reg [7:0] addr1;reg [4:0] addr1char;reg hs1,vs1;wire [8:0] y_cnt;reg [9:0] xcc;reg [5:0] fs;reg [4:0] cc;//hang tong bureg [8:0] ll;//chang tong bureg [3:1] grbp;div_2 div_2(clk,clk_div);ROMsin ROM(addr,clk,data);//testchar testchar(addrchar,clk,datachar);assign vga_clk=clk_div;assign grb[2]=(grbp[2])&hs1&vs1;assign grb[3]=(grbp[3])&hs1&vs1; assign grb[1]=(grbp[1])&hs1&vs1;always @(posedge clk) beginif (fs==53) fs<=0;else fs<=(fs+1'b1);endassign fclk=fs[5];always @(posedge fclk) beginif (cc==29) cc<=5'b00000;else cc<=cc+1'b1;endassign cclk=cc[4];always @(posedge cclk) beginif (ll==481) ll<=9'b0;else ll<=ll+1'b1;endassign y_cnt=ll;//生成行同步,场同步信号always @(cc or ll) beginif (cc>23) hs1<=1'b0;else hs1<=1'b1;if (ll>479) vs1<=1'b0;else vs1<=1'b1;endalways @( posedge vga_clk)if(blank_n)beginif(xcc==639) xcc<=0;else xcc<=xcc+1'b1;endelse xcc<=0;always@(xcc,y_cnt,data)beginif (xcc>=10'd200 && xcc<=10'd455) beginaddr1<=xcc-8'd200;if (y_cnt==9'd300-data) grbp<=3'b001;else grbp<=3'b000;endelsebeginaddr1<=3'b000;grbp <=3'b000;endend/****************/always @(posedge clk_div)beginif(y_cnt >= 9'd100 && y_cnt <= 9'd115)beginif (xcc == 10'd500)addr1char <= 0; //求地址else if (xcc >= 10'd501 && xcc <= 10'd516 )addr1char<=addr1char+1'b1;endendwire [3:0] dis_bit=10'd115-y_cnt;always @ (posedge clk_div) //数据位begingrbp<=3'b000;if (y_cnt>=9'd100 && y_cnt<=9'd115 && xcc>=10'd501 && xcc<=10'd516 ) beginif(datachar[dis_bit])grbp <= 3'b010; //RGB赋值else grbp <= 3'b000;endend/****************/assign addr=addr1;assign addrchar=addr1char;assign hs=hs1;assign vs=vs1;assign r=grb[2];assign g=grb[3];assign b=grb[1];assign blank_n=hs&vs;assign sync_n_r=1'b0;assign sync_n=sync_n_r;assign red={10{r&blank_n}};assign green={10{g&blank_n}};assign blue={10{b&blank_n}};endmodule最终显示结果如图12所示图12 结果显示。