三态输出门电路(TSL门)

实验二 三态门和OC门的研究

图输出高电平VOH的下限值; VOL(max) --门电路输出低电平VOL的上限值; IOH(max)--门电路带拉电流负载的能力,或称放电流能力; IOL(max)—门电路带灌电流负载的能力,或称吸电流能力; VIH(min)--为能保证电路处于导通状态的最小输入(高)电平; VIL(max) --为能保证电路处于截止状态的最大输入(低)电平。 IIH — 输入高电平时流入输入端的电流; IIL -- 输入低电平时流出输入端的电流。

图3_2_5 计算OC门外接电阻Rc的工作状态

m'(7)个输入端(a) 计算Rc最大值(b) 计算Rc最小值图3_2_5 计算OC门外接电阻Rc的 工作状态

其中 IcEO -- OC门输出三极管T5截止时的漏电流; Ec — 外接电源电压值; m -- TTL负载门个数; n — 输出短接的OC门个数; m’— 各负载门接到OC门输出端的输入端总和。 Rc值的大小会影响输出波形的边沿时间,在工作速度较高时,Rc的取值应接近

3完成第七项中的思考题1233281用三态门实现三路信号分时传送的总线结构

实验二 三态门和OC门的研究 一、实验目的

(1) 熟悉两种特殊的门电路:三态门和OC门; (2) 了解“总线”结构的工作原理。 二、实验原理

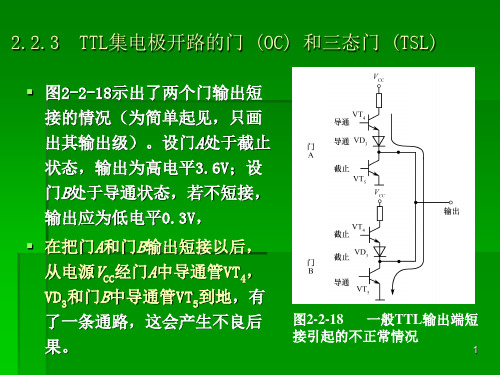

数字系统中,有时需把两个或两个以上集成逻辑门的输出端连接起来,完成一定的逻

辑功能。普通TTL门电路的输出端是不允许直接连接的。图2_1示出了两个TTL门输出短 接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。设门A处于截止状态, 若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。在把门 A和门B的输出端作如图3_2_1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导 通的 T5到地,有了一条通路,其不良后果为:图3_2_1 不正常情况:普通TTL门电路输 出端短接

第八讲 其它功能的TTL门电路

课时授课计划 - 8课号:8课题:3.3.3 其它功能的TTL门电路3.3.4 TTL数字集成电路系列3.3.5 TTL集成逻辑门的使用注意事项目的与要求:熟悉OC门和TTL三态门的工作原理及有关的逻辑概念;了解国际上通用标准型号和我国现行国家标准。

重点与难点:重点:OC门和TTL三态门的应用。

难点:OC门和TTL三态门的工作原理。

教具:课堂讨论:高阻态的含义;OC门和TTL三态门的应用。

现代教学方法与手段:数字电路网络课程PowerPoint复习(提问):TTL集成与非门的外特性;提高TTL集成与非门开关速度的方法。

授课班次:课时分配:提纲3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门的工作原理2.三态输出门的应用3.3.4 TTL数字集成电路系列一、CT54系列和CT74系列二、TTL集成逻辑门电路的子系列三、各系列TTL集成逻辑门电路性能的比较3.3.5 TTL集成逻辑门的使用注意事项一、电源电压及电源干扰的消除二、输出端的连接三、闲置输入端的处理四、电路安装接线和焊接应注意的问题五、调试中应注意的问题作业:P87 3.43.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理工作原理:当输入人A、B、C都为高电平时,V2和V5饱和导通,输出低电平;当输入A、B、C中有低电平时,V2和V5截止,输出高电平。

因此,OC门具有与非功能,其逻辑表达式为:二、与或非门三、三态输出门(TSL门)1.三态输出门的工作原理2.三态输出门的应用(1)用三态输出门构成单向总线(2)用三态输出门构成双向总线3.3.4 TTL数字集成电路系列一、CT54系列和CT74系列表3. 3. 2 CT54系列和CT74系列的对比CT54系列和CT74系列具有完全相同的电路结构和电气性能参数。

8.VHDL语言基础(六)

双向和三态电路设计

1

双向和三态电路信号赋值

1、三态门设计

三态门,简称TSL(Three-state Logic)门,是在普 通门电路的基础上,附加使能控制端和控制电路构成 的。三态门除了通常的高电平和低电平两种输出状态 外,还有第三种输出状态-高阻态。处于高阻态时,电 路与负载之间相当于开路。

双向和三态电路信号赋值

2、双向端口设计 用INOUT模式设计双向端口也必须考虑三 态的使用,因为双向端口的设计与三态端口的 设计十分相似,都必须考虑端口的三态控制。 这是由于双向端口在完成输入功能时,必须使 原来呈输出模式的端口呈高阻态,否则,待输 入的外部数据势必会与端口处原有电平发生 “线与”,导致无法将外部数据正确地读入, 从而实现“双向”的功能。

24

双向和三态电路信号赋值

课堂练习:

修改8位4通道三态总线驱动器的第一 个设计,使其能综合出正确的电路。

25

2

双向和三态电路信号赋值

1、三态门设计

3

双向和三态电路信号赋值

1、三态门设计 三态门用途之一是实现总线传输。总线 传输的方式有两种,单向总线和双向总线。 单向总线方式下,要求只有需要传输信息的 那个三态门的控制端处于使能状态,其余各 门皆处于禁止状态。

4

双向和三态电路信号赋值

三态门实现总线传输的原理:

11

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

12

双向和三态电路信号赋值

2、双向端口设计

双向端口设计实例

13

双向和三态电路信号赋值

14

双向和三态电路信号赋值

2、双向端口设计

分析:

q定义为双向端口,而x定义为三态控制输出口。 在q履行输入功能时,前者没有将其设定为高 阻态输出,即执行语句:q<=“ZZZZZZZZ”,从 而没有使q成为真正的双向端口,导致了错误 的逻辑电路; 执行语句:q<=“ZZZZZZZZ”,使q 在IF 语句 中有了完整的条件描述,从而克服了时序元件 的引入。

数字电路教案-阎石-第三章-逻辑门电路

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

ch3-a---基本逻辑门回顾分析

(1) C 1、C 0 : TN、TP均导通, vO vI (0 ~ VDD)

(2) C 0、C 1 : TN、TP均截止, CvO vI

等效电路

υI / υO

υo/υI

3.2.4 CMOS传输门(双向模拟开关)

2、CMOS传输门电路的工作原理

vI /vO

-5V到+5V

C

+5V

TP +5V vO /vI

2.三态(TSL)输出门电路

VDD

& 10

×10 A

TP 截导止通

01 EN

≥1 10

1 10

L 高01 阻 TN 截截导止止通

三态输出门电路逻辑符号

使能EN 输入A

1

0

输出L 0

A 1L EN

1

1

1

0

×

高阻

逻辑功能:高电平有效的同相三态门

3.3.2 CMOS漏极开路(OD)

真值表

门和三态输出门电路

逻辑真值表

逻辑表达式

vi (A)

0

vO(L)

1

1

0

逻辑图

L A

A1 L

3.2.2 CMOS 反相器

(2)CMOS反相器的工作速度较高

带电容负载

输出从低电平 跳变为高电平

VDD

VDD

输出从高电平 跳变为低电平

VDD

iDP

TP vI

vI=0V vO

TN

iDN

CL

iDP vO vI

CL

iDP

TP vO

TN

3.2.3 其他CMOS门电路

3. CMOS 与门

Y AB AB

三态门的工作原理

三态门的工作原理三态门(Three-state gate)是一种数字逻辑门,用于在某些情况下控制输出线路的导通或断开。

三态门有三个输出状态,分别为高电平、低电平和高阻抗状态。

高阻抗状态相当于输出开路或断路,因此该状态下的输出端的电压等于输入端的电压,但电流几乎为零。

1.三态门的基本结构三态门由一个基本的逻辑门和一个控制电路组成。

基本的逻辑门通常是一个反相器或一个与非门。

控制电路由一个使能端EN和一个反相器组成,该电路的作用是控制逻辑门的输出状态。

2.三态门的输出控制端使能端EN是三态门的输出控制端,该端口的电平决定了三态门的输出状态。

当EN为高电平(1)时,三态门处于正常工作状态,输出状态取决于输入信号。

如果输入信号为高电平(1),则输出为高电平(1),如果输入信号为低电平(0),则输出为低电平(0)。

当EN为低电平(0)时,三态门处于高阻抗状态,输出相当于开路或断路。

此时,输出端的电压等于输入端的电压,但电流几乎为零。

禁用端和使能端是相互独立的控制端,它们可以在同一个三态门上实现不同的控制作用。

禁用端用于禁止输出,当禁用端为高电平(1)时,三态门处于正常工作状态,当禁用端为低电平(0)时,三态门被禁止输出。

3.三态门的输出状态当EN为高电平(1)时,三态门处于正常工作状态,输出状态取决于输入信号。

如果输入信号为高电平(1),则输出为高电平(1),如果输入信号为低电平(0),则输出为低电平(0)。

当EN为低电平(0)时,三态门处于高阻抗状态,输出相当于开路或断路。

此时,输出端的电压等于输入端的电压,但电流几乎为零。

4.三态门的应用三态门在计算机和数字系统中被广泛应用。

例如,在计算机的总线结构中,多个三态门可以连接在同一条总线线上,当某些三态门需要向总线传输数据时,可以通过控制使能端使其处于正常工作状态,而其他不需要传输数据的三态门可以使能端处于高阻抗状态,从而避免总线冲突。

此外,三态门还可以用于实现逻辑电路的复杂组合,例如实现具有“或”和“与”逻辑功能的组合电路。

OC门与三态门

实验3.4 三态门和OC门的应用一、实验目的1.掌握TTL三态门的逻辑应用;2.掌握TTL OC门的逻辑应用;3.熟悉TTL三态门、OC门电路应用的测试方法。

二、知识点三态门和OC门输出端可并接。

三态门有低电平、高电平和高阻三种状态;OC门可实现“线与”功能。

三、实验原理在实际应用中,常需要把几个逻辑门的输出端并联使用,实现逻辑与,称为“线与”。

但普通TTL门电路不允许将输出端直接并联在一起,因为这种门电路输出高电平还是低电平,其输出电阻都很小,只有几欧姆或几十欧姆。

若把两个TTL门输出端连在一起,当其中一个输出高电平,另一个输出低电平时,它们中的导通管就会在Vcc和地之间形成一个低阻串联通路,通过这两个门的输出级产生很大的电流,损坏电路。

图3-3-1示出了两个TTL门输出短接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。

设门A处于截止状态,若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。

在把门A和门B的输出端作如图3-3-1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导通的 T5到地,形成了一个低阻通路,其不良后果为:(1)输出电平既不是高电平也不是低电平,而是两者之间的某一值,导致逻辑功能混乱;(2)上述通路导致输出级电流远大于正常值,导致功耗剧增,发热增大,可能烧坏器件。

图3-4-1普通TTL门输出短接1.三态门(TS门)三态门,简称TSL(Three-state Logic)门,是在普通门电路的基础上,附加使能控制端和控制电路构成的。

三态门除了通常的高电平和低电平两种输出状态外,还有第三种输出状态——高阻态。

处于高阻态时,电路与负载之间相当于开路。

(a )使能端高电平有效 (b )使能端低电平有效 图3-4-2三态门的结构和逻辑符号图3-4-2所示为三态门的结构和逻辑符号,图(a)是使能端高电平有效的三态与非门,当使能端EN = 1时,电路为正常的工作状态,与普通的与非门一样,实现Y = ;当EN = 0时,为禁止工作状态,Y 输出呈高阻状态。

数字逻辑课件——TTL集电极开路的门和三态门

当EN1 = 1而其余为0时,门G2和G3呈 高阻,信号A1的非送到了总线Y上;

1

0

0

图2-2-23 用三态非门构 成单向总线

15

当仅有EN2 = 1时,信号A2的非送到 了总线Y上;

当仅有EN3 = 1时,信号A3的非送到 了总线Y上。

这样,就实现了信号A1,A2,A3向总 线Y的分时传送。见表2-2-3所示,

与非门1:

i

功耗

T4热击穿

与非门2:UOL

不允许输出直接“短

接”

2

(1)输出电平既非“1”(3.6V),也非“0”(0.3V),而 是两者之间的某一值,导致逻辑混乱。 (2)导致输出级电流远大于正常值,导致功耗剧增,可能烧 毁管子。 两种允许输出端连接在一起的TTL电路。 (一)集电极开路门电路—OC门(Open-Collector Gate) 集电极开路与非门的电路结构与逻辑符号示于图2-2-19。它

而当两个门的输出端连在一起,只要其中 有一个输出低电平(即VT5和VT’5中至少 有一个饱和),总的输出Y就是低电平;

7

只有当两个门都输出高电平(即VT5和 VT’5都截止)时,总的输出Y才是高电平, 这相当于“与”逻辑关系:

Y Y1 Y2 A1B1 A2B2

8

由于这个“与”关系是通过将输出线Y1和Y2短接实现的,

27

VD3的作用:VD3经过VT2为VT4提 供了一个低电阻放电回路,使

VT4更快地截止,有利于缩短传 输延迟时间。

VD4的作用:Y由高变低时,VD4经 VT2c、VT5b为CL提供另一条放电回 路,既加快了CL的放电速度,又 为VT5增加了基极驱动电流,加 快了VT5的导通。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2011-12-31

2.4 2.4 其它类型其它类型其它类型TTL TTL TTL门电路门电路门电路

复习

TTL反相器的电压传输特性有哪几个区?

TTL反相器主要有哪些特性?

TTL反相器的主要参数有哪些?

2011-12-312

2011-12-313

2.4.1 TTL 与非门

每一个发射极能各自独立形成正向偏置的发

射结,并可使三极管进入放大或饱和区。

图2-16 多发射极三极管

1.TTL与非门的电路结构及工作原理

1V 2.1V

有0输出1

全1输出0

图2-17 三输入TTL与非门电路

(a)电路 (b) 逻辑符号

2011-12-314

2.TTL门电路的改进系列

为了提高工作速度,降低功耗,提高抗干扰能力,各生产厂家对门电路作了多次改进。

74系列与54系列的电路具有完全相同的电路结构和电气性能参数。

其不同之处见下表所示。

2011-12-315

表2-6不同系列TTL门电路的比较

其中LS系列的综合性能(功耗延迟积)较优,价格较ALS系列优越,因此得到了较广的应用。

2011-12-316

对于不同系列的TTL器件,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。

例如,7420、74H20、74S20、74LS20都是四输入双与非门,都采用14条引脚双列直插式封装,而且各引脚的位置也是相同的。

2011-12-317

2.4.2 集电极开路门(OC门)

推拉式输出电路结构存在局限性。

首先,输出端不能并联使用。

若两个门的输出一高一低,当两个门的输出端并联以后,必然有很大的电流同时流过这两个门的输出级,而且电流的数值远远超过正常的工作电流,可能使门电路损坏。

而且,输出端也呈现不高不低的电平,不能实现应有的逻辑功能。

2011-12-318

2011-12-31

9图2-18 推拉式输出级并联的情况

其次,在采用推拉式输出级的门电路中,电源一经确定(通常规定为5V),输出的高电平也就固定了(不可能高于电源电压5V),因而无法满足对不同输出高电平的需要。

集电极开路门(简称OC门)就是为克服以上局限性而设计的一种TTL门电路。

2011-12-3110

2011-12-31

11

(1)电路结构:输出级是集电极开路的。

1.集电极开路门的电路结构

(2)逻辑符号:用“◇”表示集电极开路。

图2-19 集电极开路的TTL与非门(a)电路 (b)逻辑符号

集电极开路

(3)工作原理:

=0.3V;

当VT3饱和,输出低电平U

OL

当VT3截止,由外接电源E通过外接上拉电阻

=E。

提供高电平U

OH

因此,OC门电路必须外接电源和负载电阻,才能提供高电平输出信号。

2011-12-3112

2011-12-31

(1) OC 门的输出端并联,实现线与功能。

R

R 图2-20 OC 门的输出端并联实现线与功能 Y 1

0011

Y 1 Y 2CD

AB CD AB Y Y Y +=•=•=212. OC门的应用举例

2011-12-31

14

图2-21 用OC门实现电平转换的电路

(2)用OC 门实现电平转换

2.4.3 三态输出门电路(TS门)

三态门电路的输出有三种可能出现的状态:高电平、低电平、高阻。

悬空、悬浮状态,又称为禁止状态。

测电阻为∞,故称为高阻状态。

测电压为0V,但不是接地。

因为悬空,所以测其电流为0A。

2011-12-3115

1.三态门的电路结构

01

截止

Y=

2011-12-3116

2011-12-31

17

1

导通

1.0V

1.0V

截止

截止

悬空

控制端低电平有效的三态门

控制端高电平有效的三态门

2011-12-3118

2011-12-31

19

2.三态门的主要应用-实现总线传输 要求各门的控制端EN 轮流为高电平,且在任何时刻只有一个门的控制端为

高电平。

图2-23 用三态门实现总线传输

如有8个门,则8个EN 端的波形应依次为高电平,如下页所示。

2011-12-3120。