计算机组成原理 第15讲_流水线

计算机组成原理中的流水线与并行处理

计算机组成原理中的流水线与并行处理计算机组成原理是指计算机的各个组成部分及其相互关系的原理。

其中,流水线与并行处理是计算机组成原理中的两个重要概念。

本文将从流水线和并行处理的定义、特点、应用以及优缺点等方面进行论述。

一、流水线的定义和特点流水线技术是一种将复杂的任务分解为若干个互相依赖的子任务,并通过时序控制将其分别交给不同的处理单元进行执行的技术。

它可以提高计算机的执行效率和吞吐量。

与串行处理相比,流水线处理具有以下特点:1.任务分解:将复杂的任务分解为多个子任务,每个子任务由不同的处理单元负责执行。

2.流水线寄存器:通过在流水线各个阶段之间插入流水线寄存器,实现了各个阶段之间的数据传递和暂存,确保了数据的正确性和稳定性。

3.并行操作:不同的处理单元可以并行执行不同的任务,提高了计算机的并行处理能力。

4.随机任务执行:由于流水线中的各个阶段是独立的,因此可以随机运行和停止任务,提高了计算机的灵活性。

二、并行处理的定义和特点并行处理是指同时利用多个处理器或者多个处理单元并行执行多个任务的处理方式。

它可以大幅提升计算机系统的运算速度和处理能力。

并行处理的特点如下:1.任务分配:将大任务分解为多个小任务,并分配给多个处理单元同时执行。

2.任务协调:通过合理的任务调度算法,协调各个处理单元之间的任务执行顺序和数据传递,确保整个系统的稳定性和正确性。

3.资源共享:各个处理单元之间可以共享资源,如内存、缓存等,提高资源利用率。

4.计算效率提高:通过多个处理单元同时执行任务,大幅提高了计算效率和处理速度。

三、流水线与并行处理的应用流水线和并行处理在计算机领域被广泛应用,以下是几个常见的应用示例:1.超级计算机:超级计算机通常采用并行处理的方式,利用多个处理器同时进行计算,以提高计算能力。

2.图形处理器:图形处理器(GPU)采用流水线技术,将图像处理任务分解为多个子任务,通过流水线处理实现高效的图形渲染和计算。

计算机组成原理之流水线处理机(ppt 59页)

计算机组成原理

7

7

流水线的基本概念

什么是流水线

计算机中的流水线是把一个重复的过程分解为若干个子过 程,每个子过程与其他子过程并行进行。由于这种工作方式与 工厂中的生产流水线十分相似,因此称为流水线技术。 从本质上讲,流水线技术是一种时间并行技术。

计算机组成原理

8

8

计算机的各个部分几乎都可以采用流水线技术:

计算机组成原理

2

2

将解决的主要问题

掌握流水线处理机的数据路径 建立指令流水线中指令如何重叠执行和流动

了解流水线工作原理以及相关问题

计算机组成原理

3

3

单周期处理机

指令 存储器 PC Add

D ata

W ritePC

disp

rs1 rd

1

rs2

0

S e lS t im m e

SelB ranch

偏移量符 号扩展

rd(rs1) and imme

rd (rs1) or (rs2)

计算机组成原理

25

25

31 26 25 21

00 0000

rd

00 0001

rd

00 0010

rd

00 0011

rd

00 0100

rd

00 0101

rd

00 0110

rd

00 0111

rd

00 1000

rd

00 1001

rd

00 1010

00 1011

00 1100

计算机组成原理

指令系统和指令格式

20 16 rs1

00010 rs1

00101 rs1

00101 rs1

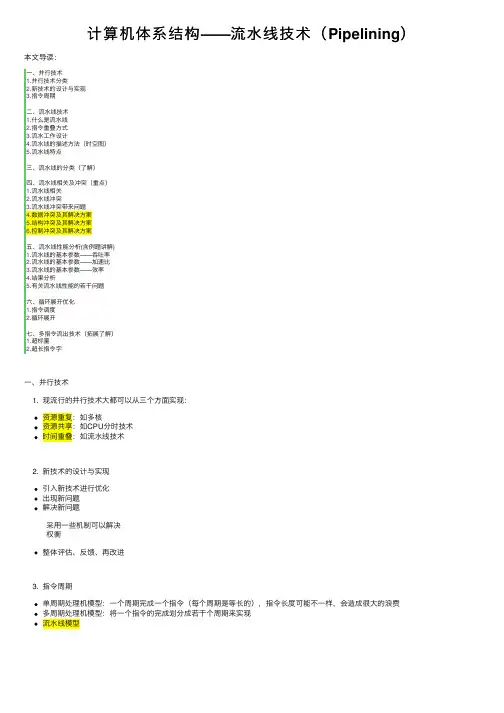

计算机体系结构——流水线技术(Pipelining)

单功能流水线:流水线只完成一种固定功能 多功能流水线:流水线可以完成多种功能,如 TI公司的ASC机,8段流水线,能够实现:定点加减 法、定点乘法、浮点加法等功能 3.按同一时间内各段之间的连接方式分 静态多功能流水线 :同一时间内,多功能结构只能按一种功能的连接方式工作。 动态多功能流水线:在同一时间内,可以有多种功能的连接方式同时工作 4.按处理的数据类型 标量流水线 向量流水线 5.按控制方式 同步流水线 异步流水线:当Si功能段要向Si+1段传送数据时,首 先发出就绪信号,Si+1功能段收到信号后,向Si回送 一个回答信号。 6.按任务从输出端的流出顺序 顺序流水方式:指令流出顺序 = 指令流入顺序 乱序流水方式:指令流出顺序 != 指令流入顺序 7. 线性流水线——不带反馈回路的流水线

三、流水线的分类(了解)

四、流水线相关及冲突(重点) 1.流水线相关 2.流水线冲突 3.流水线冲突带来问题 4.数据冲突及其解决方案 5.结构冲突及其解决方案 6.控制冲突及其解决方案

五、流水线性能分析(含例题讲解) 1.流水线的基本参数——吞吐率 2.流水线的基本参数——加速比 3.流水线的基本参数——效率 4.结果分析 5.有关流水线性能的若干问题

整体评估、反馈、再改进

3. 指令周期

单周期处理机模型:一个周期完成一个指令(每个周期是等长的),指令长度可能不一样,会造成很大的浪费 多周期处理机模型:将一个指令的完成划分成若干个周期来实现 流水线模型

二、流水线技术 1. 什么是流水线? 计算机中的流水线是把一个重复的过程分解为若干个子过程,每个子过程与其他子过程并行进行。由于这种工作方式与工厂中的生产 流水线十分相似, 因此称为流水线技术 从本质上讲,流水线技术是一种时间并行技术。

计算机组成原理流水线设计基础知识全面解析

计算机组成原理流水线设计基础知识全面解析计算机组成原理是计算机科学与技术的基础课程之一,而流水线设计则是其中的重要内容之一。

本文将全面解析计算机组成原理流水线设计的基础知识,介绍其工作原理、优势、流水线冲突及解决方法等内容。

一、工作原理计算机组成原理中,流水线设计是通过将指令的执行过程划分为多个阶段,并将这些阶段在不同的处理单元上并行执行的方式,从而提高指令的执行效率。

流水线设计主要包含以下几个阶段:1. 取指令阶段(IF):从内存中读取指令并将其送至指令译码器。

2. 指令译码阶段(ID):对指令进行解码,判断其类型,并提取相关寄存器的值。

3. 执行阶段(EX):根据指令的类型,对操作数进行计算,并将结果保存至寄存器中。

4. 访存阶段(MEM):如果指令需要访问内存,则进行内存读取或写入操作。

5. 写回阶段(WB):将计算结果写回到寄存器中。

通过将指令的执行划分为多个阶段,并使用多个处理单元并行执行,流水线设计可以大大提高指令的执行效率,加快程序的运行速度。

二、优势流水线设计具有以下几个优势:1. 并行处理:通过将指令的执行划分为多个阶段,并使用多个处理单元并行执行,可以加快指令的执行速度。

2. 提高资源利用率:由于每个处理单元都可以执行不同的指令阶段,因此可以充分利用硬件资源,提高整体的资源利用率。

3. 灵活性:不同的指令可以使用不同的处理单元进行执行,在保持高效率的同时,增加了系统的灵活性,可以执行更多的指令类型。

然而,除了以上的优势外,流水线设计也存在一些问题,即流水线冲突。

三、流水线冲突及解决方法1. 结构冲突:当多个指令需要使用同一硬件资源时,会发生结构冲突。

例如,同时对存储器进行读取和写入操作。

解决方法:通过增加硬件资源的数量或调整指令的执行顺序,可以避免结构冲突的发生。

2. 数据冲突:当后续指令需要使用前一条指令的运算结果时,会发生数据冲突。

例如,一条指令的结果被另一条指令使用。

解决方法:可以通过插入空闲周期或使用旁路机制,将结果传递给后续指令,从而解决数据冲突。

计算机组成原理中央处理器与流水线技术

计算机组成原理中央处理器与流水线技术计算机组成原理是计算机科学中的基础课程之一,它主要研究计算机系统的硬件组成和工作原理。

而中央处理器(Central Processing Unit,简称CPU)作为计算机的核心部件之一,承担着指令的译码、执行和数据处理等关键任务。

为了提高CPU的运行效率和性能,流水线技术被引入其中。

本文将对计算机组成原理中央处理器以及流水线技术进行探讨。

一、中央处理器的基本结构和功能中央处理器作为计算机系统的核心,它主要由控制器和运算器两部分组成。

其中,控制器负责对指令的解码和控制,而运算器则负责执行这些指令并进行数据的处理。

控制器是中央处理器的指挥中枢,它接收来自主存储器的指令,并对其进行解码和分析。

解码后的指令将被传送到运算器,根据指令的要求,运算器会执行相应的运算操作,并将结果返回到主存储器或其他设备。

运算器主要由算数逻辑单元(ALU)和寄存器组成。

ALU负责执行各种算术运算和逻辑运算,寄存器则用于存储指令和数据。

在运算过程中,ALU可以根据指令的要求,通过寄存器之间的数据传输和运算来完成各种运算操作。

二、中央处理器与流水线技术的关系为了提高CPU的执行效率和性能,流水线技术被引入其中。

流水线技术是基于指令级并行的思想,将指令的执行过程划分为多个子任务,并通过流水线的方式并行执行这些子任务,从而提高CPU的吞吐量。

1. 流水线技术的原理流水线技术将整个指令的执行过程划分为多个阶段,每个阶段完成一个特定的操作。

这些阶段依次连接在一起,形成一个流水线。

当一个指令进入流水线后,它会按照顺序经过各个阶段的处理,直至完成。

而在同一时刻,不同指令的不同阶段可以并行执行,从而提高了整个流水线的效率。

2. 流水线技术的优势流水线技术的引入使得CPU能够同时处理多条指令,提高了整体的执行效率。

同时,流水线技术还具有以下几个优点:(1)资源复用:不同阶段的操作可以使用相同的硬件资源,提高硬件资源的利用率。

计算机组成原理与系统结构流水线技术

(1) 实现。 (2) 注意问题。

2) 精确断点

4. 乱序执行

17

6.3.6 带成功开销的流水线性能

18

6.4 指令级并行

6.4.1 指令级并行概述

1. 指令流水线的限制 2. 突破限制的途径

19

6.4.2 提高指令级并行的方法

1. 指令调度

1) 静态调度 2) 动态调度

(1) 能调度在编译时不可能知道的竞争情况。 (2) 符合程序执行的实际情况。 (3) 具有更高的效率和准确性。 (4) 简化编译程序设计。 (5) 代码的移植性强。

7

6.2.1 吞吐率

1. 最大吞吐率TPmax

1) 各段时间相等的流水线

2) 各段时间不相等的流水线

(1) 将瓶颈细分。

(2) 利用重复设置。

2. 实际吞吐率TP

1) 各段时间相等的流水线

2) 各段时间不相等的流水线

8

6.2.2 加速比

1. 各段时间相等 的流水线

2. 各段时间不相 等的流水线

9

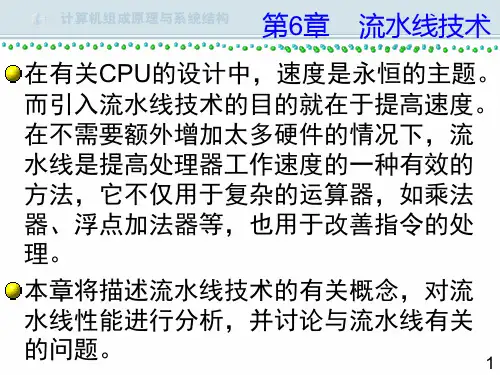

第6章 流水线技术

在有关CPU的设计中,速度是永恒的主题。 而引入流水线技术的目的就在于提高速度。 在不需要额外增加太多硬件的情况下,流 水线是提高处理器工作速度的一种有效的 方法,它不仅用于复杂的运算器,如乘法 器、浮点加法器等,也用于改善指令的处 理。

本章将描述流水线技术的有关概念,对流 水线性能进行分析,并讨论与流水线有关 的问题。

20

6.4.2 提高指令级并行的方法

2. 乱序执行和寄存器重命名

1) 顺序执行

2) 乱序执行

(1) 记分牌法。

❖① 发射级。

❖② 读操作数。

❖③ 执行。

计算机体系结构之流水线技术(ppt 125页)

张伟 计算机学院

大纲

1 概念定义 2 流水线分类 3 MIPS五级流水线 4 性能分析 5 流水线相关 6 高级流水线技术

1 概念定义

洗衣店的例子

A, B, C, D 均有一些衣物要 清洗,甩干,折叠

清洗要花30 分钟 甩干要用40 分钟 叠衣物也需要20 分钟

流水线输出端任务流出的顺序与输入端任务流 入的顺序相同。

异步流动流水线(乱序流水线):

流水线输出端任务流出的顺序与输入端任务流 入的顺序不同。

3 MIPS五级流水线

DLX(Dancing Links)

DLX 是一种简单的指令集(教学、简单芯片) 在不流水的情况下,如何实现DLX。

实现DLX指令的一种简单数据通路

4. 存储器访问周期MEM(Memory Access) 5. 写回周期WB(Write Back)

MIPS的简单实现

Instruction Fetch

Instr. Decode Reg. Fetch

Next PC

Next SEQ PC

4

RS1

RS2

Execute Addr. Calc

Zero?

RD

增加了向后传递IR和从MEM/WB.IR回送到通用寄存 器组的连接。

将对PC的修改移到了IF段,以便PC能及时地加 4,为取下一条指令做好准备。

2. 每一个流水段进行的操 作

IR[rs]=IR6..10 IR[rt]=IR11..15 IR[rd]=IR16..20

流水线的每个流水段的操作

将有效地址计算周期和执行周期合并为一个时钟周期,这

是因为MIPS指令集采用load/store结构,没有任何指令

需要同时进行数据有效地址的计算、转移目标地址的计算

计算机系统结构之流水线技术(205页)

入 求阶差

△t

对阶 △t

尾数相加 △t

出 规格化

△t

▲

31/206

1. 时空图 ➢ 时空图从时间和空间两个方面描述了流水线的工作 过程。时空图中,横坐标代表时间,纵坐标代表流 水线的各个段。 ➢ 4段指令流水线的时空图:

空间

存结果

123456

执行 译码

123456

5

123 45 6

取指令 1

2

3

4

k…+…1 k+j

已经由指令分析器预处理完成,存放在先行操作栈中的 RR*型指令,指令所需要的操作数已经读到先行读数栈中

k…+…j+1 k+j+n

已经由指令分析器预处理完成,存放在先行操作栈中,指 令所需要的操作数还没有读到先行读数栈中

k+j+n+1 正在指令分析器中进行分析和预处理的指令

k…+…j+n+2 已经从主存储器中预取到先行指令缓冲栈中的指令 k+j+n+m

1

2

3

…

1

2

3

…n

1

2

3

…

n

2

3

k

ti

i1

…n (n-1)t2

Tk 各段执行时间不相等的流水线及其时空图

n

时间

▲

33/206

2 流水线的基本概念

➢ 流水线每一个功能部件的后面都要有一个缓冲寄 存器(锁存器),称为流水寄存器。

站的某个存储单元(设其地址为j),同时用j替换原来指令

中的目标地址码字段。

✓ 立即数型指令:把指令中的立即数送入读数站(设为第l个 存储单元),同样也用l替换原来指令中的立即数字段。

计算机组成原理基础知识流水线技术和超标量处理器

计算机组成原理基础知识流水线技术和超标量处理器计算机组成原理基础知识:流水线技术和超标量处理器计算机组成原理是指计算机硬件的基本组成和工作原理。

在计算机科学与技术领域,流水线技术和超标量处理器是两个重要的概念。

本文将介绍这两种技术的基本原理和应用。

一、流水线技术流水线技术是指将一个复杂的操作分解成多个简单的子操作,并将这些子操作连续地执行,以提高计算机的指令执行效率。

在传统的自顶向下的设计方法中,计算机硬件主要包括控制器、运算器等单一功能模块,而在流水线技术中,计算机硬件被划分成多个阶段,每个阶段执行一个特定的功能子模块。

经典的流水线包括取指、译码、执行、访存和写回等阶段。

在取指阶段,计算机从存储器中读取指令;在译码阶段,计算机对指令进行解码并读取相应的操作数;在执行阶段,计算机执行相应的操作;在访存阶段,计算机对数据进行读写操作;在写回阶段,计算机将执行结果写回到寄存器或存储器。

流水线技术的优点是可以充分利用计算机硬件资源,提高指令的并行执行程度。

但是,流水线技术也存在一些问题,例如数据的相关性和冒险问题,需要通过一些技术手段来解决。

二、超标量处理器超标量处理器是一种在流水线技术基础上的改进方案。

传统的流水线技术中,每个阶段只能执行一个指令,而超标量处理器允许在同一个时钟周期内执行多个指令,以进一步提高计算机的执行效率。

超标量处理器主要依靠两个关键技术来实现多指令并行执行:乱序执行和动态调度。

乱序执行是指根据指令之间的依赖关系,按照合理的顺序执行指令,而不是按照指令在程序中的顺序执行。

动态调度是指通过硬件对指令进行调度,在不改变程序语义的前提下,尽可能地重排指令的执行顺序,以提高指令的并行度。

超标量处理器的工作原理可以简单描述为:在取指阶段,计算机从存储器中读取多个指令;在译码阶段,计算机对这些指令进行解码;在执行阶段,计算机并行执行多个指令;在访存阶段,计算机同时进行多个数据的读写操作;在写回阶段,计算机将执行结果写回到寄存器或存储器。

计算机组成原理与指令流水线性能优化概述

计算机组成原理与指令流水线性能优化概述计算机组成原理是计算机科学中的重要课程,它研究计算机硬件系统的组成和工作原理,包括中央处理器(CPU)、存储器、输入输出设备等。

而指令流水线是计算机中的一种重要的优化技术,通过对指令执行过程进行流水线化,以提高处理器的执行效率。

本文将从计算机组成原理和指令流水线的基本概念入手,探讨如何进行性能优化。

一、计算机组成原理概述计算机组成原理是研究计算机硬件系统如何组成,以及各个部件如何协同工作的学科。

计算机硬件系统主要包括中央处理器(CPU)、存储器、输入输出设备等。

其中,CPU是计算机的核心部件,主要负责执行程序指令,其性能直接影响到计算机的运行速度。

计算机组成原理的研究围绕着提高计算机的性能,降低成本,提高可靠性等目标展开。

其主要内容包括指令系统设计、CPU结构设计、存储器层次结构设计、输入输出系统设计等。

通过对这些部件的优化,可以提高计算机的性能。

二、指令流水线的基本概念指令流水线是一种将指令执行过程划分为多个阶段,并通过并行执行提高处理器效率的技术。

在传统的单周期执行方式中,每条指令的执行需要占用一个时钟周期。

而指令流水线将每条指令的执行划分为多个阶段,不同指令在不同阶段同时执行,从而提高了处理器的吞吐量。

指令流水线的基本阶段包括取指令(IF)、指令译码(ID)、执行(EX)、访存(MEM)和写回(WB)等。

每个阶段只需占用一个时钟周期,而不同指令在不同阶段之间交错执行,从而实现多条指令的并行执行。

指令流水线的工作原理类似于流水线上的工厂,每个工人负责完成流水线上的一个工序,从而实现生产效率的提高。

三、指令流水线性能优化的方法1. 增加流水线级数:流水线级数是指流水线中的阶段数,增加流水线级数可以进一步提高处理器的性能。

较长的流水线可以使得吞吐量更大,但也会增加流水线的延迟。

因此,在提高流水线级数时需要平衡吞吐量和延迟,选择适当的流水线级数。

2. 解决数据冒险问题:数据冒险是指在指令流水线中,后一条指令需要用到前一条指令的结果,但前一条指令的结果还未计算出来,导致流水线停顿的情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

将一个重复的时序过程分解成为多个子过程Subprocess。每个 子过程都可有效地在其专用功能段上与其它子过程同时执行。

例如,分成4个功能段Segment: 入口 取 指 令 指令 译码 取操 作数 执行

出口

9

时空图 Space-Time-Diagram 各功能段时间相等

空间

执行

(功能段)

通过时间

Instruction level parallelism In the best case scenario, this pipeline can sustain a completion rate of one instruction per cycle.

16

流水技术的特点 ① 流水线可分成若干个互有联系的子过程,分别由专用功 能段实现。 ② 实现子过程的功能段所需时间尽可能相等,避免因不等 而产生处理的瓶颈,形成流水线的断流。

4

§6.5 流水线工作原理

计算机的速度可以用每秒执行的指令条数来表示。 指令的解释 怎样加快一条指令的解释过程? 为了加快单条指令的解释过程可采用的方法有:

•选用更高速的器件

•减少解释过程所需拍数 •使解释过程的各个动作并行执行 指令的解释可以有三种控制方式:顺序,重叠,流水。

5

1.顺序方式 各条机器指令间顺序串行执行。一条指令执行完之后,才取 下条指令来执行。指令内的各条微指令也是顺序串行执行的。 例如,把解释一条机器指令分为:取指,分析,执行,3个 子过程。

20

解决访存冲突的方法: 取指k 分析k 执行k

取指k+1

分析k+1 取指k+2 k+1

执行k+1 分析k+2

执行k+2

① 采用“哈佛结构”。指令和操作数分别存放在2个独立编址且 可同时访问的存储器内。 ② 采用多体交叉存储器。使第k条指令的操作数与第k+1条指令 不在同一个存储体内。 ③ 设置指令缓冲寄存器组。把若干条指令预先从主存取到指缓。 取指令部件从指缓取指令,执行部件从主存取操作数,互相不干 扰。只要指缓不满,就自动从主存预取指令。

回 写 结 果 部 件

修 改 指 令 指 针 部 件

在指令流水过程中要不断访存,所需时间不确定,难以 用统一的时钟控制各段工作。

18

流水线结构 ② 运算操作流水线 Arithmetic Pipelining 按照指令的要求,选择合适的算法,把运算过程分成多个子 过程。使各个子过程的时间尽量相等。 对 阶 功 能 部 件 尾 数 加 部 件 规 格 化 部 件

Model of a subscalar CPU.

3

Model of a subscalar CPU.

This process gives rise to an inherent inefficiency in subscalar CPUs. Since only one instruction is executed at a time, the entire CPU must wait for that instruction to complete before proceeding to the next instruction.

设各段时间相等,每段效率ei相等, e0 = e1 = ……= em : e0 = n·Δt0/T = n/(m+(n-1))

m e0 n m t0 m m m T 若各段时间不等,则各段的效率也不等,整个流水线的效率

整个流水线的效率

i

e E

E

n t i

i 1

取指k 取指k 执行k 执行k 取指k+1 执行k+1 取指k+2 执行k+2 取指k+1 执行k+1 取指k+2 执行k+2 取指k+3 执行k+3

理想情况

取指k+3 执行k+3

不同指令在各个阶段 所需时间不同 取指k 执行k

实际情况?

取指k+1

执行k+1

取指k+2 一次重叠

8

执行k+2

3.流水方式 Pipelining One of the simplest methods used to accomplish increased parallelism is to begin the first steps of instruction fetching and decoding before the prior instruction finishes executing. This is the simplest form of a technique known as instruction pipelining, and is utilized in almost all modern general-purpose CPUs.

计算机组成原理

Principles of Computer Organization

广义双语教学课程

青岛理工大学 校级精品课程

http://211.64.192.109/skyclass25/ /ec/C84/

计算机组成原理设计性作业

第8周周末完成

课题3 组合逻辑控制单元设计

12

② 加速比 Speedup Ratio m段流水线的速度与等效的非流水线的速度之比。 •若各段时间相等 完成n个任务的时间: T流水= m·Δt0 + (n-1)·Δt0 T非流水= n·m·Δt0 加速比:

n m t0 T非流水 nm SP m t0 (n 1) t0 T流水 m n 1

This design, wherein the CPU's execution resources can operate on only one instruction at a time, can only possibly reach scalar performance (one instruction per clock). However, the performance is nearly always subscalar (less than one instruction per cycle).

锁 存 器

锁 存 器

锁 存 器

各段与一个统一的时钟同步。

在各段间增加锁存器。

19

流水线要解决的技术问题 要实现重叠和流水,还要解决:访存冲突,相关,等问题。 1.访存冲突 Resource Conflicts 在同一时间段,“分析k”在形成操作数有效地址后要访存取 操作数,而“取指k+1”也需访存取指令。 取指k 分析k 取指k+1 执行k 分析k+1 取指k+2 k+1 执行k+1 分析k+2 执行k+2

11

流水线的主要技术指标有:吞吐率,加速比,效率,等。 ① 吞吐率 Throughput Rate 单位时间内流水线所能处理的任务数(或指令数),或流 水线能输出的结果的数量。 最大吞吐率: 当流水线在连续流动达到稳定状态后的吞吐率。

如果各功能段时间都相等,Δti=Δt0

TPmax=1/Δt0

如果各功能段时间不相等,TPmax=1/max(Δti) 取决于最慢的段。

③ 形成流水处理需要一段准备时间,称为“通过时间”。 此后,流水过程才能稳定。

④ 指令流发生不是顺序执行时,会使流水过程中断。再形 成流水过程需“通过时间”。要提高效率,不应常断流。 ⑤ 流水线技术适用于大量重复的程序过程。只有在输入端 能连续地提供任务,流水线效率才能充分发挥。

17

流水线结构 ① 指令流水线 Instruction Pipeline 要求指令部件每个节拍输出一条指令给执行部件。指令流水 过程要分成更多的子过程。 取 指 令 部 件 指 令 译 码 部 件 地 址 形 成 部 件 取 操 作 数 部 件 操 作 执 行 部 件

取指k+1

执行k+1 取指k+2

Δt

执行k+2

重叠解释不能加快一条指令的实现,但能加快相邻两条指 令以至一段程序的解释。 重叠方式把一条指令的解释过程分解成“取指”,“执行” 两个子过程。若每个子过程需Δt时间,一条指令需2Δt时间完成。 机器每隔Δt时间完成一条指令的解释。吞吐率提高一倍。

7

重叠方式与顺序方式的比较

m m 1 1 n

13

② 加速比 Speedup Ratio m段流水线的速度与等效的非流水线的速度之比。 •若各段时间不等 加速比:

SP

n ti

i 1

m

Δtj是最慢的一段时间

t

i 1

m

i

(n 1) t j

14

流水线上的各段有 “通过时间”和“排空时间”, ③ 效率 Efficiency 并非都是满负荷工作。 流水线上的设备利用率就是效率。

用硬布线(组合逻辑)控制法设计一个简单模型机的控 制单元CU(微操作信号产生电路)。 假设该模型机有 8 条不同类型的指令。包括:算术运算、 逻辑运算、移位、数据传送、访存操作、转移等。根据每条 指令的功能和时序,分析其执行过程中需要在各个阶段产生 的全部微操作,导出产生这些微操作控制信号的逻辑。

提示:需要决定指令周期包括哪几个机器周期,每个机器周期 包括几拍,每拍包括几个时钟,以及时钟周期是多少nS。有些 操作可能还需要规定是在时钟的上升沿或是在时钟的下降沿进 行。

2

第6章 中央处理器

Chapter 6 Central Processing Unit

(5) The description of the basic operation of a CPU offered in the previous section describes the simplest form that a CPU can take. This type of CPU, usually referred to as subscalar, operates on and executes one instruction on one or two pieces of data at a time.