STC89C52单片机存储器扩展

STC89C52单片机用户手册

STC89C52单片机用户手册一、概述STC89C52 单片机是一款高性能、低功耗的 8 位微控制器,具有丰富的片内资源和强大的功能,广泛应用于各种电子设备和控制系统中。

二、主要特点1、增强型 8051 内核,指令代码完全兼容传统 8051 单片机。

2、工作电压范围宽,可在 38V 55V 之间正常工作。

3、片内集成 8K 字节的 Flash 程序存储器,可反复擦写 1000 次以上。

4、 512 字节的片内数据存储器(RAM)。

5、拥有 32 个可编程的 I/O 口,方便连接外部设备。

6、 3 个 16 位定时器/计数器,可用于定时、计数和脉冲宽度测量等功能。

7、 8 个中断源,包括 2 个外部中断、3 个定时器中断和 2 个串行口中断,具有两级中断优先级。

8、全双工串行通信接口(UART),可方便地与其他设备进行通信。

三、引脚功能1、 VCC:电源正极,接+5V 电源。

2、 GND:电源地。

3、 P0 口:8 位漏极开路双向 I/O 口,作为地址/数据总线分时复用口。

4、 P1 口:8 位准双向 I/O 口,具有内部上拉电阻。

5、 P2 口:8 位准双向 I/O 口,作为高 8 位地址总线。

6、 P3 口:8 位准双向 I/O 口,具有第二功能。

例如,P30 为串行输入口(RXD),P31 为串行输出口(TXD)等。

四、存储结构1、程序存储器STC89C52 单片机的程序存储器空间为 8K 字节,地址范围为0000H 1FFFH。

用于存放用户编写的程序代码。

2、数据存储器数据存储器分为内部数据存储器和外部数据存储器。

内部数据存储器包括低 128 字节的 RAM(地址范围为 00H 7FH)和高 128 字节的特殊功能寄存器(SFR,地址范围为 80H FFH)。

外部数据存储器最大可扩展至 64K 字节。

五、时钟与复位1、时钟电路STC89C52 单片机可以使用内部时钟和外部时钟。

内部时钟通过在XTAL1 和 XTAL2 引脚之间连接晶振和电容来产生时钟信号。

STC89C52系列单片机

ISP/IAP操作时的地址寄存器高八位; (3) ISP_ADRRL(E4H):

ISP/IAP操作时的地址寄存器低八位; (4) ISP_CMD(E5H):

ISP/IAP操作时的命令模式寄存器,须命 令触发寄存器触发方可生效;

P4口各位可位寻址.

2021/7/1

10

五、看门狗电路 WDT_CONTR (E1H)

D7 D6 D5 D4 D3 D2 D1 D0

-

-

EN_ CLR_ IDLE_ WDT WDT WDT

PS2 PS1

PS0

EN_WDT: 看门狗允许位,

置“1”时,看门狗启动;

CLR_WDT:看门狗清“0”位,

置“1”时,看门狗将重新计数;

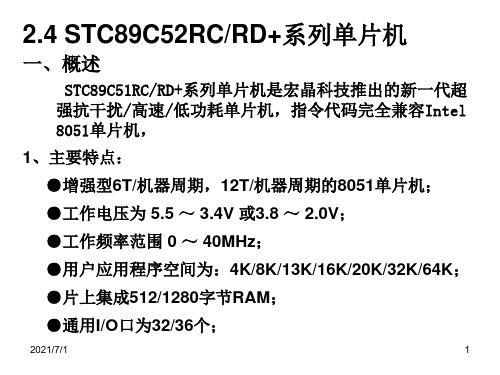

●工作频率范围 0 ~ 40MHz;

●用户应用程序空间为:4K/8K/13K/16K/20K/32K/64K;

●片上集成512/1280字节RAM;

●通用I/O口为32/36个;

2021/7/1

1

● ISP/IAP功能,可直接通过串口下载用户程序;

●片内EEPROM;

●看门狗功能;

● 4路外部中断,且省电模式可由外部中断低电平触发中 断方式唤醒;

2021/7/1

5

二、扩展RAM的使用

1、RAM的大小 STC89C51RC:

内部RAM 256Byte,XRAM 256Byte, 共512Byte;

STC89C51RD+: 内部RAM 256Byte,XRAM 1024Byte, 共1280Byte;

2021/7/1

6

2、使用控制 AUXR (8EH)

单片机内部RAM的扩展

STC单片机内部扩展RAM的应用作者:郭天祥来源:原创更新时间:2008-11-27 21:19:35 浏览次数:5803RAM是用来在程序运行中存放随机变量的数据空间,51单片机默认的内部RAM只有128字节,52单片机增加至256字节,STC89C52增加到512字节,STC89C54、55、58、516等增加到1280字节,对于编程者来说,一个芯片的RAM越多,写起程序来就越容易得心应手,不会总考虑RAM不够用而担心这担心那,连过多的变量都不敢定义。

在前面我们写程序时曾讲到过,如果定义一个变量后,不对这个变量进行初始化,这个变量默认的初值就是0,其实这个结论是需要一定的条件的,在用KEIL编写程序时,总程序中所有变量占用的字节之和小于128字节,并且存储器模式为small模式的前提下,对定义的变量不进行初始化时,编译器会默认将变量值设定为0。

一旦程序中的总变量超过128字节,必须对所有变量进行初始化,否则,没有被初始化的变量默认值将是不确定的。

当变量总和超过128字节时,必须还要在编译器中重新设定存储器的存储模式,存储器模式一共有3种,分别为small、compact和large模式,在KEIL编译器中有选项可进行选择,选项表如图4.4.1所示。

它决定了没有明确指定存储类型的变量、函数参数等数据的默认存储区域。

如果在某些函数中需要使用非默认的存储模式,也可以使用关健字直接说明。

下面对这三种模式分别做介绍。

1. small模式small模式中,所有缺省变量参数均装入单片机内部128字节RAM中,当定义类似如:uchar a; float b;等变量时,这些变量都装入内部128字节RAM中。

使用该模式的优点是访问速度快,缺点是空间有限,而且是对堆栈的空间分配比较少,难以把握,碰到需要递归调用的时候需要小心。

所以这种模式只适用于小程序。

2. compact模式compact模式中,所有缺省变量均位于单片机内部256字节RAM中,和在small模式中使用关健字pdata 来定义变量的效果相同,如:uchar pdata a[100];在该种模式下,程序总变量不得超过256字节,对于只有128字节的单片机,使用此模式定义变量超过128字节时,程序将出错。

stc89c52中EEPROM使用方法

单片机STC89C52RC内部EEPRO M单片机运行时的数据都存在于RAM(随机存储器)中,在掉电后RAM中的数据是无法保留的,那么怎样使数据在掉电后不丢失呢?这就需要使用E EPROM或FLASHR OM 等存储器来实现。

在传统的单片机系统中,一般是在片外扩展存储器,单片机与存储器之间通过II C 或SPI 等接口来进行数据通信。

这样不光会增加开发成本,同时在程序开发上也要花更多的心思。

在STC 单片机中内置了EEPROM(其实是采用ISP/IAP 技术读写内部F LASH 来实现EEPR OM),这样就节省了片外资源,使用起来也更加方便。

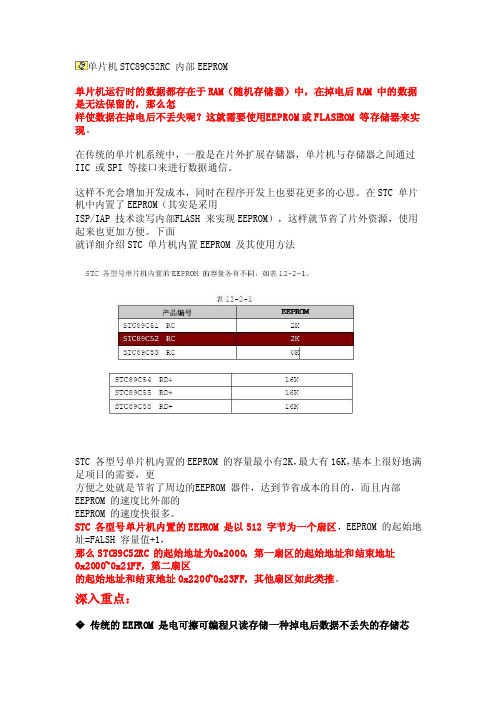

下面就详细介绍ST C 单片机内置EE PROM 及其使用方法STC 各型号单片机内置的EEPR OM 的容量最小有2K,最大有16K,基本上很好地满足项目的需要,更方便之处就是节省了周边的E EPROM器件,达到节省成本的目的,而且内部EEP ROM 的速度比外部的EEPROM的速度快很多。

STC 各型号单片机内置的EEPR OM 是以512 字节为一个扇区,EEPROM的起始地址=FALSH 容量值+1,那么STC89C52RC的起始地址为0x2000,第一扇区的起始地址和结束地址0x2000~0x21FF,第二扇区的起始地址和结束地址0x2200~0x23FF,其他扇区如此类推。

深入重点:�传统的EEPR OM 是电可擦可编程只读存储一种掉电后数据不丢失的存储芯片。

�STC89C52RC 的EEPROM是通过ISP/IAP 技术读写内部F LASH 来实现EEPR OM。

�STC89C52RC 的EEPROM起始地址为0x2000,以512 字节为一个扇区,EERPOM的大小为2K字节。

STC89C52RC 与EEPORM实现的寄存器有6 个,分别是ISP_DATA、ISP_ADD RH、ISP_ADD RLISP_TRI G、ISP_CMD、ISP_CON TR。

第4章-STC89C52单片机硬件结构-PPT

4.3 STC89C52单片机存储器结构

STC89C52RC存储器的结构特点之一是将程序存储器和数据存 储器分开(哈佛结构),并有各自的访问指令。 STC89C52RC系列单片机除可以访问片上Flash存储器外,还 可以访问64KB的外部程序存储器。STC89C52RC系列单片机 内部有512字节的数据存储器,其在物理和逻辑上都分为 两个地址空间:内部RAM(256字节)和内部扩展 RAM(256字节),另外还可以访问在片外扩展的64KB外部 数据存储器。

6. 电源与时钟引脚 (1) VCC:电源正极 (2) Gnd:电源负极,接地 (3) XTAL1:片内振荡器反相放大器和时钟发生器电路输入

端。用片内振荡器时,该脚接外部石英晶体和微调电容。 外接时钟源时,该脚接外部时钟振荡器的信号。 (4) XTAL2:片内振荡器反相放大器的输出端。当使用片内 振荡器,该脚连接外部石英晶体和微调电容。当使用外部 时钟源时,本脚悬空。 RST:复位输入。当输入连续两个机器周期以上高电平时为 有效,用来完成单片机的复位初始化操作。看门狗计时完 成后,RST引脚输出96个晶振周期的高电平。特殊寄存器 AUXR(地址8EH)上的DISRTO位可以使此功能无效。 DISRTO默认状态下,复位高电平为有效。

EA=1时,CPU从片内0000H开始取指令,当PC值没有超出 1FFFH时,只访问片内Flash存储器,当PC值超出1FFFH自动 转向读片外程序存储器空间2000H~FFFFH内的程序。

EA=0时,只能执行片外程序存储器(0000H~FFFFH)中 的程序,不理会片内8KB Flash存储器。

(2)程序存储器某些固定单元用于各中断源中断服务程序入口。

16.封装形式有:LQFP-44、PDIP-40、PLCC-44、PQFP-44。由 于LQFP-44具有体积小、扩展了P4口、外部中断2和3及定 时器T2的功能。PDIP-40的封装与传统的89C52芯片兼容。

郭天祥pdf

跑飞的情况,因此我们也很难人为制造出使单片机程序跑乱的情况,下面的

程序演示利用看门狗的溢出时间来使程序自动复位运行。

【例】:在 TX-1C 实验板上实现如下描述:程序启动后设定看门狗溢

出时间为 2 秒左右,然后点亮第一个发光二极管,稍延时一会,然后熄灭发

光二极管,使程序进入等待死循环状态,并且在死循环中大约每隔 1 秒喂狗

一次,看程序运行是否正常。

新建文件 part3.4.2.c,程序代码如下:

#include <reg52.h>

//52 系列单片机头文件

#define uchar unsigned char

#define uint unsigned int

sfr WDT_CONTR=0xe1;

sbit led1=P1^0;

上图设置存储器模式为 large 模式 其次,为安全起见,当程序中定义多于 128 字节的其它变量时,最好申明为 xdata 型,如 uchar xdata table[100];意思为定义一个 100 个字节容量的数组,将其在扩展 RAM 中分配存储空间。另外 一定要注意,在 large 模式下,编写程序时,定义的变量总数千万不要超过对应单片机的内部最大

倍速与双倍速的设置在下载程序软件界面上有设置选择,大家可自行

下载测试程序运行速度。预分频数的值由 PS2、PS1 和 PS0 的组合确

定,如表 4.2.2 所示。晶振频率即为当前系统的时钟频率。

下面我们通过两个例子来进一步讲解使用看门狗和不使用看门狗时程

序运行的区别,由于 STC 单片机的高抗干扰特点,至今我还未曾遇到过程序

ቤተ መጻሕፍቲ ባይዱRAM 字节数,因为即使超过了,编译器也不会提示错误,但是程序必定会出错。

STC89C52的RAM说明

STC89C52系列单片机RAM说明1、工作寄存器区工作寄存器区位于片内数据存储器中的00H~1FH单元,共32字节,分成四组。

每组8个字节,分别记为R0~R7。

通过配置程序状态字(PSW)中的两个位(RS1,RS0)来决定你所操作的Rn是哪一个区的Rn。

程序默认在工作寄存器A组存放中间运算数据。

当进入中断程序时,中断数据工作寄存器组由组切换到其它区域。

2、可位寻址区可位寻址区位于片内存储器中的20H~2FH区间。

共计16个Byte,128个bit。

每个字节的每个位都拥有单独的地址,即字节地址.位地址,如:SETB 020H.1,就是令020字节的第2个位置位。

3、数据缓冲区(又叫用户RAM区)该区位于片内寄存器的30H~7FH区间。

共计80Byte。

其实整个通用RAM区都拥有同样的寻址规则,因此理论上整个通用RAM区(00H~7FH)都可以算作用户RAM区,只不过,唉,尼玛怎么感觉这么墨迹呢???擦!无力吐槽!4、堆栈其实都不应该单独给丫分个名分,这部分用途根本就是打游击的,哪里有地儿,就往哪钻。

不过基本上它只在80H~FFH这块活动,可以算是和数据缓冲区共用这片区域吧。

5、SFR(特殊用途寄存器)它们是大爷,内部寄存器中的高128个Byte区域内,它们基本就是横行霸道的主。

东一榔头西一棒子的,到处都是占坑不拉屎的节奏。

6、内部RAM残余在片内RAM高字节区被SFR祸害之后剩下的地盘,也可以拿来用用。

7、片外RAM如STC89C52,标称512Byte,那么片内用了256,剩下的256就是这儿了。

说这部分是片外,其实挺冤的,撑死了算是计划外超生的孩子吧,这部分还是在单片机内部,但待遇有点不一样。

首先寻址规则就变了,变成了16位寻址,地址码也成了int格式了。

读写这片区域的内容,需要用MOVX。

STC89C52处理器特点

STC89C52处理器特点概述STC89C52是一款具有强大功能的单片机处理器。

它以其高性能、低功耗和丰富的功能而备受欢迎。

本文将介绍STC89C52处理器的特点和优势。

主要特点以下是STC89C52处理器的主要特点:1. 高性能: STC89C52处理器采用高效的8051内核,具有较高的时钟频率和指令执行能力。

它能够处理复杂的任务并提供快速的响应时间。

2. 丰富的外设接口: STC89C52处理器具有多个通用输入输出口,支持与各种外围设备的连接,如LED、LCD、键盘、数码管等。

这使得它在各种应用领域具有广泛的适用性。

3. 强大的存储能力: STC89C52处理器内部集成了8KB的闪存和2KB的RAM,提供了足够的存储空间来存储程序和数据。

此外,它还支持外部扩展的存储器接口,使得存储容量更加灵活和可扩展。

4. 多种通信接口: STC89C52处理器支持多种通信接口,包括UART、SPI和I2C。

这使得它能够与其他设备进行可靠的数据传输和通信,满足不同应用需求。

5. 低功耗设计: STC89C52处理器采用先进的功率管理技术,能够在低功耗状态下工作,并且具有快速唤醒的能力。

这使得它适合在电池供电的移动设备和节能应用中使用。

6. 安全性和可靠性: STC89C52处理器具有良好的抗干扰和电压波动的能力,能够保护处理器免受外部干扰和异常电压的损害。

它也支持硬件和软件级别的安全机制,确保系统的安全性和可靠性。

总结STC89C52处理器是一款功能强大的单片机处理器,具有高性能、丰富的外设接口、强大的存储能力、多种通信接口、低功耗设计和良好的安全性和可靠性。

它适用于各种应用领域,如工业控制、自动化设备、消费电子和物联网等。

STC89C52单片机的中文介绍

海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料 STC89C51RC / RD+ 系列单片机中文指南 ---高可靠 ---超低价 ---低功耗 ---无法解密STC89C51RC,STC89LE51RCSTC89C52RC,STC89LE52RCSTC89C53RC,STC89LE53RCSTC89C54RD+,STC89LE54RD+STC89C58RD+,STC89LE58RD+STC89C516RD+,STC89LE516RD+附录A: 为什么少数用户的普通8051程序烧录后,不能运行附录B: STC89LE516AD,STC89LE516X2附录C: STC89C51RC / RD+ 系列单片机 ISP (DIY)附录D: ISP Demo(演示版)软件(*.hex)及通信协议附录E: 如何实现运行中自定义下载,无仿真器时方便调试附录F: Keil C51高级语言编程的软件如何减少代码长度国内技术支援:宏晶科技(深圳) www.MCU-Memory.com support@dsp-memory.comUpdate date: 2005-2-16 型 号 最高时钟 频 率HzFlash程序存储器RAM数据存储器降低EMI看门狗双倍速P4口ISPIAPEEPROM数据指针串口UART中断源优先级定时器A/D向下兼容Winbond向下兼容Philips向下兼容Atmel 5V 3VSTC89C51 RC0-80M4K512√√√√√√1K+ 21ch+843W78E51P89C51STC89C52 RC0-80M8K512√√√√√√1K+ 21ch+843W78E52P89C52STC89C53 RC0-80M15K512√√√√√√ 21ch+843W78E54P89C54AT89C55STC89C54 RD+0-80M16K1280√√√√√√8K+ 21ch+843W78E54P89C54AT89C55STC89C58 RD+0-80M32K1280√√√√√√8K+ 21ch+843W78E58P89C58AT89C51RCSTC89C516 RD+0-80M63K1280√√√√√√ 21ch+843W78E516P89C51RD2AT89C51RD2STC89LE51 RC0-80M4K512√√√√√√1K+ 21ch+843W78LE51AT89LV51STC89LE52 RC0-80M8K512√√√√√√1K+ 21ch+843W78LE52AT89LV52STC89LE53 RC0-80M14K512√√√√√√ 21ch+843W78LE54AT89LV55STC89LE54 RD+0-80M16K1280√√√√√√8K+ 21ch+843W78LE54AT89LV55STC89LE58 RD+0-80M32K1280√√√√√√8K+ 21ch+843W78LE58AT89LV51RCSTC89LE516RD+0-80M63K1280√√√√√√ 21ch+843W78LE516P89LV51RD2AT89LV51RD2STC89LE516AD0-90M64K512√√√ 21ch+643√需要A/D转换时才选用,8路8位精度在P1.0 - P1.7口,17 个机器周期一次STC89LE516X20-90M64K512√√√√ 21ch+643√ 本应用技术手册是针对有一定8051系列(MCS-51)单片机编程基础的用户编写的。

stc89C52技术简介

3.2 51单片机部分3.2.1 单片机选型依据MCS-51系列为美国Intel公司在上世纪80年代推出的一种8位单片机。

在芯片的集成程度上有较大提高,同时也大幅提升了性能,单片机的功能也大大丰富,功能单元的数量与种类答复增加,取得巨大成功,如今在我国获得广泛的应用。

MMCS51单片机的内部总体结构其基本特性如下:8位CPU、片内振荡器、4k字节ROM、128字节RAM、21个特殊功能寄存器、32根I/O线、可寻址的64k字节外部数据、程序存贮空间、2个16位定时器、计数器中断结构:具有二个优先级、五个中断源、一个全双工串行口、位寻址(即可寻找某位的内容)功能,适于按位进行逻辑运算的位处理器。

除128字节RAM、4k字节ROM和中断、串行口及定时器模块外,还有4组I/O口P0~P3,余下的就是CPU的全部组成。

把4kROM换为EEPROM就是8751的结构,如去掉ROM/EEPROM 部分即为8031,如果将ROM置换为Flash存贮器或EEPROM,或再省去某些I/O,即可得到51系列的派生品种,如89C51、AT89C2051等单片机。

单片机各部分是通过内部的总线有机地连接起来的。

MCS51单片机的组成如下:运算器以完成二进制的算术/逻辑运算部件ALU为核心,再加上暂存器TMP、累加器ACC、寄存器B、程序状态标志寄存器PSW及布尔处理器。

累加器ACC是一个八位寄存器,它是CPU中工作最频繁的寄存器。

在进行算术、逻辑运算时,累加器ACC往往在运算前暂存一个操作数(如被加数),而运算后又保存其结果(如代数和)。

寄存器B主要用于乘法和除法操作。

标志寄存器PSW也是一个八位寄存器,用来存放运算结果的一些特征,如有无进位、借位等。

其每位的具体含意如下所示:对用户来讲,最关心的是以下四位。

(1)进位标志CY(PSW.7)。

它表示了运算是否有进位(或借位)。

如果操作结果在最高位有进位(加法)或者借位(减法),则该位为1,否则为0[1] 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8.1 系统扩展结构 8.2 地址锁存与地址空间分配 8.3 程序存储器的扩展 8.4 数据存储器的扩展 8.5 EPROM和RAM的综合扩展

8.1 系统扩展结构

为减少连接线,简化组成结构,可把具有共性的连线归并成 一组公共连线,即总线——传送信息的公共通道(BUS)。

STC89C52为减少引脚数量,采用了复用P0口方案,即P0口兼作数据 线和低8位地址线,为了将地址和数据信息区分开来,需要在P0口外 部增加地址锁存器,即将地址信息的低8位锁存后输出。

STC89C52RC的4个并行I/O口,由于系 统扩展的需要,能够真正作为数字I/O使用, 就剩下P1和P3的部分口线了。

STC89C52单片机发出的地址码用于选择某个存储器 单元,在这个过程中单片机必须进行两种选择:一是选 中该存储器芯片,称为“片选”,未被选中的芯片不能 被访问。二是在“片选”的基础上再根据单片机发出的 地址码来对“选中” 芯片的某一单元进行访问,即“单 元选择”。为实现片选,存储器芯片都有片选引脚。同 时也都有多条地址线引脚,以便进行单元选择。注意, “片选”和“单元选择”都是单片机通过地址线一次发 出的地址信号来完成选择的。

I/O口方式(非总线方式 )

例如:MOVX A, @DPTR

I/O口方式——采用片内RAM

(片外RAM 0~0FFFFH) 指令访问外设

例如:MOV A,P0

STC89C52单片机没有专用总线引脚,而是采用了I/O引脚兼

作总线引脚的方案。

STC89C52单片机的存储器扩展即包括程序存储 器扩展又包括数据存储器扩展。AT89S51单片 机采用程序存储器空间和数据存储器空间截然 分开的哈佛结构。扩展后,系统形成了两个并 行的外部存储器空间。

STC89C52单片机属于总线型结构,片内各功能部件都是 按总线关系设计并集成为整体的。

三总线:地址总线(AB) 、数据总线(DB)、控制总线(CB). 单片机系统扩展主要包括存储器扩展和I/O接口部件扩展。

第8章 单片机接口技术

STC89C52单片机与外部设备连接有两种方式:

总线方式

总线方式——采用片外RAM 指令访问外设

(1简.线称选译法-码---一法般)只。适用于外扩少量的片外存储器和

I/O接口芯片。 线选法是指直接利用单片机系统的某一高位地址线

作为存储器芯片(或I/O接口芯片)的“片选”控制信 号。为此,只需要把用到的高位地址线与存储器芯片 的“片选”端直接连接即可。

线选法的优点是电路简单,不需要另外增加地址译 码器硬件电路,体积小,成本低。缺点是可寻址的芯 片数目受到限制,芯片之间地址不连续,地址空间8.2.1 地址锁存

目前,常用的地址锁存器芯片有 74LS373、74HC373,74LS573等。在每个机 器周期,ALE两次有效,可以利用地址锁存 器在ALE的下降沿将P0口输出的地址信息 锁存,当ALE转为低电平时,P0输出8位数 据信息。 1.锁存器74LS373----带有三态输出门的8D触

2.译码法---适合于多芯片扩展.

使用译码器对AT89S51单片机的高位地 址进行译码,译码输出作为存储器芯片的 片选信号。

译码法的优点是能够有效地利用存储器 空间.

常用的译码器芯片有74LS138、 74LS139和74LS154。若全部高位地址线都 参加译码,称为全译码;若仅部分高位地 址线参加译码,称为部分译码。部分译码 存在着部分存储器地址空间相重叠的情况。

是一种带有三 态门的8D锁存器, 功能及内部结构与 74LS373完全一样, 只是其引脚排列与 74LS373不同。与 74LS373相比,

74LS573的输入D端 和输出Q端依次排列 在芯片两侧,为绘

8.2.2 地址空间分配

实际系统设计中,既需要扩展程序存储器,又需要 扩展数据存储器,如何把片外的两个64KB地址空间分配 给各个程序存储器、数据存储器芯片,使一个存储单元 只对应一个地址,避免单片机发出一个地址时,同时访 问两个单元,发生数据冲突。这就是存储器地址空间分 配问题。

• 本书讲解时把单片机系统的地址线笼 统地分为低位地址线和高位地址线,片选 都是使用高位地址线。实际上,16条地址 线中的高、低位地址线的数目并不是固定 的,只是习惯上把用于 “单元选择”的地 址线,都称为低位地址线,其余的为高位 地址线。

常用的存储器地址空间分配方法有两种:

线性选择法(简称线选法)和地址译码法

导通 锁存 隔离

结构:内部由8路D触发器和8个三态缓冲器组成。 原理:/OE端为低电平时,D端信号在 G端正脉冲作用下实

现“接通-锁存-隔离”功能。

74LS373的引脚 373功能表

引脚说明: • D7~D0:8位数据输入线, • Q7~Q0:8位数据输出线。 • G:数据输入锁存选通信号。当

加到该引脚的信号为高电平时, 外部数据选通到内部锁存器,负 跳变时,数据锁存到锁存器中。 • OE:数据输出允许信号,低电平 有效。当该信号为低电平时,三 态门打开,锁存器中数据输出到 数据输出线。当该信号为高电平 时,输出线为高阻态。

当一个选通端为G1为高电平,且另 外两个选通端 G和2A G为2低B 电平时,可 将输入端C、B、A的二进制编码在一个 对应的引脚输出端以低电平译出,其余 引脚输出均为高电平。此时,可将输出 为低电平的引脚作为某一存储器芯片的 片选信号。

数据总线——P0口

地址总线——P0+P2

控制总线——P3口+控制引脚

使用的控制信号如下: PSEN作为外扩程序存储器的 读选通控制信号。

EA

WR和 R为D 外扩数据存储器和 I/O的读、写选通控制信号。 ALE作为P0口发出的低8位地址 锁存控制信号。 EA为片内外程序存储器的选择 控制信号。

373的工作过程: 1、P0口先将低8位地址信号锁 存在373中; 2、373的输出端与输入端(P0 口)隔离;

3、P0口输出8位数据信号+ P2口输出高8位地址信号+ 373输出低8位地址信号 →同时产生16位地址信号+8

位数据信号

STC89C52单片机P0口与74LS373的连接

2.锁存器74LS573