用原理图输入法设计四位全加器实验

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一用原理图输入法设计四位全加器

一实验目的

熟悉利用Quartus II 的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二实验原理

一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout 与相邻的高位加法器的最低进位输入信号cin 相接。而1位全加器可以按照5.4节介绍的方法来完成。

三实验内容

1:完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设计成一个硬件符号入库。键1、键2、键3(PIO0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接sum和cout。

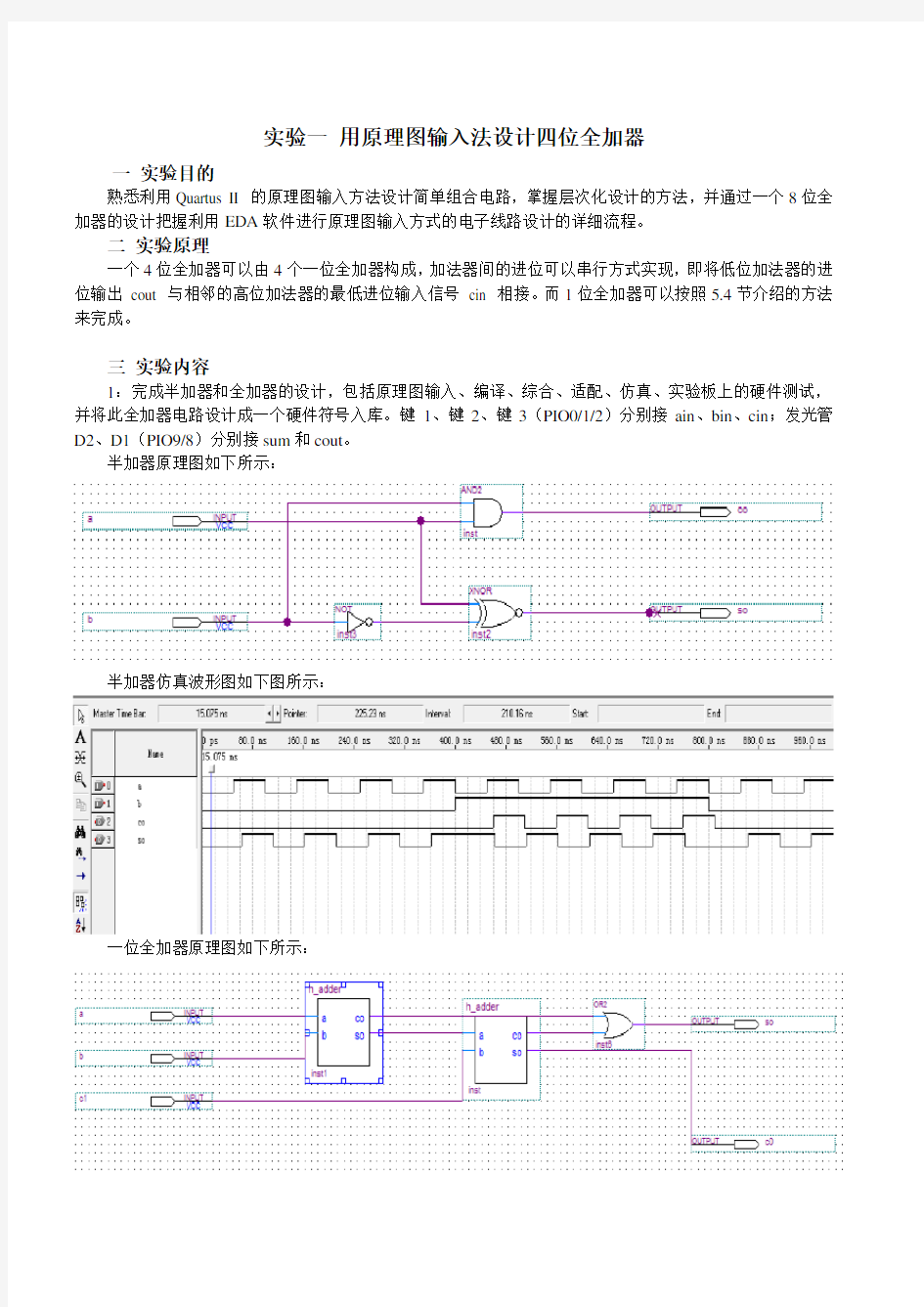

半加器原理图如下所示:

半加器仿真波形图如下图所示:

一位全加器原理图如下所示:

一位全加器仿真波形如下图所示:

2,建立一个更高层次的原理图设计,利用以上获得的1位全加器构成4位全加器,并完成编译、综合、适配、仿真、和硬件测试。建议选择电路模式1(附图F-2):键2、键1输入4位加数:键4、键3输入4位被加数:数码6和数码5显示加和:D8显示进位cout。

四位全加器原理图如下所示:

四位全加器波形图如下所示:

四实验总结

通过本次实验,我掌握了Quartus II 的原理图输入方法设计简单组合电路和层次化设计的方法和详细流程。

(注:文档可能无法思考全面,请浏览后下载,供参考。可复制、编制,期待你的好评与关注)