交换网络32路复用模块设计verilog

基于Verilog HDL的32位分频计数器的设计

分频计数器的基本原理

• 选择合适频率的晶振,然后对其分频,得到 系统需要的时钟频率,再对这一频率时钟进行计 数据。一般的计数器都有输入时钟信号,这里以 晶振的输出时钟作为分频计数据器的输入时钟 CLK。复位信号对各信号进行复位。片选信号用 于选通芯片,以备读写计数值。写信号用于写计 数初始值。读信号用于读取计数值。地址信号 ADDR决定读写计数值的高位还是低位。CLKl为 分频输出的时钟信号。c为输出的进位信号。 DATA为双向数据信号+当系统为分频计数器写 入初始值时是输入,当系统读取计数值时是输出。

基于Verilog HDL的32位分频计 数器的设计

微电子 高翔

Verilog HDL的优点

• Verilog HDL是一种通用的硬件描述语言,易 • 学易用

• Verilog HDL允许在同一个电路模型内进行不 • 同抽象层次的描述

• Verilog HDL 绝大多数流行的综合工具都支持

• 所有的制造厂商都提供用于Verilog HDL综合 • 之后的逻辑仿真的元件库

原理图

实现功能综合

程序仿真

总结

• 首先本文介绍了硬件描述语言的发展状况,并对国内发展 提出了建议,然后对本

• 文要用的硬件语言VerilogHDL进行了详细介绍,并对仿真 所用的软件进行了介

•

绍。

• 其次介绍了32位分频器计数器的原理,并介绍了其它的 分频器,讨论了优缺点,

• 并且详细介绍了本文所用的分频计数器的原理和介绍、分 析。

HDL语言的发展。基于Verilog HDL的优越性,IEEE于

基于Verilog设计的双向32位移位寄存器

双向移位寄存器摘要:系统使用EDA技术设计了具有移位功能的寄存器,采用硬件描述语言VHDL进行设计,然后进行编程,时序仿真。

软件基于Verilog语言实现了双向32位移位寄存器的控制功能。

通过本设计熟悉QuartusII环境下的硬件描述操作流程,掌握基本的Verilog语法与编写风格。

关键字:EDA;Verilog;32位双向移位寄存器1.引言随着社会的发展,科学技术也在不断的进步。

特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。

近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为EDA服务;(2)硬件电路与软件设计过程已高度渗透;(3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;(4)数字系统的芯片化实现手段已成主流。

因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言VHDL对32位双向移位寄存器进行编程实现。

2.课程设计的目的在计算机中常要求寄存器有移位功能。

如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。

因此,移位寄存器的设计是必要的。

本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课程设计更加深入的了解移位寄存器的功能。

了解EDA技术,并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关知识理论联系实际,掌握所学的课程知识。

通过对移位寄存器的设计,巩固和综合运用所学知识,提高对计算机组成原理的理解。

verilog多路红外时分复用通信例程 -回复

verilog多路红外时分复用通信例程-回复实现多路红外时分复用通信是一个非常有趣和实用的课题。

在这篇文章中,我将详细介绍如何使用Verilog编程语言来实现多路红外时分复用通信的例程。

请跟随我的步骤一步一步回答。

首先,让我们来了解一下什么是红外时分复用通信。

红外时分复用通信是一种使用红外线作为载体,在不同的时间片段上分别传输不同的数据信号的通信方法。

它通过在不同时间段上分别发送和接收不同的红外信号,实现了多路通信的目的。

在Verilog中,我们可以使用逻辑门电路来实现多路红外时分复用通信。

下面是一个基本的多路红外时分复用通信的Verilog例程:module infrared_comm(input clk, 时钟信号input reset, 复位信号input [3:0] data_in, 输入数据信号output reg [3:0] data_out 输出数据信号);reg [1:0] state; 状态寄存器reg [3:0] data_mux; 数据选择器always @(posedge clk) beginif(reset) begin 复位state <= 0;data_out <= 0;end else begincase(state)0: begin 默认状态data_out <= 0;state <= 1;end1: begin 切换状态data_mux <= data_in;state <= 2;end2: begin 发送状态data_out <= data_mux;state <= 0;enddefault: state <= 0; 默认状态endcaseendendendmodule以上Verilog代码实现了一个简单的多路红外时分复用通信的例程。

让我来逐步解释一下每个部分的功能。

首先,我们定义了一个模块`infrared_comm`,其中包含了输入和输出的端口。

verilog组合电路的设计 -回复

verilog组合电路的设计-回复Verilog组合电路的设计:引言在现代电子系统中,组合电路起着至关重要的作用。

组合电路由逻辑门和其他逻辑元件组成,没有存储元件,其输出仅取决于当前的输入。

这种特点使得组合电路非常适合用于解决各种问题,例如数据选择、逻辑运算、状态机、编码器和解码器等。

本文将介绍关于Verilog组合电路设计的基础知识,并提供一步一步的解决方案,以帮助读者更好地理解和应用这些概念。

第1步:了解Verilog HDL(硬件描述语言)Verilog HDL是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它提供了一种便捷的方法来设计和模拟数字逻辑电路。

在开始设计之前,我们需要对Verilog HDL有基本的了解。

首先,我们需要了解几个基本概念:- 模块:Verilog中的模块是组合电路的一个基本单位。

模块由端口声明和内部逻辑实现组成。

- 端口声明:端口声明定义了模块的输入和输出端口的类型和名称。

- 内部逻辑:内部逻辑定义了模块的功能,它由组合逻辑和时序逻辑组成。

第2步:编写模块的端口声明在设计组合电路之前,我们需要先确定模块的输入和输出端口。

在这个例子中,我们将以[4位全加器]为主题进行设计。

首先,我们需要定义4个输入端口a、b、cin和一个输出端口sum,同时还有一个进位输出端口cout。

根据这些要求,我们可以编写以下端口声明:module full_adder(a, b, cin, sum, cout);input a, b, cin;output sum, cout;endmodule第3步:实现内部逻辑接下来,我们需要实现全加器的内部逻辑。

全加器是一种用于将两个二进制数字和一个进位输入相加的电路。

首先,我们需要声明一个临时变量temp,用于存储每个位上的和以及进位的计算结果。

然后,我们可以分别计算每个位上的和以及进位,最后将结果赋给输出端口sum和cout。

以下是全加器的完整代码:module full_adder(a, b, cin, sum, cout);input a, b, cin;output sum, cout;wire temp;assign sum = a ^ b ^ cin;assign temp = (a & b) (a & cin) (b & cin);assign cout = temp;endmodule第4步:设计主模块我们已经成功定义并实现了全加器模块。

verilog !用法 -回复

verilog !用法-回复Verilog 是硬件描述语言(Hardware Description Language, HDL) 的一种,主要用于描述数字系统的行为和结构。

它是一种高级语言,可用于描述电子系统的硬件功能和电路行为。

Verilog 具有模块化和并行化的特性,能够快速且准确地描述电子系统及其各个组件之间的相互关系。

本文将以"Verilog 用法" 为主题,为读者逐步介绍Verilog 的基础知识和常见用法。

第一部分:Verilog 简介和基础知识(500 字)1. 什么是Verilog?Verilog 是一种硬件描述语言,用于描述数字系统的行为和结构。

它是一种高级语言,能够准确描述电子系统的硬件功能和电路行为。

2. Verilog 的起源和发展最早的Verilog 是在1984 年由Gateway Design Automation 公司的Philip Moorby 发明的。

之后,它被开放出来,并逐渐成为数字系统设计的行业标准。

3. Verilog 的基本元素Verilog 包含模块(module)、端口(port)、信号(signal)、寄存器(register)、线网(wire)、输入(input)、输出(output)、内部连接(assign)等基本元素,这些元素共同构成了一个完整的Verilog 描述。

4. Verilog 的行为建模Verilog 提供了多种行为建模的方式,包括组合逻辑(combinational)、时序逻辑(sequential)、有限状态机(finite state machine)等,使得设计者能够准确地描述电子系统的行为和时序。

第二部分:Verilog 模块和端口定义(500 字)1. Verilog 模块的定义Verilog 中的模块是一个独立的功能单元,它可以包含多个输入输出端口和内部信号,用于描述一个子系统的功能。

模块内部可以包含连接和互连逻辑,以及寄存器等具体的硬件描述。

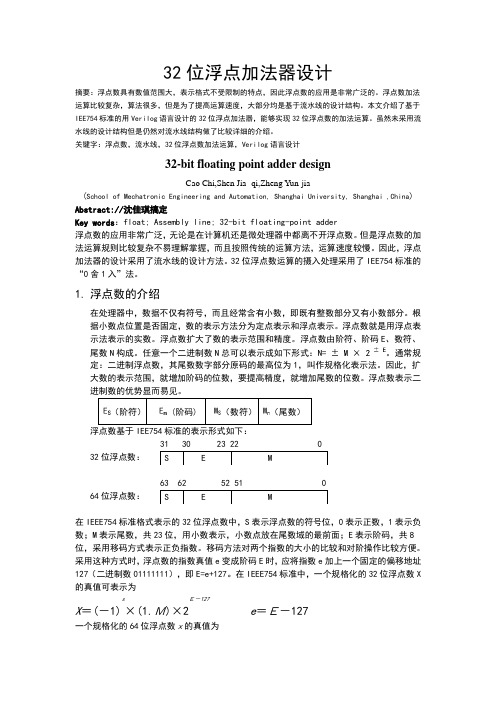

上海大学verilog设计32位浮点加法器设计

32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的。

浮点数加法运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构。

本文介绍了基于IEE754标准的用Verilog 语言设计的32位浮点加法器,能够实现32位浮点数的加法运算。

虽然未采用流水线的设计结构但是仍然对流水线结构做了比较详细的介绍。

关键字:浮点数,流水线,32位浮点数加法运算,Verilog 语言设计32-bit floating point adder designCao Chi,Shen Jia- qi,Zheng Yun-jia(School of Mechatronic Engineering and Automation, Shanghai University, Shanghai ,China ) Abstract://沈佳琪搞定Key words :float; Assembly line; 32-bit floating-point adder 浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数。

但是浮点数的加法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢。

因此,浮点加法器的设计采用了流水线的设计方法。

32位浮点数运算的摄入处理采用了IEE754标准的“0舍1入”法。

1. 浮点数的介绍在处理器中,数据不仅有符号,而且经常含有小数,即既有整数部分又有小数部分。

根据小数点位置是否固定,数的表示方法分为定点表示和浮点表示。

浮点数就是用浮点表示法表示的实数。

浮点数扩大了数的表示范围和精度。

浮点数由阶符、阶码E 、数符、尾数N 构成。

任意一个二进制数N 总可以表示成如下形式:N=。

通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法。

因此,扩大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数。

《Verilog设计入门》PPT课件

精选PPT

18

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句

两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。

对于always引导的块语句中含有多条阻塞式赋值语句时,当执行某 一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精选PPT

23

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式

精选PPT

24

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句 if(表达式) begin 语句1;语句2;…..语句n; end else begin 语句n+1;语句n+2;…..语句n+n; end

input a,b;

output so,co;

assign so = a ^ b;

assign co = a & b;

endmodule

精选PPT

28

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述

2.基于always @引导的过程语句和逻辑操作符的描述

module h_adder2(a,b,so,co);

endmodule

精选PPT

34

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 5. 全加器描述----用半加器、或门模块及例化语句描述

精选PPT

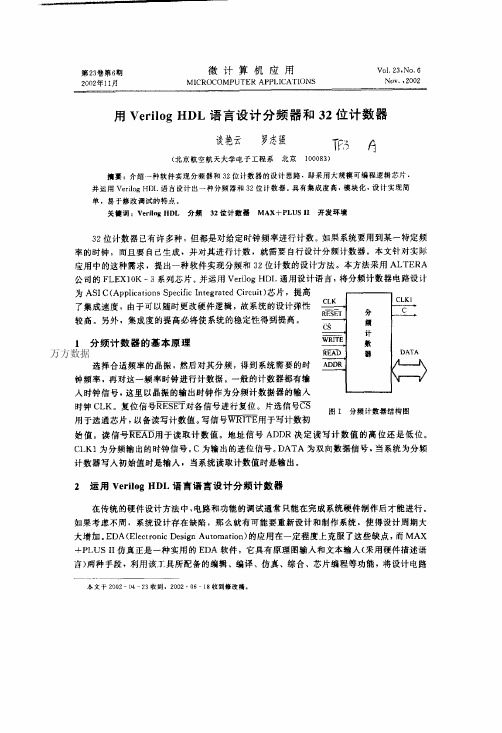

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学

ASIC课程设计报告二

学号:201222240937 姓名:周恒

课题题目:交换网络32路复用模块设计

2013年5月

题目要求

Develop, verify (before and after synthesis), and synthesize a Verilog module that encapsulates the functionality shown in Fig.2, where the outputs of the A/D converters are inputs to a module that interleaves the sample bytes, with separate sub-modules for the control unit, the mux, the demux, the parallel to serial converter, and the serial to parallel converter. Define additional interface signals as needed to complete the design. Model the multiplexer so that its outputs will be registered. Carefully document your work.

图1-2 一个简单的交换控制系统组成

本次设计的主要内容为交换网络复用与解复用模块,在下文做出详细设计,包括设计规格书、设计框图、仿真波形和设计结论。

一、设计框图

整个系统由5个模块组成,其顶层模块如下图所示:

1.控制模块:用于对整个系统的控制,包括复用控制,串并转换控制,并

串转换控制和解复用控制。

2.复用模块:对32路输入数据进行复用,依次输入系统。

3.并串转换模块:将8bit的并行数据转换为串行数据。

4.串并转换模块:将对应的串行数据转换为并行数据。

5.解复用模块:对32路数据进行复用输出,依次输出系统。

系统框图顶层图

复用模块:对32路输入数据进行复用,依次输入系统,其原理框图部分截图如下图所示。

复用模块原理框图部分截图

并串转换模块:将8bit的并行数据转换为串行数据其原理框图如下图所示。

并串转换模块原理框图

串并转换模块:将对应的串行数据转换为并行数据,其原理框图如图下图所示。

串并转换模块原理框图

解复用模块:对32路数据进行复用输出,依次输出系统,其原理框图部分截图如下图所示。

解复用模块原理框图部分截图

二、仿真波形

通过testbench模块产生测试输入,将各个模块添加到顶层图中联合测试,最终实现所需要的功能。

tesebench说明:

测试输入为d_in[255:0]表示输入的32路8位数据。

第一个125us传输的32路数据分别为16进制的01,02,03......, (20)

第二组为21,22,23......,3e, (40)

……

……

产生的仿真波形如下图所示:

输入波形为:

第一组32路输入数据

第二组32路输入数据

第三组32路输入数据

输出波形如下:

设计总结

通过仿真表面各个模块完成了相应的功能,输入数据帧以125us为周期传到输出,实现了课程设计的要求。