组合逻辑电路的分析与设计方法 ppt课件

合集下载

组合逻辑电路的分析和设计PPT课件

(3) 列函数表达式

F2 m(1,2) d(3,5,6,7) F1 m(1,4) d(3,5,6,7)

第35页/共228页

F2 m(1,2) d(3,5,6,7) F1 m(1,4) d(3,5,6,7)

(4) 逻辑函数的化简

a. 化简F2

BC

A 00 01 11 10

0

1 1

种不同的编码器,如二进制编码器、优先编码器和 8421BCD编码器等。 1. 二进制编码器

用n位二进制代码对N=2n个一般信号进行编码 的电路,叫做二进制编码器。 二进制编码器也称之为2n –n线二进制编码器。

第42页/共228页

(1) 二进制编码器的主要特点

任何时刻只允许输入一个有效信号,不允许同时出现 两个或两个以上的有效信号,因而其输入是一组有约束(互 相排斥)的变量。

第22页/共228页

⑵ 写出逻辑函数表达式

由真值表写出逻辑函数表达式。

⑶ 对逻辑函数式进行化简和变换 根据选用的逻辑门的类型,将函数式化简或变换

为最简式。选用的逻辑门不同,化简的形式也不同。 ⑷ 画出逻辑电路图

根据化简后的逻辑函数式,画出门级逻辑电路图。 在实际数字电路设计中,还须选择器件型号。

第23页/共228页

& B

& B

L CA CB

L CA CB

若用集成门实现与或式,至少需要两种类型的门电路。

若用集成门实现与非式,则仅需要一种类型的门电路。

第29页/共228页

[例7] 试用与或非门设计一个操作码形成器,如图所 示。当按下*、+、-各个操作键时,要求分别产生乘 法、加法和减法的操作码01、10和11。

2. 组合逻辑电路的主要特点 a. 电路中就不包含记忆性元器件; b. 而且输出与输入之间没有反馈连线; c. 门电路是组合电路的基本单元。 d. 输出与电路原来状态无关。

【全文】组合逻辑电路ppt

列出真值表

W A BD BC A BD BC X BC BD BCD BC BD BCD Y CD CD CD CD ZD

ABCD WXYZ ABCD WXYZ

0000 0001 0010 0011 0100

0011 0100 0101 0110 0111

0101 0110 0111 1000 1001

4、功能评述

1. 写出输出函数表达式

根据逻辑电路图写输出函数表达式时,一般从输入端开始 往输出端逐级推导,直至得到所有与输入变量相关的输出函数 表达式为止。

即:

输入

输出

2、 化简输出函数表达式 目得:① 简单、清晰地反映输入与输出之间得逻辑关系; ② 简化电路结构,获得最佳经济技术指标。

3、 列出输出函数真值表 真值表详尽地给出了输入、输出取值关系,能直观地

半加器已被加工成小规模集成电路, 其逻辑符号如右图所示。

思考:可用 何种芯片实现?

例3 分析下图所示组合逻辑电路,已知输入为8421码, 说明该电路功能。

解 写出该电路输出函数表达式

W A BD BC A BD BC X BC BD BCD BC BD BCD Y CD CD CD CD ZD

设:被加数、加数及来自低位得“进位”分别用变量Ai、Bi 及Ci-1表示,相加产生得“与”及“进位”用Si与Ci表示。

设:被加数、加数及来自低位得“进位”分别用变量Ai、Bi 及Ci-1表示,相加产生得“与”及“进位”用Si与Ci表示。

根据二进制加法运算法则可列出全加器得真值表如下表

所示。

Ai Bi Ci-1

1000 1001 1010 1011 1100

功能: 8421码转换成余3码!

4、3 组合逻辑电路设计

第三章组合逻辑电路ppt课件

图3.3.1 3位二进制普通编码器框图 《数字电子技术》

3.3 若干常用中规模组合逻辑电路 表3-3-1 3位二进制普通编码器真值表

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

由于普通编码器在任何时刻 I0 ~ I7 当中仅有一个 取值为1,即只有真值表中所列的8种状态,而且它

的( 28 8 )种状态均为约束项。因此,由真值表

A

&

1

F2

C

B

&

C

图3.2.1 【例1】逻辑电路图

《数字电子技术》

3.2 组合逻辑电路的分析和设计方法

§3.2.2 组合逻辑电路的设计方法

所谓“设计”:即根据给出的实际逻辑问题,求出实 现这个逻辑功能的最简逻辑电路。

所谓“最简”:是指所用器件最少,器件种类最少, 而且器件之间的连线也最少。

一、设计步骤 (1)进行逻辑抽象

【例1】试用两片74LS148接成16线-4线优先编码器,

将-的优11先11权’最1低6个。146位个二低进A电0A制平1~5代输A码1入5 ,信其号中

编为‘0000

的A优0 先权最高,

接成的电路图如图3.3.4所示:

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

图3.3.4 用两片74LS148接成的16线-4线优先编码器逻辑图

I7

)

S

Y0 (I1I2 I4 I6 I3 I4 I6 I5 I6 I7 ) S

(由功能表第一行体现)。

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

(2)YS 为选通输出端,其表达式为:

YS I0 I1 I2 I3 I4 I5 I6 I7 S

此式表明:只有当所有的编码输入端均为高 电平(即没有编码输入),且S=1( S 0 )

3.3 若干常用中规模组合逻辑电路 表3-3-1 3位二进制普通编码器真值表

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

由于普通编码器在任何时刻 I0 ~ I7 当中仅有一个 取值为1,即只有真值表中所列的8种状态,而且它

的( 28 8 )种状态均为约束项。因此,由真值表

A

&

1

F2

C

B

&

C

图3.2.1 【例1】逻辑电路图

《数字电子技术》

3.2 组合逻辑电路的分析和设计方法

§3.2.2 组合逻辑电路的设计方法

所谓“设计”:即根据给出的实际逻辑问题,求出实 现这个逻辑功能的最简逻辑电路。

所谓“最简”:是指所用器件最少,器件种类最少, 而且器件之间的连线也最少。

一、设计步骤 (1)进行逻辑抽象

【例1】试用两片74LS148接成16线-4线优先编码器,

将-的优11先11权’最1低6个。146位个二低进A电0A制平1~5代输A码1入5 ,信其号中

编为‘0000

的A优0 先权最高,

接成的电路图如图3.3.4所示:

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

图3.3.4 用两片74LS148接成的16线-4线优先编码器逻辑图

I7

)

S

Y0 (I1I2 I4 I6 I3 I4 I6 I5 I6 I7 ) S

(由功能表第一行体现)。

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

(2)YS 为选通输出端,其表达式为:

YS I0 I1 I2 I3 I4 I5 I6 I7 S

此式表明:只有当所有的编码输入端均为高 电平(即没有编码输入),且S=1( S 0 )

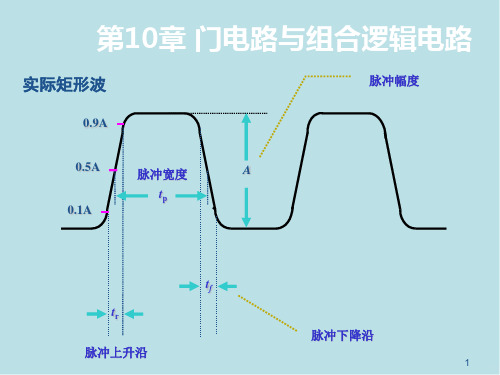

电路与电子技术第10章-组合逻辑电路课件.ppt

33

第10章 门电路与组合逻辑电路

(1) 逻辑表达式 用与、或、非等运算和括号来描述逻辑函数的表达式

如: Y A(B C) D

输出变量: Y

输入变量: A、B、C

反变量: 字母上有非号, 如: D

原变量: 字母上没有非号, 如: A、B、C

34

第10章 门电路与组合逻辑电路

(2) 逻辑状态表

0•A=0 A•0=0 1•A=A

A•1 =A A•A=A

A• A 0

0+A=A

A+0=A

1+A=1

1=0

非 0=1

运 算

0=0

1=1

A A

A+1 =1 A+A =A

A A1 29

第10章 门电路与组合逻辑电路

3. 逻辑代数运算定律 交换律: A + B = B + A

A•B =B•A

结合律: ABC = (AB) C =A (BC)

T5

A、B 有一个为 0 或都为 0 时:

T1 发射结导通, T1 集电结和 T2 、T5 均截止 复合管 T3 、T4 导通,Y 为 1

21

第10章 门电路与组合逻辑电路

常用 TTL 集成与非门 74LS00

74LS00 有 4 个两输入与非门,完全相同

Y AB

A、B 为输入端 Y 为输出端 4 个与非门电源公共 第 14 脚接 + 5V 直流电源 第 7 脚接电源的地

(2) 配项法

应用 B B( A A)

[例] Y AB AC BC AB AC BC( A A) AB AC ABC ABC

AB(1 C ) AC(1 B) AB AC

第10章 门电路与组合逻辑电路

(1) 逻辑表达式 用与、或、非等运算和括号来描述逻辑函数的表达式

如: Y A(B C) D

输出变量: Y

输入变量: A、B、C

反变量: 字母上有非号, 如: D

原变量: 字母上没有非号, 如: A、B、C

34

第10章 门电路与组合逻辑电路

(2) 逻辑状态表

0•A=0 A•0=0 1•A=A

A•1 =A A•A=A

A• A 0

0+A=A

A+0=A

1+A=1

1=0

非 0=1

运 算

0=0

1=1

A A

A+1 =1 A+A =A

A A1 29

第10章 门电路与组合逻辑电路

3. 逻辑代数运算定律 交换律: A + B = B + A

A•B =B•A

结合律: ABC = (AB) C =A (BC)

T5

A、B 有一个为 0 或都为 0 时:

T1 发射结导通, T1 集电结和 T2 、T5 均截止 复合管 T3 、T4 导通,Y 为 1

21

第10章 门电路与组合逻辑电路

常用 TTL 集成与非门 74LS00

74LS00 有 4 个两输入与非门,完全相同

Y AB

A、B 为输入端 Y 为输出端 4 个与非门电源公共 第 14 脚接 + 5V 直流电源 第 7 脚接电源的地

(2) 配项法

应用 B B( A A)

[例] Y AB AC BC AB AC BC( A A) AB AC ABC ABC

AB(1 C ) AC(1 B) AB AC

数字电子技术基础组合逻辑电路ppt课件

通常数据分配器有一根输入线,n根地址控制线,2n根数据输出线,因此根据输出线的个数也称为2n路数据分配器

用74LS138译码器实现的数据分配器

译码器的三个输入端A2 、A1 、A0作为选择通道用的地址信号输入,八个输出端作为数据输出通道,三个控制端接法如下:

74HC4511引脚图

74HC4511是常用的CMOS七段显示译码器, A3、A2、 A1、A0为输入端,输入8421BCD码,a~g为七段输出,输出高电平有效,可用来驱动共阴极LED数码管。

为测试输入端,低电平有效,当

时a~g输出全为1,用于检查译码器和LED

数码管是否能正常工作。

数据时,可强制将不需要显示的位消去。如四位数码管,某时刻只需显示最低的两位数据,则可以让最高两位数据的

例2

用74LS138实现逻辑函数

。

解:

将函数表达式写成最小项之和

将输入变量A、B、C分别接入输入端,注意高位和低位的接法,使能端接有效电平,由于74LS138输出为反码输出,需要再将F变换一下:

逻辑电路图

注意:使用中规模集成译码器实现逻辑函数时,译码器的输入端个数要和逻辑函数变量的个数相同,并且需要将逻辑函数化成最小项表达式。

3.2.2 组合逻辑电路的设计方法

根据给定的逻辑功能要求,设计出能实现这 个功能要求的逻辑电路。

实现的电路要最简,即所用器件品种最少、数量最少、连线最少。

要求:

(1)根据设计要求确定输入输出变量并逻辑赋 写出真值表。

(2)由真值表写出逻辑函数表达式并化简或转换。

(3)选用合适的器件画出逻辑图。

2.二-十进制译码器

常用的有8421BCD码集成译码器74HC42,

第3单元组合逻辑电路的分析与设计PPT课件

本单元学习指导

➢ 各种组合逻辑电路在功能上千差万别,但其分 析方法和设计方法都是共同的。掌握了一般的分析方 法,可得知任何给定电路逻辑功能;掌握基本的设计 方法,就可据已知的实际要求设计获得相应的逻辑电 路。

21

实验三 组合逻辑电路设计之 密码锁、8线-3线编码器

一.实验目的

➢1.掌握组合逻辑电路的设计方法。 ➢2.用实验验证设计电路的逻辑功能。 ➢3.掌握编码的概述,为后继内容做准备。

设三人的意见为变量A、B、C,表决结果 为函数L。对变量及函数进行如下状态赋值: 对于变量A、B、C,设同意为逻辑“1”; 不同意为逻辑“0”。对于函数L,设事情

通过为逻辑“1”;没通过为逻辑“0”。

真值表

14

(2)由真值表写出逻辑表达式:

LA B CAB CAC BABC

(3)化简.

LABC ABCAC BABC A(B CC)BC (AA)A(CBB) AB BC AC

15

(4)画出逻辑图 .

如果要求用与非门实现该逻辑电路,就应将表达式转换成与非—与 非表达式: LA B B C A C ABC AC

画出逻辑图如图所示。

16

(2)列逻辑真值表。由于每一时刻只有一个 输入端,所以输入组合只有8组,而不用列28 次输出组合。

17

2.组合逻辑电路设计举例

例3.16 : 设计一个8输入3输出的二进制编码电 路,即8-3线编码器。要求,每一时刻只有一 个输入键接通高电平,即为“1”,当不同的输 入键为“1”时,会有一个对应二进制码输出。

(4)简述其逻辑功能。

A、B表示两个1位 二进制的加数,S 是它们相加的本位 和,C是向高位的 进位。这种电路可 用于实现两个1位 二进制数的相加, 它是运算器中的基 本单元电路,称为 半加器。

35-组合逻辑电路的分析与设计PPT模板

电工电子技术

组合逻辑电路的分析与设计

1.1 组合逻辑电路的分析方法

1.组合逻辑电路的特点

组合逻辑电路是数字电路中最简单的一类逻辑电路。其特 点是:任何时刻的输出只与该时刻的输入状态有关,而与先 前的输入状态无关,也就是说组合逻辑电路不具备记忆功能, 结构上无反馈。

2.组合逻辑电路的分析方法

所谓组合逻辑电路的分析,是对给定组合逻辑电路进行 逻辑分析,求出其相应的输入、输出逻辑关系表达式,确定 其逻辑功能。

(5)画出逻辑图,如右图所示。

电工电子技术

由真值表可知,当A、B、C三个变量不一致时,输出为 1,所以这个电路称为“不一致电路”。

1.2 组合逻辑电路的分析方法

组合逻辑电路的设计是组合逻辑电路分析的逆过程, 即已知逻辑功能要求,设计出具体的实现该功能的组合逻辑 电路。其设计步骤如下。

(1)分析逻辑问题,明确输入量与输出量; (2)根据逻辑要求列出相应的真值表;

(3)根据真值表写出逻辑函数的最小项表达式; (4)化简逻辑函数,并根据可能提供的逻辑电路类型写 出所需的表达式形式; (5)画出与表达式相应的逻辑图。

组合逻辑电路的设计一般应以电路简单、所用器件最 少为目标,并尽量减少所用集成器件的种类。

【例14-2】设计一个三人表决电路,表决结果按“少数 服从多数”的原则决定。

【解】(1)分析具体问题,确定输入量与输出量。设三 人的意见为变量A、B、C,表决结果为函数Y,并设同意为逻 辑1,不同意为逻辑0,事情通过为逻辑1,没通过为逻辑0。

(2)根据逻辑要求列出真值表。

(3)由真值表写出逻辑表达பைடு நூலகம்。

Y ABC ABC ABC ABC

(4)化简逻辑函数。画该逻辑函数的卡诺图,并合并最 小项,如左图所示,得最简与或表达式:Y=AB+BC+AC。

组合逻辑电路的分析与设计

1.1 组合逻辑电路的分析方法

1.组合逻辑电路的特点

组合逻辑电路是数字电路中最简单的一类逻辑电路。其特 点是:任何时刻的输出只与该时刻的输入状态有关,而与先 前的输入状态无关,也就是说组合逻辑电路不具备记忆功能, 结构上无反馈。

2.组合逻辑电路的分析方法

所谓组合逻辑电路的分析,是对给定组合逻辑电路进行 逻辑分析,求出其相应的输入、输出逻辑关系表达式,确定 其逻辑功能。

(5)画出逻辑图,如右图所示。

电工电子技术

由真值表可知,当A、B、C三个变量不一致时,输出为 1,所以这个电路称为“不一致电路”。

1.2 组合逻辑电路的分析方法

组合逻辑电路的设计是组合逻辑电路分析的逆过程, 即已知逻辑功能要求,设计出具体的实现该功能的组合逻辑 电路。其设计步骤如下。

(1)分析逻辑问题,明确输入量与输出量; (2)根据逻辑要求列出相应的真值表;

(3)根据真值表写出逻辑函数的最小项表达式; (4)化简逻辑函数,并根据可能提供的逻辑电路类型写 出所需的表达式形式; (5)画出与表达式相应的逻辑图。

组合逻辑电路的设计一般应以电路简单、所用器件最 少为目标,并尽量减少所用集成器件的种类。

【例14-2】设计一个三人表决电路,表决结果按“少数 服从多数”的原则决定。

【解】(1)分析具体问题,确定输入量与输出量。设三 人的意见为变量A、B、C,表决结果为函数Y,并设同意为逻 辑1,不同意为逻辑0,事情通过为逻辑1,没通过为逻辑0。

(2)根据逻辑要求列出真值表。

(3)由真值表写出逻辑表达பைடு நூலகம்。

Y ABC ABC ABC ABC

(4)化简逻辑函数。画该逻辑函数的卡诺图,并合并最 小项,如左图所示,得最简与或表达式:Y=AB+BC+AC。

第四章组合逻辑电路的分析与设计PPT课件

≥1

Ci

Ai Bi

∑

Si

Ci-1

CI

CO

Ci

=1

Si

14

二、多位数加法器

4位串行进位加法器

C3 S3

S2

S1

S0

Ci Si ∑

Ai Bi Ci-1

Ci Si ∑

Ai Bi Ci-1

Ci Si ∑

Ai Bi Ci-1

Ci Si ∑

Ai Bi Ci-1

A3 B3 C2

A2 B2 C1

A1 B1 C0

A0 B0 C-1

2n≥N

16

二.优先编码器——允许同时输入两个以上信号,并按优先级输出。 集成优先编码器举例——74148(8线-3线)

注意:该电路为反码输出。EI为使能输入端(低电平有效),EO为使能 输出端(高电平有效) ,GS为优先编码工作标志(低电平有效)。

17

EO

GS

A0

A1

A2

≥1

≥1

≥1

≥1

&

&

&

C i A iB iC i 1 A iB iC i 1 A iB iC i 1 A iB iC i 1

A iB i(A i B i)C i- 1

13

S i Ai Bi Ci1

C i A iB i(A i B i)C i -1

根据逻辑表达式画出全加器的逻辑电路图:

Ai Bi

Ci -1

&

=1

串行进位加法器,电路简单,但运算速度慢。 为此产生了超前进位加法器,详见P109。

15

4.3.2 编码器

一.编码器的基本概念及工作原理 编码——将特定的逻辑信号编为一组二进制代码。 能够实现编码功能的逻辑部件称为编码器。 一般而言,N个不同的信号,至少需要n位二 进制数编码。 N和n之间满足下列关系:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子电路

课题 组合逻辑电路的分析与设计

教学科研处:张瑜

1

组合逻辑电路的分析与设计 ◆课 题 纲 要

➢组合逻辑电路的特点 ➢组合逻辑电路的分析 ➢组合逻辑电路的设计

2

预备知识的复习

➢ 描述逻辑电路逻辑功能的主要方法:

逻辑表达式

真值表

卡诺图

逻辑图

➢各种表示法之间的相互转换?

逻辑图

逻辑表达式

真值表

,使之在上楼前,用楼

下开关打开电灯,上楼

c)列出真值表。

后,用楼上开关关灭电

2.根据真值表,写出输出逻辑函数表达式灯楼;上或开者关在打下开楼电前灯,,用下

或画其卡诺图 3.对输出逻辑函数进行化简与变换

楼后,用楼下开关关灭 电灯

化为最简与或式、然后变换为适当的形式。 4.根据最简输出逻辑函数式,画逻辑图

&

&L

&

思考作业题:

设计一个举重裁判表决器。设举重有三个裁判 ,一个主裁判和两个副裁判。杠铃的完全举起 由每一裁判按一下自己前面的按钮来确定。只 有当两个裁判(其中必须有主裁判)判明成功 ,表示成功的灯才亮。

19

小结

理解组合电路的特点 掌握组合电路的分析方法 掌握组合电路的设计方法 在许多情况下,如果用中、大规模集成电路来实现 组合函数,可以取得事半功倍的效果。

记忆功能的元件或电路,无反馈通路。

每一个输出变量是全部或部分

输入变量的函数:

L1=f1(A1、A2、…、Ai) L2=f2(A1、A2、…、Ai)

……

Lj=fj(A1、A2、…、Ai)

4

二、组合逻辑电路的分析

A

&

B

&

C

&

Y &

分析目的:逻辑电路 逻辑功能。

5

分析举例:

例1:分析下图的逻辑功能:

A

已知逻辑 电路图

逻辑表达式

最简表达式

列真值表

说明功能

练习:试分析下图的逻辑功能

8

练习过程

试分析下图的逻辑功能

Z2

解:①求逻辑表达式

Z1 AB

Z1 Z3

Z2 AAB Z3 BAB

SZ2Z3Z2Z3

AABBAB(AB)AB ②列真值表:

(AB)(AB)ABAB

AB

A B CS

0 0 00

CZ1 AB

逻辑图

出从

B

逐输

1 级入

写到

出输

C

逻辑表 达式

2

化 简

最简与或 表达式

Y1 AB

Y2 BC

Y3 CA

Y1

&

Y2

&

Y3

&

Y

Y &

1

YY1Y2Y3ABBCAC

2

分析举例:

最简与或 表达式

3

真值表

4

电路的逻 辑功能

YA B B C CA

3

ABC 000 001 010 011 100 101 110 111

用功能模块(MSI)设计的原则: (1)功能模块个数少,品种也少。

(2)功能模块之间连线少。

10

三、组合逻辑电路的设计方法

设计的一般步骤(与分析相反):

1.逻辑抽象

实例:设计一个楼上、

a)分析因果关系:确定输入、输出变量。 楼下开关的控制逻辑电

路来控制楼梯上的路灯

b)定义逻辑状态:确定0,1的意义。

Y

0

0

0

4

1

0 1

1

1

当输入A、B、 C中有2个或3 个为1时,输 出Y为1,否 则输出Y为0。 所以这个电路 实际上是一种 3人表决用的 组合电路: 3人表决电路

7

小结

分析组合逻辑电路的一般方法:

1.由前到后逐级写出各逻辑门输出端的逻辑表达式。 2.化简逻辑表达式为最简与或表达式。 3.列真表。 4.由真值表,分析逻辑功能。

真值表

逻辑表达式

逻辑图

组合逻辑电路的分析与设计本质就是各种表示法之间的相互转换

3

一、组合逻辑电路的特点

功能特点:电路任一时刻的输出状态只决定于该时 刻

各输入状态的组合,而与电路的原状态无关(即无记忆功 能)。

例:表决控制电路、楼梯灯控制电路、加法电路、数值比较电路、编\译

码器、多路选择器等等。

结构特点:组合电路就是由门电路组合而成,电路中无

1

解:设楼上开关为A,楼下开关为B,灯泡为Y。

并设A、B闭合时为1,断开时为0;灯亮时Y为1, 灯灭时Y为0。根据逻辑要求列出真值表

0

真值表

1

1

0

2

2

逻辑表达式

3

化简或变换 后的表达式

4

逻辑电路图

YABAB

用与非 门实现

3

YABAB

4

思考:用4个与 非门能否实现 该电路?

A

Y

B

13

能: 分析如下:

(变换表达式)

A

&

&

&Y

&

B

注意:设计结果的不唯一性,及工程设计与

理论分析的差异

14

15

电子表决器

告别举手表决:人大代表在人民大会堂进行电子表决

设计练习

试设计一个三人表决逻辑电路,要求: 三人A、B、C各 控制一个按键,按下为“1”,不按为“0”。多数 (2)按下为通过。通过时L=1,不通过L=0。用与 非门实现。

+5V

A

B

要设计

的逻辑

L

C

电路

设计过程

解:

2、用卡诺图化简写出最简式

1、列真值表

1

ABC L

00 0 0 00 1 0

111

AC BC

A B

0 1 0 0 L= AC + BC + AB = AB • AC • BC

0 1 1 1 3、画逻辑图

A

&

10 0 0

B

10 1 1

C

11 0 1 11 1 1

0 1 01

③逻辑功能:半加器

1 0 01

9

1 1 10

三、组合逻辑电路的设计方法来自设计目的根据给定的逻辑功能要求,设计出用尽可

能少的逻辑门来实现该逻辑功能的电路。

设计组合逻辑电路的原则

用门电路(SSI)设计的原则:

(1)所用门的个数尽量少,而且各门的输入端数目 也尽量少。

(2)尽量减少所用集成器件(门)的种类

20

作业:

①教材:P96----题4 ②思考练习题:设计一个举重裁判表决器。设举重有三个裁 判,一个主裁判和两个副裁判。杠铃的完全举起由每一裁判 按一下自己前面的按钮来确定。只有当两个裁判(其中必须 有主裁判)判明成功,表示成功的灯才亮。试设计该电路。

21

谢 谢!

22

实际逻 辑问题

真值表

逻辑表达式

最简或合 理表达式

逻辑图

11

设计举例

电路功 能描述

1 逻 辑 抽 象

实例:设计一个楼上、楼下开关的控制逻辑电路来

控制楼梯上的路灯,使之在上楼前,用楼下开关打 开电灯,上楼后,用楼上开关关灭电灯;或者在下 楼前,用楼上开关打开电灯,下楼后,用楼下开关 关灭电灯。(要求用与非门实现电路)

课题 组合逻辑电路的分析与设计

教学科研处:张瑜

1

组合逻辑电路的分析与设计 ◆课 题 纲 要

➢组合逻辑电路的特点 ➢组合逻辑电路的分析 ➢组合逻辑电路的设计

2

预备知识的复习

➢ 描述逻辑电路逻辑功能的主要方法:

逻辑表达式

真值表

卡诺图

逻辑图

➢各种表示法之间的相互转换?

逻辑图

逻辑表达式

真值表

,使之在上楼前,用楼

下开关打开电灯,上楼

c)列出真值表。

后,用楼上开关关灭电

2.根据真值表,写出输出逻辑函数表达式灯楼;上或开者关在打下开楼电前灯,,用下

或画其卡诺图 3.对输出逻辑函数进行化简与变换

楼后,用楼下开关关灭 电灯

化为最简与或式、然后变换为适当的形式。 4.根据最简输出逻辑函数式,画逻辑图

&

&L

&

思考作业题:

设计一个举重裁判表决器。设举重有三个裁判 ,一个主裁判和两个副裁判。杠铃的完全举起 由每一裁判按一下自己前面的按钮来确定。只 有当两个裁判(其中必须有主裁判)判明成功 ,表示成功的灯才亮。

19

小结

理解组合电路的特点 掌握组合电路的分析方法 掌握组合电路的设计方法 在许多情况下,如果用中、大规模集成电路来实现 组合函数,可以取得事半功倍的效果。

记忆功能的元件或电路,无反馈通路。

每一个输出变量是全部或部分

输入变量的函数:

L1=f1(A1、A2、…、Ai) L2=f2(A1、A2、…、Ai)

……

Lj=fj(A1、A2、…、Ai)

4

二、组合逻辑电路的分析

A

&

B

&

C

&

Y &

分析目的:逻辑电路 逻辑功能。

5

分析举例:

例1:分析下图的逻辑功能:

A

已知逻辑 电路图

逻辑表达式

最简表达式

列真值表

说明功能

练习:试分析下图的逻辑功能

8

练习过程

试分析下图的逻辑功能

Z2

解:①求逻辑表达式

Z1 AB

Z1 Z3

Z2 AAB Z3 BAB

SZ2Z3Z2Z3

AABBAB(AB)AB ②列真值表:

(AB)(AB)ABAB

AB

A B CS

0 0 00

CZ1 AB

逻辑图

出从

B

逐输

1 级入

写到

出输

C

逻辑表 达式

2

化 简

最简与或 表达式

Y1 AB

Y2 BC

Y3 CA

Y1

&

Y2

&

Y3

&

Y

Y &

1

YY1Y2Y3ABBCAC

2

分析举例:

最简与或 表达式

3

真值表

4

电路的逻 辑功能

YA B B C CA

3

ABC 000 001 010 011 100 101 110 111

用功能模块(MSI)设计的原则: (1)功能模块个数少,品种也少。

(2)功能模块之间连线少。

10

三、组合逻辑电路的设计方法

设计的一般步骤(与分析相反):

1.逻辑抽象

实例:设计一个楼上、

a)分析因果关系:确定输入、输出变量。 楼下开关的控制逻辑电

路来控制楼梯上的路灯

b)定义逻辑状态:确定0,1的意义。

Y

0

0

0

4

1

0 1

1

1

当输入A、B、 C中有2个或3 个为1时,输 出Y为1,否 则输出Y为0。 所以这个电路 实际上是一种 3人表决用的 组合电路: 3人表决电路

7

小结

分析组合逻辑电路的一般方法:

1.由前到后逐级写出各逻辑门输出端的逻辑表达式。 2.化简逻辑表达式为最简与或表达式。 3.列真表。 4.由真值表,分析逻辑功能。

真值表

逻辑表达式

逻辑图

组合逻辑电路的分析与设计本质就是各种表示法之间的相互转换

3

一、组合逻辑电路的特点

功能特点:电路任一时刻的输出状态只决定于该时 刻

各输入状态的组合,而与电路的原状态无关(即无记忆功 能)。

例:表决控制电路、楼梯灯控制电路、加法电路、数值比较电路、编\译

码器、多路选择器等等。

结构特点:组合电路就是由门电路组合而成,电路中无

1

解:设楼上开关为A,楼下开关为B,灯泡为Y。

并设A、B闭合时为1,断开时为0;灯亮时Y为1, 灯灭时Y为0。根据逻辑要求列出真值表

0

真值表

1

1

0

2

2

逻辑表达式

3

化简或变换 后的表达式

4

逻辑电路图

YABAB

用与非 门实现

3

YABAB

4

思考:用4个与 非门能否实现 该电路?

A

Y

B

13

能: 分析如下:

(变换表达式)

A

&

&

&Y

&

B

注意:设计结果的不唯一性,及工程设计与

理论分析的差异

14

15

电子表决器

告别举手表决:人大代表在人民大会堂进行电子表决

设计练习

试设计一个三人表决逻辑电路,要求: 三人A、B、C各 控制一个按键,按下为“1”,不按为“0”。多数 (2)按下为通过。通过时L=1,不通过L=0。用与 非门实现。

+5V

A

B

要设计

的逻辑

L

C

电路

设计过程

解:

2、用卡诺图化简写出最简式

1、列真值表

1

ABC L

00 0 0 00 1 0

111

AC BC

A B

0 1 0 0 L= AC + BC + AB = AB • AC • BC

0 1 1 1 3、画逻辑图

A

&

10 0 0

B

10 1 1

C

11 0 1 11 1 1

0 1 01

③逻辑功能:半加器

1 0 01

9

1 1 10

三、组合逻辑电路的设计方法来自设计目的根据给定的逻辑功能要求,设计出用尽可

能少的逻辑门来实现该逻辑功能的电路。

设计组合逻辑电路的原则

用门电路(SSI)设计的原则:

(1)所用门的个数尽量少,而且各门的输入端数目 也尽量少。

(2)尽量减少所用集成器件(门)的种类

20

作业:

①教材:P96----题4 ②思考练习题:设计一个举重裁判表决器。设举重有三个裁 判,一个主裁判和两个副裁判。杠铃的完全举起由每一裁判 按一下自己前面的按钮来确定。只有当两个裁判(其中必须 有主裁判)判明成功,表示成功的灯才亮。试设计该电路。

21

谢 谢!

22

实际逻 辑问题

真值表

逻辑表达式

最简或合 理表达式

逻辑图

11

设计举例

电路功 能描述

1 逻 辑 抽 象

实例:设计一个楼上、楼下开关的控制逻辑电路来

控制楼梯上的路灯,使之在上楼前,用楼下开关打 开电灯,上楼后,用楼上开关关灭电灯;或者在下 楼前,用楼上开关打开电灯,下楼后,用楼下开关 关灭电灯。(要求用与非门实现电路)