微电子工艺(3)----第三章外延

微电子工艺(3)外延

而外延生长速率正相反。

外延速率的影响因素(三)

反应剂浓度对生长 速率的影响

SiCl4摩尔浓度 大于0.27出现 腐蚀现象

SiCl4浓度与生长速率的关系

速率、温度对结晶类型的影响

-1

3.2.4 外延层中的杂质分布

掺杂采用原位气相掺杂。 杂质掺入效率依赖于:生长 温度、生长速率、气流中掺 杂剂相对于硅源的摩尔数、 反应室几何形状,掺杂剂自 身特性。 有杂质再分布现象

3.2.5 设备

立式和桶式外延装置示意图

气相外延设备

3.2.6 外延方法

低压外延 选择外延 SOI技术

低压外延low-pressure epitaxy

目的:减小自掺杂效应 压力:1*103—2*104Pa 原因: 低压气体扩散速率快,衬底逸出杂质可快速穿过边界层 (滞留层),被排除反应室,重新进入外延层机会减小; 停止外延时,气体易清除,多层外延时缩小了过渡区, 温度影响 压力降低,生长外延层温度下限也降低; 问题:易泄漏;基座与衬底间温差大;基座、反应室在减压 时放出吸附气体;外延生长温度低等-----外延层晶体完整性 受到一定影响

选择外延(Selective epitaxial growth,SEG)

•如何实现? 根据硅在绝缘体上很难核化成膜的特性,在硅表面的特 定区域生长外延层而其它区域不生长的技术。 外延生长晶粒成核速度 SiO2〈Si3N4〈Si •Cl或HCl作用: 利用氧化物表面的高清洁性和源中存在足够的Cl或HCl提高 原子的活动性,以抑制气相中和掩蔽层表面处成核;Cl↑,选 择性↑,因为HCl可将在氧化物表面形成的小团的硅刻蚀掉; •三种类型: 1.以Si为衬底,以SiO2或Si3N4为掩膜,在暴露的硅窗口内 生长外延;或在暴露的硅窗口内生长外延,在掩膜生长PolySi; 2.同样以Si为衬底,以SiO2或Si3N4为掩膜,在暴露的硅衬 底上刻图形,再生长外延; 3.沟槽处外延生长

外延抑制自掺杂技术简介

毕业论文简介外延抑制自掺杂技术研究应用物理2班 08510233 伏瑜指导老师:王青 ( 教授) 杜金生 (工程师)摘要外延层杂质浓度是影响电学性能的重要参数,外延掺杂存在有意识掺杂和无意识掺杂(即自掺杂),自掺杂影响外延生长。

自掺杂降低了衬底/外延界面过渡区的陡峭程度,同时也增加了外延淀积过程中的本底浓度。

不但对外延层的电阻率控制带来相当大的困难,使外延层界面处杂质分布梯度变缓,外延层有效厚度减薄,PN结击穿电压的显著降低,晶体管的大电流特性变坏,特别不利于要求薄而界面处杂质分布陡的外延层的微波器件的制造。

而且一些有害杂质的存在,还会使噪声增加等。

本文对外延淀积过程中自掺杂的产生进行了分析,提出了在外延淀积过程中可以通过改变压力、温度、及采用HCl腐蚀抛光技术、背封技术、H2烘烤赶气技术、二步外延技术等方法来解决外延自掺杂,从而改善器件的特性参数。

关键词:外延淀积自掺杂AbstractThe impurity concentration is a key parameter which has an effect on the electrical performance of the device in the epitaxy, the doping of epitaxy exists conscious and unconscious doping (i.e, self-doping), the growth of epitaxy is influenced by self-doping. Since the self-doping reduced the steep degree of substrate and the epitaxy interface of transition region, also increased background concentration in the process of the extension. It makes the control of the epitaxy,s resistivity difficult, the epitaxy of the interface between layer impurities distribution gradient slow, the epitaxy of effective thickness thin, the breakdown voltage of PN junction significantly reduce, and the current characteristics of transistor change bad, especially to the disadvantage of manufacturing microwave devices ,which were required thin and the distribution of the impurities were steep in the interface. And the existence of some harmful impurities, still can make noise up, etc.This paper analised the generation of self-doping during the epitaxial deposition , some techniques such as altering press, temperature,HCl rot, back-seal, H2expel,and two-step epitaxy, are proposed to improve the electrical charateristics of the device by reducing self-doping effect during epitaxial deposition.Key words:Epitaxy; Deposition;Self-doping;第一章外延技术概述1、概念所谓外延就是在一定的条件下,在单晶衬底上,沿原来的结晶方向生长一层导电类型、电阻率、厚度和晶格结构、完整性等都符合要求的新单晶层的工艺过程。

微电子工艺概论1-5

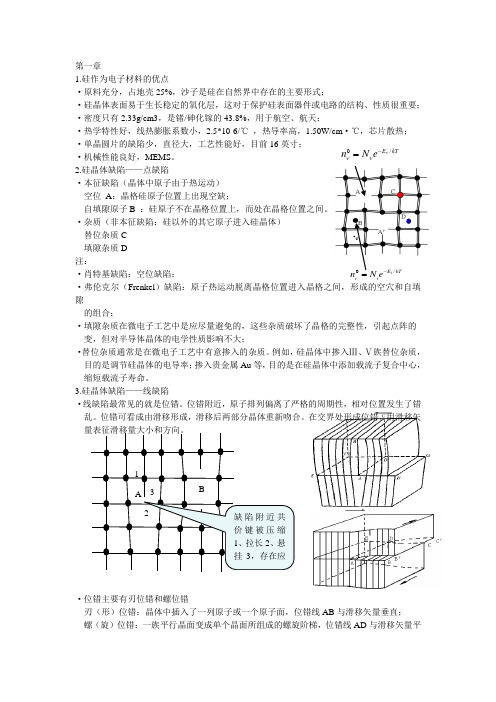

1.硅作为电子材料的优点·原料充分,占地壳25%,沙子是硅在自然界中存在的主要形式;·硅晶体表面易于生长稳定的氧化层,这对于保护硅表面器件或电路的结构、性质很重要; ·密度只有2.33g/cm3,是锗/砷化镓的43.8%,用于航空、航天;·热学特性好,线热膨胀系数小,2.5*10-6/℃ ,热导率高,1.50W/cm ·℃,芯片散热; ·单晶圆片的缺陷少,直径大,工艺性能好,目前16英寸;·机械性能良好,MEMS 。

2.硅晶体缺陷——点缺陷·本征缺陷(晶体中原子由于热运动) 空位 A :晶格硅原子位置上出现空缺;自填隙原子B :硅原子不在晶格位置上,而处在晶格位置之间。

·杂质(非本征缺陷:硅以外的其它原子进入硅晶体) 替位杂质C 填隙杂质D 注:·肖特基缺陷:空位缺陷; ·弗伦克尔(Frenkel )缺陷:原子热运动脱离晶格位置进入晶格之间,形成的空穴和自填隙的组合;·填隙杂质在微电子工艺中是应尽量避免的,这些杂质破坏了晶格的完整性,引起点阵的 变,但对半导体晶体的电学性质影响不大; ·替位杂质通常是在微电子工艺中有意掺入的杂质。

例如,硅晶体中掺入Ⅲ、Ⅴ族替位杂质, 目的是调节硅晶体的电导率;掺入贵金属Au 等,目的是在硅晶体中添加载流子复合中心, 缩短载流子寿命。

3.硅晶体缺陷——线缺陷·线缺陷最常见的就是位错。

位错附近,原子排列偏离了严格的周期性,相对位置发生了错 乱。

位错可看成由滑移形成,滑移后两部分晶体重新吻合。

在交界处形成位错。

用滑移矢量表征滑移量大小和方向。

·位错主要有刃位错和螺位错刃(形)位错:晶体中插入了一列原子或一个原子面,位错线AB与滑移矢量垂直; 螺(旋)位错:一族平行晶面变成单个晶面所组成的螺旋阶梯,位错线AD 与滑移矢量平kT E v v e N n /0-=νkTE i i i e N n /0-=1 23 BA 缺陷附近共价键被压缩1、拉长2、悬挂3,存在应力·刃形位错的两种运动方式:滑移和攀移。

外延工艺

2012-3-7

25

软误差

从封装材料中辐射出的α粒子进入衬 底产生大量(约106量级)电子-空穴对, 在低掺杂MOS衬底中,电子-空穴对 可以扩散50μm,易受电场作用进入 有源区,引起器件误动作,这就是 软误差。 采用低阻衬底上外延高阻层的外延片, 则电子-空穴对先进入衬底低阻层,其扩 散长度仅1μm,易被复合,它使软误差 率减少到原来的1/10。

2012-3-7 12

三. 外延中的掺杂

掺杂剂有: 1.氢化物: PH3,AsH3,BBr3,B2H6 POCl3,AsCl3 2. 氯化物:

2012-3-7 13

在外延层的电阻率还会受到下 列三种因素的干扰

重掺杂衬底中的大量杂质通过热扩散方 式进入外延层,称为杂质外扩散。 衬底中的杂质因挥发等而进入气流,然 后重新返回外延层,称为气相自掺杂。 气源或外延系统中的污染杂质进入外延, 称为系统污染。

2012-3-7 23

外延层和衬底中不同类型的掺杂形成的 p--n结,它不是通过杂质补偿作用形成的, 其杂质分布可接近理想的突变结。

2012-3-7

24

外延改善NMOS存储器电路特性

(1)提高器件的抗软误差能力 (2)采用低阻上外延高阻层,可降低源、 漏n+ 区耗尽层寄生电容,并提高器件对 衬底中杂散电荷噪声的抗扰度 (3)硅外延片可提供比体硅高的载流子寿 命,使半导体存储器的电荷保持性能提 高。

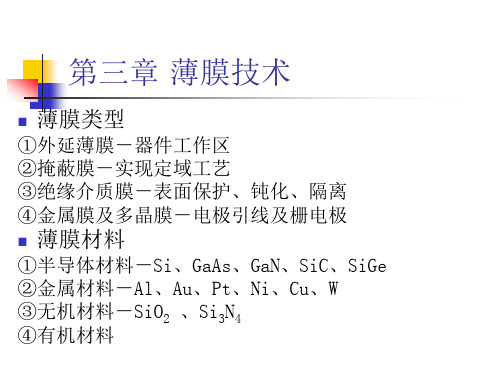

【2024版】微电子工艺之薄膜技术

二、外延掺杂及杂质再分布

3.杂质再分布

再分布:外延层中的杂质向衬底扩散;

衬底中的杂质向外延层扩散。

总杂质浓度分布:各自扩散的共同结果。

①衬底杂质的再分布(图3-21)

初始条件:N2(x,0)=Nsub,x<0; N2(x,0)=0,x>0; 边界条件一:衬底深处杂质浓度均匀,即

当vt» D1t 时,有

N1x,t

Nf 2

erfc

2

x D1t

二、外延掺杂及杂质再分布

当vt»2 D1t 时,有

N1(x,t)≈Nf

③总的杂质分布(图3-24)

N(x,t)=N1(x,t)± N2(x,t) “+”: 同一导电类型;

“-”:相反导电类型;

三、自掺杂(非故意掺杂)

1.定义

N 2 x

x 0

二、外延掺杂及杂质再分布

边Jd界条D件2 二Nx:2 在xx外f 延J层b 表J s面 (h2x=vxfN)2 ,扩x f 散,t 流密度Jd为

解得:

N2x,t

N sub 2

erfc

2

x D2 t

v h2 2h2

v

ex

p

D2

vt

x erfc

2vt x 2 D2t

①当hG» ks,则 NGS≈NG0,V= ks(NT/ NSi) Y,是表面反 应控制。

②当ks» hG,则 NGS ≈0, V= hG(NT/ NSi) Y,是质量转 移控制。

二、外延掺杂及杂质再分布

1. 掺杂原理-以SiH4-H2-PH3为例

外延工艺简介

THANKS

感谢观看

物理气相沉积

利用物理方法使气态物质冷凝或蒸发沉积在基底 上。

3

外延生长速率与成核密度

外延生长速率与成核密度之间存在关联。

液相外延生长技术

溶液生长

01

将基底浸泡在含有源材料的溶液中,通过扩散控制反应过程。

热壁外延生长

02

将基底靠近加热的壁,使源材料蒸发并在基底上沉积。

外延层厚度和均匀性

03

液相外延生长过程中,需要控制外延层厚度和均匀性。

外延材料种类及特性

单晶硅外延片

单晶硅外延片是一种常见的外延材料,具有高导热、高绝缘、高 透光等特性,广泛应用于电力电子、微电子等领域。

氮化镓(GaN)外延片

GaN外延片具有高击穿电压、高热导率、高抗辐射能力等特性,在 高频大功率电子器件领域具有广泛应用。

氧化锌(ZnO)外延片

ZnO外延片具有高电子迁移率、高透明度、低介电常数等优点,在 光电器件和压电器件领域有重要应用。

这类设备采用水平管式结构,具有生长速度快、温度分布均匀、薄膜质量高等优点,适用 于生长高质量的外延层。

垂直管外延设备

采用垂直管式结构,具有生长环境稳定、操作简单、易于维护等特点,适合生长多种材料 的外延层。

金属有机物化学气相沉积(MOCVD)

MOCVD设备具有灵活的化学气相沉积能力,能够在较低温度下生长高质量的外延层,同 时具有高生产效率和低成本等优点。

随着科技的不断发展,外延工艺的应用领域越来越广 泛。例如,在新能源领域,外延工艺可以用于制备太 阳能电池、燃料电池等高效能源转换器件;在生物医 学领域,外延工艺可以用于制备生物芯片、生物传感 器等生物医学器件;在环保领域,外延工艺可以用于 制备光催化材料、空气净化器等环保器件。未来,随 着外延工艺的不断进步和完善,其应用领域将不断拓 展,为人类社会的发展带来更多的机遇和挑战。

微电子器件(3-3)

均匀基区相关知识点I pEI pCI prI nEI nr相关公式β∗W B2 τb =1− =1− 2 2 LB τBD EW B N B WBρE γ = 1− D W N = 1− W ρ B E E E B⎛ W B2 α =⎜ ⎜1 − 2 L2 B ⎝2 B 2 BR口E = 1− R口B1⎞⎛ R口E ⎞ W B2 R口E ⎟ ⎟⎜ ⎟ ≈ 1 − 2 L2 − R ⎜1 − R ⎟ 口 B1 ⎠ B 口 B1 ⎠⎝⎛W R口E ⎜ β ≈⎜ + R口B1 ⎝ 2L⎞ ⎟ ⎟ ⎠−1§3-3 缓变基区晶体管的放大系数以NPN 管为例,结电压为 VBE 与 VBC 。

现代晶体管,如双扩散外延平面管 属缓变基区晶体管,由于载流子在 基区主要是以漂移运动在传输,故 它又称为 漂移晶体管。

N+0PN杂质浓度分布图:x jE x jCWB = x jC − x jEN E ( x) N B ( x)NC0x jE x jCx1、基区内建电场的形成与求解 形成的物理机理(以P型基区的Xmb-Xjc段为例)xjE 和xjC为发射结 和集电结结深, xmB为杂质补偿后 基区净杂质浓度 的极值位置杂质浓度高的地方留下不 可移动的电离杂质电荷 (NA-),杂质浓度低的地 方积累多子(空穴)杂质(NA) 浓度梯度杂质电离多子(空 穴) 浓度梯度多子(空 穴) 扩散正负电荷 分离内建电场内建电场的作用 漂移晶体管电场方向:指向发射结 加速场 电场作用: 基区的少子(电子) 向集电结方向漂移运 动,对少子有加速作用 向发射结方向漂移运动, 抵消多子扩散运动 多子电流等于零基区的多子(空穴)xjE到xmB段,将产生一个与EB方向相反的自建电场EB’,它将阻止 基区中少子(电子)流向集电结,称阻滞电场,该部分基区称阻 滞区。

一般情况下,相对与整个基区而言,阻滞区很窄,一般可以忽略。

请从以下几方面总结半导体器件中的内建电场① 掺杂不均匀产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响? ② 大注入产生的内建电场 ~ 产生机理? 对多数载流子运动的影响? 对少数载流子运动的影响 ? ③ p-n结中的内建电场 ~ 产生机理? 势垒区(阻挡层)→阻挡多数载流子还是阻挡少数载流子? 耗尽层近似?→ 耗尽什么种类的载流子?三个内建电场形成机理的比较内建电场种类形成原因 P区与N区刚接触 时冶金结两边存 在自由载流子浓 度差 大注入时中性区 多子具有浓度梯 度分布电荷分离的表现形式 冶金结两边自由载流子扩散,留下不 可移动的电离施主和受主杂质电荷在 空间上分离 多子与少子同时扩散,但由于多子扩 散得不到补充,最终使得靠近耗尽区 少子浓度高于多子浓度,远离耗尽区 边界少子浓度低于多子浓度,最终多 子与少子电荷在空间上分离 多子浓度扩散,使得靠近发射结耗尽 区的电离杂质电荷高于多子,靠近集 电结耗尽区的电离杂质电荷低于多 子,造成电离杂质电荷与多子电荷在 空间上分离作用 载流子的扩散运 动等于漂移运动PN结空间电 荷区内建电 场 大注入PN结 中性区中的 内建电场 (自建场) 缓变基区BJT 中基区内建 电场多子的扩散运动 与漂移运动抵 消,加强少子扩 散运动 多子的扩散运动与 漂移运动抵消,少 子在基区以漂移运 动为主掺杂原子具有浓 度梯度,多子具 有相同的浓度梯 度分布基区内建电场表达式的推导 设基区杂质浓度分布为:NB (0)NB (x)⎛ ηx ⎞ N B ( x ) = N B ( 0 ) exp ⎜ ⎜− W ⎟ ⎟ B ⎠ ⎝ 式中 η 是表征基区内杂质变化程度的一个参数:NB (WB )0WBxN B (W B ) = N B ( 0 ) exp (− η )N B (0) η = ln N B (W B )当 η = 0 时为均匀基区。

集成电路工艺__热氧化薄膜技术

3.2 热生长二氧化硅薄膜

一般湿氧氧化是由携带气体通过水浴后,含有水 汽的氧气进入石英管对硅片进行氧化,而水汽 的多少由水浴的温度控制,同时水浴的质量也 将影响氧化层质量的好坏。 一种新的湿氧氧化方法,它是依靠高纯的氢气和 氧气在石英管中按比例混合燃烧成水,氢和氧 的比例为2:1 时为水汽氧化,小于这比例为湿 氧氧化,当氢气为零时,为干氧氧化。

7-9

5-6

3.2 热生长二氧化硅薄膜

二氧化硅层的主要用途 二氧化硅对杂质有掩蔽扩散作用,能实现选择性 定域扩散掺杂 器件表面的保护和电路的钝化膜 器件的电隔离(绝缘)作用 电容的介电材料 作MOS 管的绝缘栅材料 多层互连的层间绝缘介质 缓冲层/热氧化层

3.2 热生长二氧化硅薄膜

1.扩散时的掩蔽层,离子注入的(有时与光刻胶、 Si3N4层一起使用)阻挡层

a.最小击穿电场(非本征)--针孔、裂缝、杂质。

b. 最大击穿电场(本征)--厚度、导热、界面态电荷等;氧 化层越薄、氧化温度越高, 击穿电场越低。 c.介电常数3~4(3.9)

3.2 热生长二氧化硅薄膜

不同方法制备的SiO2薄膜的物理参数

氧化方法 密度(g/cm3) 折射率λ=546nm 电阻率(Ωcm) 介电常数 介电强度 (108V/cm)

SiO2 +4HF SiF4 2H 2O SiF4 +2HF H 2SiF6

六氟化硅溶于水。利用这一性质作为掩蔽膜,微电子工艺中利用 HF光刻出IC 制造中的各种窗口。 SiO2的腐蚀速率与HF的浓度、温度、 SiO2的质量以及所含杂质 数量等因素有关。不同方法制备的SiO2 ,腐蚀速率可能相差很 大。

3.1 概述

二、用于制备薄膜的材料种类繁多,例如:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C Ce ( x) s 2

自掺杂效应

高温外延时,高掺杂衬底杂质 反扩散(蒸发)到气相粘滞层 (边界层),再进入外延层的 现象。 自掺杂效应是气相外延的本征 效应,不可能完全避免。

3.2.6 外延方法

低压外延 选择外延 SOI技术

低压外延

目的:减小自掺杂效应 压力:1*103—2*104Pa 原因: 低压气体扩散速率快,衬底逸出杂质可快速穿过边界层(滞留 层),被排除反应室,重新进入外延层机会减小; 停止外延时,气体易清除,多层外延时缩小了过渡区,冷壁系统 和热基座间无涡流,改善ρ;减小外延层图形的漂移和畸变; 温度影响 压力降低,生长外延层温度下限也降低,T↑,G↑; 问题:易泄漏;基座与衬底间温差大;基座、反应室在减压时放 出吸附气体;外延生长温度低等-----外延层晶体完整性受到一定 影响

微电子工艺

第3章 外延

(Epitaxy)

田

丽

第3章 外延

3.1 概述 3.2 气相外延 3.3 分子束外延 3.4 其它外延 3.5 外延层缺陷及检测

3.1 概述

3.1.1外延概念

在微电子工艺中,外延(epitaxy)是指在单晶 衬底上,用物理的或化学的方法,按衬底晶 向排列(生长)单晶膜的工艺过程。 新排列的晶体称为外延层,有外延层的硅片 称为(硅)外延片。 与先前描述的单晶生长不同在于外延生长温 度低于熔点许多 外延是在晶体上生长晶体,生长出的晶体的 晶向与衬底晶向相同,掺杂类型、电阻率可 不同。n/n+,n/p,GaAs/Si。

扩散效应 自掺杂效应

扩散效应

扩散效应也叫互(或外) 扩散,指在 衬底中的杂质与外延层中的杂质在 外延生长时互相扩散,引起衬底与 外延层界面附近的杂质浓度缓慢变 化的现象。 若杂质扩散速率远小于外延生长速 率,衬底中的杂质向外延层中扩散, + +对应n/n (p/p+) 或外延层中杂质向衬底中的扩散, 都如同在半无限大的固体中的扩散。 +(n/p+) -对应p/n 当衬底和外延层都掺杂时,外延层 中最终杂质分布

晶格失配 lattice mismatch 失配率

aa f 100% ' a

'

其中:a外延层晶格参数; a′衬底晶格参数。 有热膨胀失配系数和晶格常数失配率。

热失配影响 单晶薄膜物 理和电学性 质

晶格失配导致 外延膜中缺陷 密度非常高

特点

外延生长时掺入杂质的类型、浓度都可以 与衬底不同,增加了微电子器件和电路工 艺的灵活性。 多次外延工艺得到多层不同掺杂类型、不 同杂质含量、不同厚度,甚至不同材料的 外延层。

外延工艺常用的硅源

四氯化硅 SiCl4(sil.tet),是应用最广泛,也 是研究最多的硅源--------主要应用于传统外 延工艺 三氯硅烷 SiHCl3(TCS),和 SiCl4类似但温度 有所降低----常规外延生长 二氯硅烷SiH2Cl2( DCS) ----更低温度,选择 外延 硅烷SiH4,更适应薄外延层和低温生长要求, 得到广泛应用。 新硅源:二硅烷Si2H6-----低温外延

生长指(常)数Φ

Φ(cm-1)由实验确定。 与掺杂剂、化学反应、 反应系统,及生长过 程等因素有关:As比B 和P更易蒸发;氯硅烷 反应过程中的Φ要比 硅烷的小;边界层越厚, Φ就越大。

综合效果

减小自掺杂效应措施

降低外延温度,p-Si采用SiH2Cl2, SiHCl3;或SiH4, 但这对As的自掺杂是无效。 对于n-Si衬底,用蒸气压低、扩散速率也低的锑作为 埋层杂质,但锑难以达到很高的掺杂浓度。 重掺杂的衬底,用轻掺杂的硅来密封其底面和侧面, 减少杂质外逸。 低压外延可减小自掺杂,这对砷,磷的效果显著,对 硼的作用不明显。 用离子注入的埋层来降低衬底表面的杂质浓度。 可在埋层或衬底上先生长未掺杂的薄膜来避免衬底中 的杂质外逸,再原位掺杂。 避免高温下用HCl对衬底进行腐蚀、或腐蚀后用低温 气流除去因腐蚀外逸的杂质。

3.1.3 外延工艺用途

优势: 1.高的集电结击穿电压 2.低的集电极串联电阻

双极型晶体管

n+埋层 n-Si外延层 SiO2 p+隔离墙

P-Si衬底

利用外延技术的 pn结隔离是早期 双极型集成电路 常采用的电隔离 方法。

pn结隔离示意图

P阱

n阱

将CMOS电路制作在外 延层上比制作在体硅抛 光片上有以下优点: ①避免了闩锁效应; ②避免了硅层中SiOx的 沉积; ③硅表面更光滑,损伤 最小。

3.2 气相外延

硅气相外延(vapor phase

epitaxy,VPE ),指

含Si外延层材料的物质以气相形式输运至衬底, 在高温下分解或发生化学反应,在单晶衬底上生 长出与衬底取向一致的单晶。

与CVD(Chenmical Vapor Deposition,化学汽相

淀积)类似,是广义上的CVD工艺。

3.2.1硅的气相外延工艺

卧式气相外延设备示意图

设备

立式和桶式外延装置示意图

气相外延设备

工艺步骤及流程

两个步骤: 准备阶段:准备硅基片和进行基座去硅处理; 硅的外延生长 基座去硅的工艺流程: N2预冲洗→H2预冲洗→升温至850℃→升温至 1170℃→HCl排空→HCl腐蚀→H2冲洗→降温 →N2冲洗

气相质量向上,气 流速度、反应 剂浓度、温度 受到扰动的薄 气体层。 基座表面做成 斜坡状,和气 流方向呈一定 角度,α角一般 在3~10°。

基座表面边界层示意图

• 本质上是化学分

2 表面过程 解和规则排列两 个过程。 •SiH4表面外延过 SiH = Si+2H 4 2 程实质上包含了 吸附、分解、迁 移、解析这几个 环节。 •表面外延过程表 明外延生长是横 表面外延过程示意图 向进行。

而外延生长速率正相反。

外延速率的影响因素(三)

反应剂浓度对生长 速率的影响

SiCl4摩尔浓度 大于0.27出现 腐蚀现象

SiCl4浓度与生长速率的关系

速率、温度对结晶类型的影响

-1

3.2.4 外延层中的杂质分布

掺杂采用原位气相掺杂。 杂质掺入效率依赖于:生 长温度、生长速率、气流 中掺杂剂相对于硅源的摩 尔数、反应室几何形状, 掺杂剂自身特性。 有杂质再分布现象

制作在外延层上的双阱CMOS剖面图

微波器件的芯片制造,需要具有突变杂质分布的复杂 多层结构衬底材料。可以采用多层外延工艺来实现这 类衬底材料的制备。 采用异质外延的SOS/CMOS电路,外延衬底为绝缘的 蓝宝石,能够有效地防止元件之间的漏电流,抗辐照 闩锁;而且结构尺寸比体硅CMOS电路小,因SOS结构 不用隔离环,元件制作在硅外延层小岛上,岛与岛之 间的隔离距离只要满足光刻工艺精度,就能达到电隔 离要求,所以元件之间的间距很小,CMOS电路的集成 度也就提高了。

工艺

外延生长工艺流程: N2预冲洗→H2预冲洗→升温至850℃→ 升温至1170℃→HCl排空→HCl抛光 →H2冲洗附面层→外延生长(通入反应 剂及掺杂剂)→H2冲洗1170℃→降温 →N2冲洗

作用是将硅基片表面残存的氧化物(SiOx) 以及晶格不完整的硅腐蚀去掉,露出新鲜 和有完整晶格的硅表面,利于硅外延成核, 而且使衬底硅和外延层硅之间键合良好, 避免衬底硅表面缺陷向外延层中延伸。

SOI技术的诞生背景

近年来, 以笔记本电脑、蜂窝电话、微型通信 设备等为代表的便携式系统发展迅猛。 它们一 般都由高度集成的电子器件组成,且多使用干 电池或太阳能电池作为电源。因此.对于制造 电子器件的材料和性能的要求也越来越高,不 仅要能够实现高度集成,而且要满足高速、低 压、低功耗的要求。体硅CMOS技术在这些方 面都明显不能满足要求。

3.2.1 Si-Cl-H系统反应过程

SiCl2+H2

2SiCl2

Sis+2HCl

Sis+SiCl4

3.2.2气相外延原理

δ x

α

SiH4热分解外延

SiH4 → Si(s)+2H2(g) 优势: 1.反应是不可逆的,没卤化物产生,不存在反向腐蚀效 应,对反应室也无腐蚀; 2.外延温度低,一般是650-900 ℃,最低可在600℃完 成,减弱了自掺杂和扩散效应。 问题: SiH4在气相中可自行分解,造成过早核化,对 外延层的晶体结构产生重要影响,甚至生成多晶; SiH4易氧化形成硅粉,要尽量避免氧化物质和水汽的 存在,否则会影响外延层的质量;缺陷密度高于SiCl4 氢还原法制作外延层;对反应系统要求高

工艺

反应剂有:SiCl4、SiHCl3、 SiH2Cl2、 SiH4,气态反 应剂可稀释后直接通入,而液态反应剂是装在源瓶中, 用稀释气体携带进入反应器。 掺杂剂一般选用含掺杂元素的气态化合物,如PH3、 B2H6、AsH3 SiH4为反应剂, PH3为掺杂剂: SiH4(H2) Si+2H2↑ 2PH3(H2) P+6H2↑ SiH4在主流气体中只百分之几;PH3也用氢气稀释至 十~五十倍。

选择外延(Selective epitaxial growth SEG)

•外延选择性的实现根据硅在绝缘体上很难核化成膜的特性,在硅 表面的特定区域生长外延层而其它区域不生长的技术。 外延生长晶粒成核速度 SiO2〈Si3N4〈Si •利用氧化物表面的高清洁性和源中存在足够的Cl或HCl提高原子 的活动性,以抑制气相中和掩蔽层表面处成核;Cl↑,选择性↑,因 注意:窗口侧壁的生长速率不规则性导 为HCl可将在氧化物表面形成的小团的硅刻蚀掉; 致边缘和中心生长速率差别的问题; •三种类型:晶面取向不同导致的生长特性差别; 1.以Si为衬底,以SiO2或Si3N4为掩膜,在暴露的硅窗口内生长 外延;或在暴露的硅窗口内生长外延,在掩膜生长Poly-Si; 2.同样以Si为衬底,以SiO2或Si3N4为掩膜,在暴露的硅衬底上 刻图形,再生长外延; 3.沟槽处外延生长