基于FPGA和ARM的视频采集处理系统

基于FPGA的视频信号采集与处理系统方案

基于FPGA的视频信号采集与处理系统摘要图像是人类获取和交换信息的主要来源。

现如今,图像处理的应用领域已经涉与到人类生活和工作的方方面面,如航天和航空技术、工业和工程、军事公安、生物医学工程等等。

在图像处理系统中,实时图像的采集是整个系统的前端部分,也是整个系统最重要的部分。

前端的图像采集速度与质量,直接影响到图像处理系统后端的算法处理与应用。

本文主要设计图像处理系统的前端部分,即视频信号的采集。

本文设计中采用CMOS图像传感器OV7670对外界图像进行实时采集,通过FPGA部设计的初始化模块对图像传感器输出信号的格式进行配置。

根据其输出信号的时序,在FPGA部设计采集单元。

采集到的数据一路送到TFT液晶屏上进行实时显示,另一路送入SRAM缓存。

当一帧图像存储完成后,在NIOS II软核中对图像进行处理,并将处理结果以图片的方式,存储到外部存储器SD卡中。

关键字:FPGA;实时图像; CMOS;图像采集AbstractThe image is human access and exchanges the primary source of information.Nowadays, Image processing applications have involved human life and all aspects of the work, such as aerospace and aviation technology, industry and engineering, military police, biomedical engineering and so on. In the image processing system,Real-time image collection is the head part of the whole system, is also the most important part of the whole system. Part of the image acquisition speed and quality, directly affect the image processing system and the algorithm after processing and the application.This paper mainly designs image processing system, namely the head part of video signal collection.This paper applied to the design of CMOS image sensor to the outside world OV7670 real-time image acquisition. Through the FPGA design inside the initialization of the module of image sensor output signal format configuration. According to its output signal timing, In the FPGA design inside acquisition cell. The data collected one way to TFT LCD screen on the real-time display, and the other way into an SRAM cache, when a frame image storage completed, processing the image in the NIOS II MCU. And the result of processing, storage to external storage SD card.Key words:FPGA;Real-time image;CMOS;Image acquisition目录1 前言11.1 数字图像处理发展史11.2 系统整体设计22 CMOS原理和特性与CMOS摄像头的基本结构4 2.1 CMOS原理与特性42.1.1 CMOS数字图像传感器基本原理42.1.2 CMOS图像传感器的特性52.2 COMS传感器的基本结构62.2.1 OV7670简介62.2.2 OV7670部结构83 系统设计与硬件实现123.1 系统结构与工作流程123.1.1系统结构123.1.2系统工作流程123.2器件选型与硬件电路实现123.2.1 FPGA选型123.2.2 FPGA配置电路133.2.3 SDRAM电路实现153.2.4 SRAM电路实现173.2.5其他硬件电路184 系统软件设计194.1 软件设计概述194.2 VHDL简介与特点204.3 OV7670初始化模块214.4 OV7670数据采集模块234.5 SRAM控制模块和TFT液晶控制模块25 4.6 MCU单元设计264.6.1 SOPC Builder简介264.6.2主控制单元MCU的实现284.7 NIOS II软件开发294.7.1 NIOS II集成开发环境294.7.2 MCU软件设计304.7.3简单运动检测314.7.4 BMP图片存储325 总结与展望34参考文献35附录 136附录 243致441 前言1.1 数字图像处理发展史数字图像处理技术起源于20世纪20年代,当时通过海底电缆从英国伦敦到美国纽约传输了一幅照片,它采用了数字压缩技术。

基于ARM+FPGA的实用高精度数据采集器设计

基于ARM+FPGA的实用高精度数据采集器设计本文主要介绍基于ARM+FPGA的高精度数据采集器设计,该设计的特点是利用FPGA控制数据的高速采集,同时采用ARM对外围电路进行控制和数据处理,并实现在液晶屏上的频谱显示。

该设计利用FPGA实现高精度数据采集控制,利用ARM实现光标跟踪、D/A变换及显示等重要指标,并且提供了良好的人机交互界面,其设计方法具有较高的实际应用价值。

文章重点论述了基于ARM+FPGA的实用高精度数据采集器的总体设计、硬件设计和软件设计。

标签:ARM;FPGA;高精度;数据采集;系统引言在科技快速发展的今天,数据采集的重要性是十分显著的,其应用范围越来越广泛,尤其是在工业领域,数据采集的精度和处理的实时性要求逐渐提高,传统的数据采集系统通常采用A/D芯片和主控芯片搭配的手段,该方法功能单一,处理效率低下,如果遇到被测的对象比较复杂并且数据量比较大时,无法满足对数据高精度的要求。

基于ARM+FPGA的高精度数据采集系统能够有效的避免上述问题,ARM作为主控芯片,对整个系统进行控制,并将数据通过USB高速的上传到上位机中,能够借助上位机的强大的运算能力,对数据处理的实时性进行确保,同时能够简便的形成一个用户自定义的数据采集系统,具有良好的通用性;而FPGA能够对数据采样的高精度和高效率进行保证。

本文主要论述基于ARM+FPGA的高精度数据采集器设计相关内容。

1系统总体设计及基本工作原理1.1系统组成高精度数据采集器主要架构由ARM(+DA)+FPGA(+AD)组成。

本系统主要由三个独立的模块组成。

第一部分是数据采集模块,主要完成信号的采集、调理和A/D转换,然后采用并行方式送给处理器;第二部分是处理器模块,接收数据采集模块发送过来的数字信号、处理后显示,并且将处理完的信号送给D/A转换模块;第三部分是D/A转换模块,把数字频谱信号还原并通过示波器显示。

1.2 系统基本工作原理系统工作时,数据采集器置于被监控的设备处,通过传感器对设备的电压或者电流信号进行采样、保持,并送入A/D转换器变成数字信号,然后将该信号送到FPGA内的FIFO中。

基于FPGA的视频采集系统设计

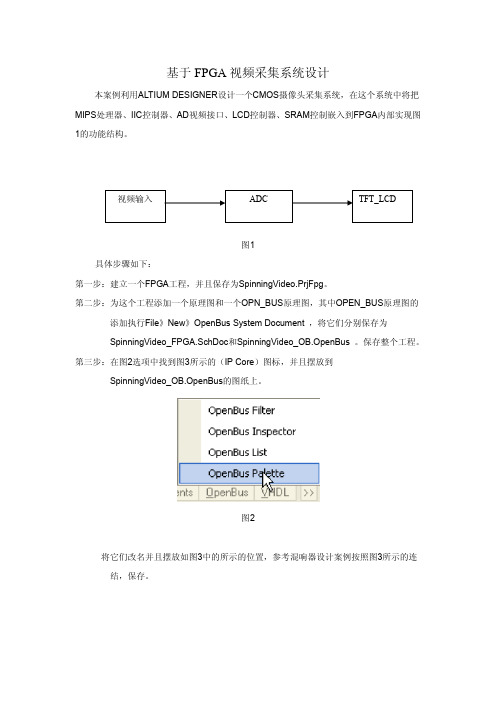

基于FPGA视频采集系统设计本案例利用ALTIUM DESIGNER设计一个CMOS摄像头采集系统,在这个系统中将把MIPS处理器、IIC控制器、AD视频接口、LCD控制器、SRAM控制嵌入到FPGA内部实现图1的功能结构。

图1具体步骤如下:第一步:建立一个FPGA工程,并且保存为SpinningVideo.PrjFpg。

第二步:为这个工程添加一个原理图和一个OPN_BUS原理图,其中OPEN_BUS原理图的添加执行File》New》OpenBus System Document ,将它们分别保存为SpinningVideo_FPGA.SchDoc和SpinningVideo_OB.OpenBus 。

保存整个工程。

第三步:在图2选项中找到图3所示的(IP Core)图标,并且摆放到SpinningVideo_OB.OpenBus的图纸上。

图2将它们改名并且摆放如图3中的所示的位置,参考混响器设计案例按照图3所示的连结,保存。

图3在设计完结构以后,由于图3中所用到的各个IP Core是默认设置下的IP Core,还需要将它们设置为我们需要的模式。

1)配置GPIO为输入和输出,两组IO,每组宽度8位。

方法选中图7中的GPIO图标,右击选择Configure GPIO (Port IO) ,在弹出的对话框中修改相应的设置。

2)配置SDRAM控制器,同样的选择图2.40中的SRAM图标,将它的参数修改为异步,静态,容量为1MB (256K x 32-bit) ,数据位宽度为2 x 16-bit WideDevices。

3)配置TSK-3000A DSP处理器,将它的参数设置为:●Internal Processor Memory to 32 K Bytes (8K x 32-Bit Words)●Multiply/Divide Unit (MDU) to Hardware MDU●On-Chip Debug System to Include JTAG-Based On-Chip Debug System●Disable Breakpoints on Hard Reset在点击OK时,如果出现JTAG错误,可以忽略。

基于Linux的FPGA+ARM高速数据采集系统设计

基于Linux的FPGA+ARM高速数据采集系统设计

基于Linux的FPGA+ARM高速数据采集系统设计

许思琦

【摘要】摘要:对于高速A/D的采集,采用I/O读取方式, ARM9最大能够采集500KSPS的A/D,因此ARM不能实现对更高速度数据读取;为达到更高速,提出了FPGA+ARM的双核架构的高速数据采集的方法,FPGA能够采集2MSPS的A/D,并采用ARM的DMA完成与FPGA的FIFO通信,以及使用Linux的内存映射技术来提高应用层与内核层数据传输效率,完成数据采集;该系统设计了FPGA+ARM 接口电路,开发了Linux下的DMA驱动程序;经试验测试,系统具有高速采集的性能。

【期刊名称】计算机测量与控制

【年(卷),期】2017(025)004

【总页数】4

【关键词】FPGA+ARM双核设计;FIFO+DMA传输;内存映射;高速采集

0 引言

为完成更高速AD数据采集,提出以ARM+FPGA双核硬件架构采集系统;由于FPGA侧重于数据处理,采用的并行多通道处理方式,处理速度为ns级别,能实现对数据高速采集;但是FPGA没有指令系统,控制能力较弱[1],因此,结合ARM的控制能力和FPGA数据处理优势进行双核设计。

由于FPGA与ARM工作在不同的时钟域,采用FPGA异步FIFO来实现数据传输很好地解决这一问题。

为达到数据高速传输,系统采用DMA控制器来读取FIFO数据[2]。

为提高应用程序读取数据速度,采用Linux内核中的内存映射技术提高数据传输效率,完成数据采集。

基于ARM和FPGA的视频监控系统设计

基于ARM和FPGA的视频监控系统设计赵小欢;夏靖波;李明辉【摘要】设计并实现了一种基于ARM+FPGA的视频监控系统,以ARM9处理器为主控制器,FPGA为协处理器,构造ARM与FPGA间的高速数据传输通道和基于Linux的轻量级的图形驱动,完成实时视频采集和显示.实验结果表明,该设计能够流畅播放PAL/NTSC两种制式视频信号,具有良好的扩展性、稳定性和较快的响应速度.【期刊名称】《液晶与显示》【年(卷),期】2010(025)001【总页数】5页(P94-98)【关键词】视频监控;总线接口;图形驱动【作者】赵小欢;夏靖波;李明辉【作者单位】空军工程大学电讯工程学院,陕西西安710077;空军工程大学电讯工程学院,陕西西安710077;空军工程大学电讯工程学院,陕西西安710077【正文语种】中文【中图分类】TP311在工业生产控制中,最直接最有效的监控方法莫过于视频监控,其中ARM处理器由于具有较好的性能与较低的价格已经在各种工业控制领域广泛使用。

但是,随着视频监控对分辨率和实时性的要求越来越高,普通的ARM处理器已难以满足需求,而高档的ARM处理器由于价格昂贵而难以普遍使用。

采用多处理器架构是缓解性能与价格矛盾的一种较好的方案,但是在多处理器结构中,多个处理器之间的数据传输效率直接制约着整个系统的性能,稍有不慎就会成为系统性能的瓶颈。

本文采用ARM与FPGA互连的主从结构来完成视频信号的采集:以ARM为系统的核心,协调整个系统的工作;以FPGA为协处理器连接在ARM的一个BAN K上,完成前端视频信号的处理[1]。

该方案充分发挥了ARM与FPGA各自的优势,很好地实现了视频监控功能,系统具有很好的灵活性,稍加改造就能应用于其他的嵌入式设计中。

视频信号十分复杂。

复合视频信号将色差信号B-Y及R-Y以3.58 MHz的次载波载送在辉度信号Y信号里,同时还包括了行同步信号、行消隐信号、场同步信号、场消隐信号等同步信号。

基于FPGA的实时视频图像采集处理系统设计

基于FPGA的实时视频图像采集处理系统设计高俊岭;陈志飞;章佩佩【期刊名称】《电子技术应用》【年(卷),期】2018(044)002【摘要】针对目前数字图像采集处理技术的实时性、大容量、小型化等特点,设计了一种基于FPGA的实时视频图像采集处理电路系统.采用FPGA作为整个系统的控制和图像数据处理中心.DDR2 SDRAM为高速储存模块核心器件,CMOS 7670为视频图像采集器件.并通过Quratus Ⅱ和Modelsim等软件对系统的边缘检测算法、控制过程、各个模块等进行硬件工程设计和仿真,实现了视频图像从采集、存储到处理、显示的整个过程.实验表明,视频图像采集处理的动态画面流畅、清晰、实时性好.%Based on characteristics of instantaneously,large capacity and miniaturization of digital image acquisition and processing technology,a real-time video image acquisition and processing circuit system was designed,FPGA was used as the center of controlling the whole system and the center of processing image data.With DDR2 SDRAM the core component of high speed storage module,and CMOS 7670 the video image acqu isition device.Through the Quratus Ⅱ and Modelsim software for edge detection algorithm and the control process,each module of the hardware design and simulation,the realization of the video images from the collection and storage to the treating and display,which shows smooth,clear and real-time.【总页数】4页(P10-12,19)【作者】高俊岭;陈志飞;章佩佩【作者单位】安徽理工大学电气与信息工程学院,安徽淮南230001;安徽理工大学电气与信息工程学院,安徽淮南230001;安徽理工大学电气与信息工程学院,安徽淮南230001【正文语种】中文【中图分类】TN919.5【相关文献】1.基于FPGA的实时视频图像几何校正系统设计 [J], 陈文艺;田科;周娟2.基于FPGA高速视频图像实时采集与处理系统设计 [J], 田杰;王广龙;乔中涛;高凤岐3.基于FPGA+DSP实时图像采集处理系统设计 [J], 靖固;杨华宇4.基于FPGA和DSP的图像实时采集处理系统设计 [J], 崔锡奎;刘敬猛;5.基于FPGA和DSP的图像实时采集处理系统设计 [J], 崔锡奎;刘敬猛因版权原因,仅展示原文概要,查看原文内容请购买。

基于arm和fpga的嵌入式高速图像采集存储系统

基于ARM和FPGA的嵌入式高速图像采集存储系统现代化生产和科学研究对图像采集系统要求日益提高。

传统图像采集系统大都是基于PC机上,而在一些特殊的场合,尤其是在实时性要求较高时,普通的PC机显然无法满足应用要求。

文中设计了一种基于ARM 和FPGA的嵌入式的图像采集存储系统,可以很好地解决实时的嵌入式图像采集和存储问题。

它主要包括图像采集模块、图像处理模块以及图像存储模块等。

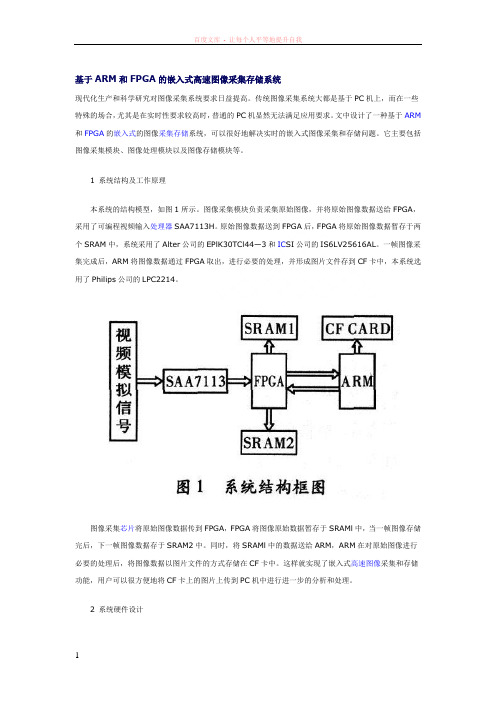

1 系统结构及工作原理本系统的结构模型,如图1所示。

图像采集模块负责采集原始图像,并将原始图像数据送给FPGA,采用了可编程视频输入处理器SAA7113H。

原始图像数据送到FPGA后,FPGA将原始图像数据暂存于两个SRAM中,系统采用了Alter公司的EPlK30TCl44—3和IC SI公司的IS6LV25616AL。

一帧图像采集完成后,ARM将图像数据通过FPGA取出,进行必要的处理,并形成图片文件存到CF卡中,本系统选用了Philips公司的LPC2214。

图像采集芯片将原始图像数据传到FPGA,FPGA将图像原始数据暂存于SRAMl中,当一帧图像存储完后,下一帧图像数据存于SRAM2中。

同时,将SRAMl中的数据送给ARM,ARM在对原始图像进行必要的处理后,将图像数据以图片文件的方式存储在CF卡中。

这样就实现了嵌入式高速图像采集和存储功能,用户可以很方便地将CF卡上的图片上传到PC机中进行进一步的分析和处理。

2 系统硬件设计2.1 图像采集模块用可编程视频输入处理器SAA7113H进行视频信号处理。

SAA7113H内部集成了强大图像色度、亮度处理功能以及多种输出模式;有32个工作寄存器,在系统复位时,必须通过I2C总线对其进行初始化。

本系统使用灰度图像,没有使用色度信号,所以数据线为8位。

SAA7113H与FPGA的接口,如图2所示。

2.2 FPGA模块FPGA主要作用是把图像采集芯片传过来的图像原始数据,采取乒乓操作的方式,暂存于两片SRAM 中。

探析基于FPGA的视频采集系统设计

探析基于FPGA的视频采集系统设计视频图像采集是数字图像处理、监控系统等应用的必要组成部分。

图像采集与处理在工农医等领域得到了广泛应用,目前随着科技的不断发展,各种图像采集设备层出不穷,性能和实用性也得到了市场验证。

视频采集系统的实现方法有很多,本文对基于FPGA的视频采集系统设计进行探讨分析。

标签:FPGA;视频采集;系统设计1、FPGA的应用优势(1)逻辑功能强大。

FPGA采用SRAM编程技术实现系统的快速运行,增强其逻辑功能;布线资源丰富,只需擦除更改程序,即可满足系统设计所需的不同逻辑功能;可编程I/O资源丰富,可满足复杂数字逻辑设计。

(2)设计灵活。

FPGA内部的嵌入式RAM支持多种操作模式,异步先入先出(FirstInputFirstOut,FIFO)数据缓冲器可拓展FPGA的设计范围,使设计选择更加灵活;FPGA内部包含的逻辑门数较多,可满足复杂设计要求。

(3)操作简便。

为保证FPGA系统的可靠性,在使用FPGA芯片之前需进行稳定性测试,在此之后设计者只要利用软硬件环境便可设计系统功能;在实现FPGA系统不同逻辑功能时,设计者可通过多次反复编程予以实现,无需更改硬件电路。

2、基于FPGA的视频采集系统方案整体框架(1)视频采集部分:将摄像头采集到的模拟视频数据CVBS转换成数字视频格式YUV4:2:2,包括I2C总线配置,TIU656解码。

(2)视频处理部分:为适应VGA的不同显示,对视频数据做相应预处理,包括彩色VGA数据处理,灰度VGA数据处理,Sobel边沿检测数据处理,Prewitt边沿检测数据处理。

(3)视频存储部分:将视频数据储存在容量为4M×16×4Banks的SDRAM中,主要包括SDRAM控制器设计。

(4)VGA显示部分:将实时的视频数据在显示器上显示出来。

包括色度空间转换,VGA时序产生,ADV7123视频数据编码。

3、系统的具体工作流程系统上电后,由配置芯片重新配置FPGA;配置完成后,FPGA对视频解码芯片进行初始化;视频解码芯片进入工作状态,采集4路模拟视频信号;FPGA 初步处理4路数字视频信号;处理后,将4路视频数据存储到SDRAM中;在TFTLCD上显示所采集的数字化视频信息;利用IO口,可在外部切换采集通道,对系统进行复位操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

iA A; DT

的 ,可以 方便 地实 现 对视 频信 号 的 实时 压 缩和 解 压缩 。在进 行 压 缩时 ,Z 3 00 受YU 422 字视 频信号 ,将 其 编码为 J E  ̄ R 66接 V :: 数 P G

流输 出 。Z 3 0 0 R 6 6 对像 素块 ¥ C I 视 频信 号可 实现 高 达2 ~3 帧/ ICR  ̄ 5 0 秒的压 缩 ;灵活 的数据 接 L ,支持 三种 Y 视频 接 口模式 ,即 8 l UV 位

imC f MOSF A 、 ( V L / 有效 / 帧

b gn ei i mC S L A ) f MO V L (

主模 式 、 1位 从模 式 和8 从 模 式 ;3 不 同 的 比特率 控 制模 式 用 6 位 种

e ei {r F A , V L = 2 1) l (Pe V Li A }= ’ 0 s f F b

在处 理 前一 帧

mCM 0 S FV L A

VAL mCMOS L

—

/ / 正

_ E _ AN ’

l) ' l ) (( “ U y

nW A I T

SC2 0 3 4l

b gi e n

23 . AR M处 理 器 和 网 卡芯 片

ARM处 理 器选 用二 星 公 司 的 ¥ C 4 0 3 2 1 ,该 处 理 器拥 有 独 立 的 1K 指 令C c e H 数 据C c e B 6 a h  ̄ KB 1 6 a h ,MMU,支持T T C 控 F 的L D

C 80 A ¥ 90

<=

< =

O;

i LVAL;

N2 网卡接 口示意 图

2 视 频 压缩 芯 片 . 4

JE P G编解码 芯片 Z 3 0 0 R 6 6 是专 为视 频采 集与 编辑 应 用而设 计

mC MOS D T < AA =

/ 取数 据送 ) F G / 读 ,P A .

的 输 出 。所 以 ,在 F AL 个 周 期 内 , 图像传 感 器 正好 输 出 了 完 V 一 整 的一 帧 图像 。分 辨率 为6 0 8 。仅 当F AL V 信号 同 时 4 40 X V 和L AL 为高 电平 时 ,传 感 器输 出数 据 D[: 有效 ,F GA在每 个 像 素 时 90 ] P

性 ,系统选 用 了Al r公 司C co eI系列 的E 2 3F 7C 。该 ta e y ln I P C 5 62 6 芯 片具 有 30 0 5 0 个逻 辑 单元 、62 引脚 、4 5 用 户 自定 义I 7个 7个 / 0接

口、3 个嵌 入式乘 法 器和4 5 个锁 相环 ,完 全可 以满 足 系统要 求 。

_

/ / 当前 帧有 效且 前 一 帧处 理完

m CM 0S FVAL < 1 ;

】 CS A -— —● n { S 1 G 3I N — - — C}p El l

IAN n ( R _ I)

l AN I O W 1 I

{ :n W l O

— —

I “0R

钟 P XC K 升 沿时 将 有 效数 据读 入 。经 实j】 感 器 正常 工 作 I L 上 ! ,传 J ! l 时 ,S L C K,L A 频 率约 为 7 6 H  ̄ 1 . H 。 V L . k z 42 z 5 k 本 系统 采用 V rl gHDL 言来编 写 C ei o 语 M0s 图像传 感 器的 时 序 驱 动 。 在 实 际 设训 中 ,把 控 制 模 块 分 成 两部 分 :1 C C n i 2 — o fg 模块 根 据 设定 的 曝 光时 间 来发 生 IC 线S L , S A 时序 ,而 总 C K ̄ D T I 3 C pu e a t r模块 则负责 与传 感 器的 数据 接 1 ,读 入 1 位 的图像 数据 , 5 1 0 并 送到 下一 级模 块进 行相 应 处理 。以 下是 C p r模块 部分 代码 : at e u a y @(o e g L r e e g S ) l s p sd e C K o g d e R T wa i n i

f 、儿 、 — 0j 九 刁 叶 儿 口 1 H , 、一 吲 戈 j 。

ifRS ) f! T i

… … …

/ / 各信 号 清零 复位

。

I fDR 1:l ) l90 A

l r { :] D A[50

1 OM 1 D

S :】 Af90 1

制 器 ,NA ND闪存控 制 器 ,3 串 口,4 路  ̄DMA,4 带P M的时 路 W 钟 ,最 高 可运 行 在 2 3 0 MHz 。系 统采 用 的 网卡 芯 片 是C¥ 9 0 8 0A,

它是 用于 嵌 入式 设备 的 低 成本 以太 局 域 网控 制 器 。它 的高 度 集成 设计使其不再需要其它以太网控制器所必需的昂贵外部器件 。

C 80 A S 90 包括 片 kR AM, 1B s—传 输 和接 收滤 波器 ,以及带 2 0 ae T 4 毫 安驱 动 的直 接I A 总 线接 口。除 _高度 集成 ,C 8 0A 提 供 S一 『 ¥90 还 其 它性 能和 配 置选择 。它独 特 的P c eP g 结 构 可 自动 适 应 网络 aktae 通信 量模 式的 改变 和现 有 系统资 源 ,从而 提高 系 统效 率 。图2 为网

S )1 :】 I 0 【5

n 3H S1

Pr FVAL e

—

<=

i VA L; F

l lN R l A LN n E R A M M

LAN nMlM W

I10 N、 0 R nE R M M

n EM W M

i (P e F ALiVAL} 2b 1 && mS AR f {r V , ( F 一 ’0 ) T T)