以太网设备PCB布线参考

PCB布线设计规范精选全文

可编辑修改精选全文完整版印制电路板设计规范一、适用范围该设计规范适用于常用的各种数字和模拟电路设计。

对于特殊要求的,尤其射频和特殊模拟电路设计的需量行考虑。

应用设计软件为Protel99SE。

也适用于DXP Design软件或其他设计软件。

二、参考标准GB 4588.3—88 印制电路板设计和使用Q/DKBA—Y004—1999 华为公司内部印制电路板CAD工艺设计规范三、专业术语1.PCB(Print circuit Board): 印制电路板2.原理图(SCH图):电路原理图,用来设计绘制,表达硬件电路之间各种器件之间的连接关系图。

3.网络表(NetList表):由原理图自动生成的,用来表达器件电气连接的关系文件。

四、规范目的1.规范规定了公司PCB的设计流程和设计原则,为后续PCB设计提供了设计参考依据。

2.提高PCB设计质量和设计效率,减小调试中出现的各种问题,增加电路设计的稳定性。

3.提高了PCB设计的管理系统性,增加了设计的可读性,以及后续维护的便捷性。

4.公司正在整体系统设计变革中,后续需要自主研发大量电路板,合理的PCB设计流程和规范对于后续工作的开展具有十分重要的意义。

五、SCH图设计5.1 命名工作命名工作按照下表进行统一命名,以方便后续设计文档构成和网络表的生成。

有些特殊器件,没有归类的,可以根据需求选择其英文首字母作为统一命名。

对于元器件的功能具体描述,可以在Lib Ref中进行描述。

例如:元器件为按键,命名为U100,在Lib Ref中描述为KEY。

这样使得整个原理图更加清晰,功能明确。

5.2 封装确定元器件封装选择的宗旨是1. 常用性。

选择常用封装类型,不要选择同一款不常用封装类型,方便元器件购买,价格也较有优势。

2. 确定性。

封装的确定应该根据原理图上所标示的封装尺寸检查确认,最好是购买实物后确认封装。

3. 需要性。

封装的确定是根据实际需要确定的。

总体来说,贴片器件占空间小,但是价格贵,制板相同面积成本高,某些场合下不适用。

以太网PCB布布线

以太网PCB布布线————————————————————————————————作者:————————————————————————————————日期:以太网PCB布局布线我们现今使用的网络接口均为以太网接口,目前大部分处理器都支持以太网口。

目前以太网按照速率主要包括10M、10/100M、1000M 三种接口,10M应用已经很少,基本为10/100M所代替。

目前我司产品的以太网接口类型主要采用双绞线的RJ45接口,且基本应用于工控领域,因工控领域的特殊性,所以我们对以太网的器件选型以及PCB设计相当考究。

从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。

大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。

面对如此复杂的接口电路,相信各位硬件工程师们都想知道该硬件电路如何在PCB上实现。

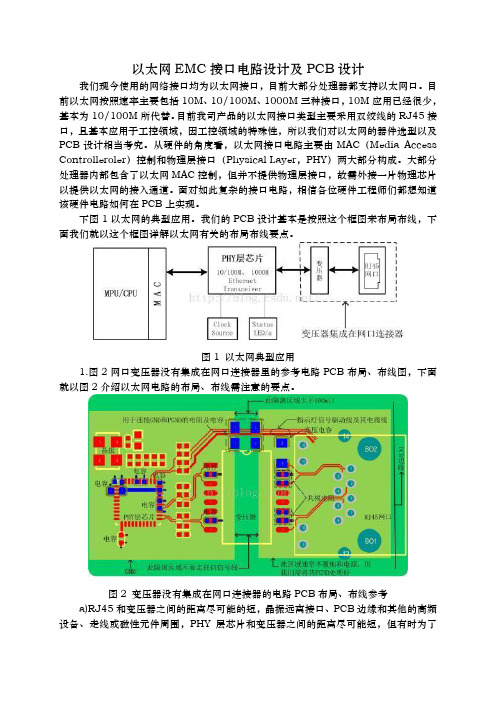

下图 1以太网的典型应用。

我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。

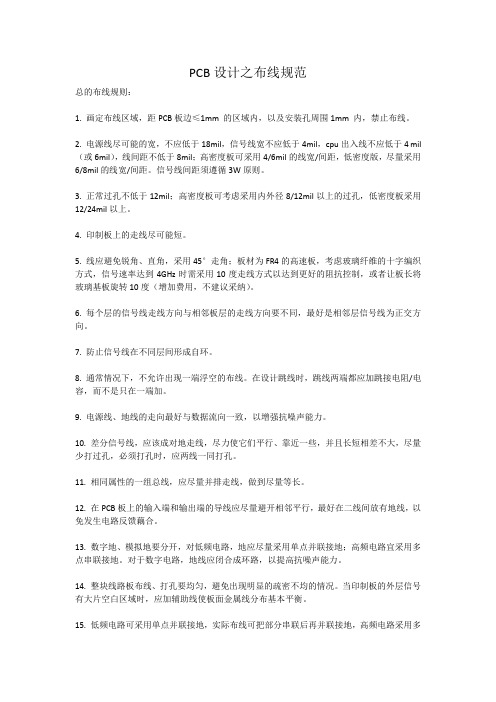

图 1 以太网典型应用1. 图 2网口变压器没有集成在网口连接器里的参考电路PCB 布局、布线图,下面就以图 2介绍以太网电路的布局、布线需注意的要点。

图 2变压器没有集成在网口连接器的电路PCB布局、布线参考a) RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB 边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;b) PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小;c) 网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;d) 网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil);e) 变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。

以太网EMC接口电路设计与PCB设计说明

以太网EMC接口电路设计及PCB设计我们现今使用的网络接口均为以太网接口,目前大部分处理器都支持以太网口。

目前以太网按照速率主要包括10M、10/100M、1000M三种接口,10M应用已经很少,基本为10/100M所代替。

目前我司产品的以太网接口类型主要采用双绞线的RJ45接口,且基本应用于工控领域,因工控领域的特殊性,所以我们对以太网的器件选型以及PCB设计相当考究。

从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。

大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。

面对如此复杂的接口电路,相信各位硬件工程师们都想知道该硬件电路如何在PCB上实现。

下图1以太网的典型应用。

我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。

图1 以太网典型应用1.图2网口变压器没有集成在网口连接器里的参考电路PCB布局、布线图,下面就以图2介绍以太网电路的布局、布线需注意的要点。

图2 变压器没有集成在网口连接器的电路PCB布局、布线参考a)RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;b)PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小;c)网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;d)网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil);e)变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。

PCB布局布线28页word文档

PCB布局、布线基本原则一、元件布局基本规则1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开;2.定位孔、标准孔等非安装孔周围1.27mm 内不得贴装元、器件,螺钉等安装孔周围3.5mm(对于M2.5)、4mm(对于M3)内不得贴装元器件;3. 卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路;4. 元器件的外侧距板边的距离为5mm;5. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm;6. 金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm。

定位孔、紧固件安装孔、椭圆孔及板中其它方孔外侧距板边的尺寸大于3mm;7. 发热元件不能紧邻导线和热敏元件;高热器件要均衡分布;8. 电源插座要尽量布置在印制板的四周,电源插座与其相连的汇流条接线端应布置在同侧。

特别应注意不要把电源插座及其它焊接连接器布置在连接器之间,以利于这些插座、连接器的焊接及电源线缆设计和扎线。

电源插座及焊接连接器的布置间距应考虑方便电源插头的插拔;9. 其它元器件的布置:所有IC元件单边对齐,有极性元件极性标示明确,同一印制板上极性标示不得多于两个方向,出现两个方向时,两个方向互相垂直;10、板面布线应疏密得当,当疏密差别太大时应以网状铜箔填充,网格大于8mil(或0.2mm);11、贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。

重要信号线不准从插座脚间穿过;12、贴片单边对齐,字符方向一致,封装方向一致;13、有极性的器件在以同一板上的极性标示方向尽量保持一致。

二、元件布线规则1、画定布线区域距PCB板边≤1mm的区域内,以及安装孔周围1mm内,禁止布线;2、电源线尽可能的宽,不应低于18mil;信号线宽不应低于12mil;cpu 入出线不应低于10mil(或8mil);线间距不低于10mil;3、正常过孔不低于30mil;4、双列直插:焊盘60mil,孔径40mil;1/4W电阻: 51*55mil(0805表贴);直插时焊盘62mil,孔径42mil;无极电容: 51*55mil(0805表贴);直插时焊盘50mil,孔径28mil;5、注意电源线与地线应尽可能呈放射状,以及信号线不能出现回环走线。

PCB设计之布线规范

PCB设计之布线规范总的布线规则:1. 画定布线区域,距PCB板边≤1mm 的区域内,以及安装孔周围1mm 内,禁止布线。

2. 电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4 mil (或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。

信号线间距须遵循3W原则。

3. 正常过孔不低于12mil;高密度板可考虑采用内外径8/12mil以上的过孔,低密度板采用12/24mil以上。

4. 印制板上的走线尽可能短。

5. 线应避免锐角、直角,采用45°走角;板材为FR4的高速板,考虑玻璃纤维的十字编织方式,信号速率达到4GHz时需采用10度走线方式以达到更好的阻抗控制,或者让板长将玻璃基板旋转10度(增加费用,不建议采纳)。

6. 每个层的信号线走线方向与相邻板层的走线方向要不同,最好是相邻层信号线为正交方向。

7. 防止信号线在不同层间形成自环。

8. 通常情况下,不允许出现一端浮空的布线。

在设计跳线时,跳线两端都应加跳接电阻/电容,而不是只在一端加。

9. 电源线、地线的走向最好与数据流向一致,以增强抗噪声能力。

10. 差分信号线,应该成对地走线,尽力使它们平行、靠近一些,并且长短相差不大,尽量少打过孔,必须打孔时,应两线一同打孔。

11. 相同属性的一组总线,应尽量并排走线,做到尽量等长。

12. 在PCB板上的输入端和输出端的导线应尽量避开相邻平行,最好在二线间放有地线,以免发生电路反馈藕合。

13. 数字地、模拟地要分开,对低频电路,地应尽量采用单点并联接地;高频电路宜采用多点串联接地。

对于数字电路,地线应闭合成环路,以提高抗噪声能力。

14. 整块线路板布线、打孔要均匀,避免出现明显的疏密不均的情况。

当印制板的外层信号有大片空白区域时,应加辅助线使板面金属线分布基本平衡。

15. 低频电路可采用单点并联接地,实际布线可把部分串联后再并联接地,高频电路采用多点串连接地。

pcb布线规则及技巧

9. 在芯片中若出现成排电源引脚或地引脚(如AVDD和DGND)最好采用如下连接方 式(该方式可避免芯片发生偏移)

pcb布线规则及技巧

10. 摄像头中信号线应尽量放在底层,布线时过孔应尽量打在芯片外部,所有布 线与最外层裁剪框应至少保证0.15MM距离。 11. 在摄像头中,布线结束后需将所有角转变成倒角,避免反射形成干扰;在转 接板中,若只是作为测试用,要求不高是可不必转成倒角,且在布线过程中允许 使用部分直角。 12. 布线时,板子左右两边边缘最好放置一条地线;铺铜时地线最好都能保证连 接以增加导电性。 13. 金手指布线时过孔只能打在补强以下。 14. 布线过程中,过孔的大小为硬板0.4/0.2,其余板0.35/0.15或0.3/0.1 15. MIPI接口是指串行差分接口,DVP接口是指并行传输接口

pcb布线规则及技巧

EMI是英文Electro Magnetic Interference 的缩写,是 电磁干扰的意思。电源是发生EMI的重要来源。电源电路 中EMI电路的作用是滤除由电网进来的各种干扰信号,防止电源开关电路形成的高频扰窜电网,或对设备和应 用环境造成干扰。在其它电路或设备中,也往往要用到EMI电路或采取其它措施防止和抑制EMI的发生,以防止 和抑制干扰,如通讯电缆的终端电阻,电脑的机箱,变压器的屏蔽罩,用顺磁材料或抗磁材料来疏导或阻止电 磁场的穿行等等。EMI是产品投放市场前电工认证的一个必检内容。 我们平时经常见到一些产品由于EMI不过 关的报告或投诉。我们常见的开关电源入口处,有一个两个绕组的电感,这个电感是共模抑制电感,也起到减 少EMI的作用。另外,一些数据线的两头,会鼓出来一个大包包(例如电脑彩显的数据线上,一些数码相机的 数据线上),其实里面就是一个减少EMI的磁环。 pcb布线规则及技巧

pcb布线法则大全

pcb布线法则大全下降,有时甚至阻碍到产品的成功率。

因此对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的缘故,现只对降低式抑制噪音作以表述:众所周知的是在电源、地线之间加上去耦电容。

尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm 对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能如此使用) 用大面积铜层作地线用,在印制板上把没被用上的地点都与地相连接作为地线用。

或是做成多层板,电源,地线各占用一层。

2、数字电路与模拟电路的共地处理现在有许多PCB 不再是单一功能电路〔数字或模拟电路〕,而是由数字电路和模拟电路混合构成的。

因此在布线时就需要考虑它们之间互相干扰问题,专门是地线上的噪音干扰。

数字电路的频率高,模拟电路的敏锐度强,对信号线来说,高频的信号线尽可能远离敏锐的模拟电路器件,对地线来说,整人PCB对外界只有一个结点,因此必须在PCB内部进行处理数、模共地的问题,而在板内部数字地和模拟地实际上是分开的它们之间互不相连,只是在PCB与外界连接的接口处〔如插头等〕。

数字地与模拟地有一点短接,请注意,只有一个连接点。

也有在PCB上不共地的,这由系统设计来决定。

3、信号线布在电〔地〕层上在多层印制板布线时,由于在信号线层没有布完的线剩下差不多不多,再多加层数就会造成白费也会给生产增加一定的工作量,成本也相应增加了,为解决那个矛盾,能够考虑在电〔地〕层上进行布线。

第一应考虑用电源层,其次才是地层。

因为最好是保留地层的完整性。

4、大面积导体中连接腿的处理在大面积的接地〔电〕中,常用元器件的腿与其连接,对连接腿的处理需要进行综合的考虑,就电气性能而言,元件腿的焊盘与铜面满接为好,但对元件的焊接装配就存在一些不良隐患如:①焊接需要大功率加热器。

pcb布局布线技巧及原则(全面)

pcb布局布线技巧及原则[ 2020-11-16 0:19:00 | By: lanzeex ]PCB 布局、布线基本原则一、元件布局基本规则1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开;2.定位孔、标准孔等非安装孔周围1.27mm 内不得贴装元、器件,螺钉等安装孔周围3.5mm(对于M2.5)、4mm(对于M3)内不得贴装元器件;3. 卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路;4. 元器件的外侧距板边的距离为5mm;5. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm;6. 金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm。

定位孔、紧固件安装孔、椭圆孔及板中其它方孔外侧距板边的尺寸大于3mm;7. 发热元件不能紧邻导线和热敏元件;高热器件要均衡分布;8. 电源插座要尽量布置在印制板的四周,电源插座与其相连的汇流条接线端应布置在同侧。

特别应注意不要把电源插座及其它焊接连接器布置在连接器之间,以利于这些插座、连接器的焊接及电源线缆设计和扎线。

电源插座及焊接连接器的布置间距应考虑方便电源插头的插拔;9. 其它元器件的布置:所有IC 元件单边对齐,有极性元件极性标示明确,同一印制板上极性标示不得多于两个方向,出现两个方向时,两个方向互相垂直;10、板面布线应疏密得当,当疏密差别太大时应以网状铜箔填充,网格大于8 mil(或0.2mm);11、贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。

重要信号线不准从插座脚间穿过;12、贴片单边对齐,字符方向一致,封装方向一致;13、有极性的器件在以同一板上的极性标示方向尽量保持一致。

二、元件布线规则1、画定布线区域距PCB 板边≤1mm 的区域内,以及安装孔周围1mm 内,禁止布线;2、电源线尽可能的宽,不应低于18mil;信号线宽不应低于12mil;cpu 入出线不应低于10mil(或8mil);线间距不低于10mil;3、正常过孔不低于30mil;4、双列直插:焊盘60mil,孔径40mil;1/4W 电阻: 51*55mil(0805 表贴);直插时焊盘62mil,孔径42mil;无极电容: 51*55mil(0805 表贴);直插时焊盘50mil,孔径28mil;5、注意电源线与地线应尽可能呈放射状,以及信号线不能出现回环走线。

千兆以太网水晶头制作和布线

第二课堂千兆 5 类或超 5 类双绞线的形式与百兆网线的形式相同,也分为直通和交叉两种。

直通网线与我们平时所使用的没有什么差别, 都是一一对应的。

但是传统的 百兆网络只用到 4 根线缆来传输,而千兆网络要用到 8 根来传输,所以千兆交叉网线的制作与百 兆不同,制作方法如下:1 对 3,2 对 6,3 对 1,4 对 7,5 对 8,6 对 2,7 对 4,8 对 5 例如: 一端为:半橙、橙,半绿、兰,半兰、绿,半棕、棕; 另一端:半绿、绿,半橙、半棕、棕,橙,兰,半兰千 兆 5 类或超 5 类双绞线的形式与百兆网线的形式相同,也分为直通和交叉两种。

直通网线与我们平时所使用的没有什么差别, 都是一一对应的。

但是传统的百兆网络 只用到 4 根线缆来传输,而千兆网络要用到 8 根来传输,所以千兆交叉网线的制作与百 兆不同,制作方法如下:1 对 3,2 对 6,3 对 1,4 对 7,5 对 8,6 对 2,7 对 4,8 对 5 例如: 一端为:半橙、橙,半绿、兰,半兰、绿,半棕、棕; 另一端:半绿、绿,半橙、半棕、棕,橙,兰,半兰2.AVAYA(CommScope) 单层结构,处理好十字芯,套好扣环,导入导线框架扣好,裁齐. 尾扣在测试通过后用 502 固定死,外套也要用 502 固定死. 全过程要小心,仔细, 开绞距离越短越好,1.千兆主干交换机,接千兆分交换机,用什么线? 六类线(CAT6) 2.千兆主干交换机,接百兆分交换机,用什么线? 买带两 1000Mbps 铜口的 26****换机 .六类线(CAT6) 3.千兆主干交换机,接新服务器,用什么线? .六类线(CAT6) 4.千兆主干交换机,接老服务器,用什么线? 超五类(CAT5E).,跑 100Mbps 5.千兆分交换机,接新机器,用什么线? .预算多就用六类线(CAT6),起码要用超五类(CAT5E). 6.百兆分交换机,接旧机器,用什么线?用超五类.原来有可以不动,质量太差的话剪掉 ,全新布过超五类(CAT5E), 以上六类线配六类头,超五类配合屏蔽头(也不贵) , 保证线和头都要正品!!! 超五类头用 AMP 压线钳压制,六类头用机压或自做工具压制.线序均按照 568B 顺序排列,然后用相关检测工具进行测试。

非常实用的PCB布局布线规则,画出美而高性能的板子

非常实用的PCB布局布线规则,画出美而高性能的板子01布局元器件布局的10条规则:1. 遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.2. 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.3. 元器件的排列要便于调试和维修,亦即小元件周围不能放置大元件、需调试的元、器件周围要有足够的空间。

4. 相同结构电路部分,尽可能采用“对称式”标准布局;5. 按照均匀分布、重心平衡、版面美观的标准优化布局;6. 同类型插装元器件在X或Y方向上应朝一个方向放置。

同一种类型的有极性分立元件也要力争在X或Y方向上保持一致,便于生产和检验。

7. 发热元件要一般应均匀分布,以利于单板和整机的散热,除温度检测元件以外的温度敏感器件应远离发热量大的元器件。

8. 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分。

9、去偶电容的布局要尽量靠近IC的电源管脚,并使之与电源和地之间形成的回路最短。

10、元件布局时,应适当考虑使用同一种电源的器件尽量放在一起, 以便于将来的电源分隔。

02布线(1)布线优先次序键信号线优先:摸拟小信号、高速信号、时钟信号和同步信号等关键信号优先布线密度优先原则:从单板上连接关系最复杂的器件着手布线。

从单板上连线最密集的区域开始布线注意点:a、尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。

必要时应采取手工优先布线、屏蔽和加大安全间距等方法。

保证信号质量。

b、电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。

c、有阻抗控制要求的网络应尽量按线长线宽要求布线。

(2)四种具体走线方式1 、时钟的布线:时钟线是对EMC 影响最大的因素之一。

在时钟线上应少打过孔,尽量避免和其它信号线并行走线,且应远离一般信号线,避免对信号线的干扰。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

REALTEK RTL8208DESIGN AND LAYOUT GUIDE1. IntroductionThis document provides detailed design and layout guidelines to achieve the best performance for implementing a 2-layer board design with the RTL8208 Octal PHY.The RTL8208 is the smallest Oct-PHY in the industry, having the smallest foot-print. To benefit BOM costs, one external PNP transistor is used to generate a 2.5V power source. Care needs to be taken, however, to prevent signals from cross-talk and interference due to the small package, and most importantly, to support a stable 2.5V power plane which determines the performance of data recovery and transmit jitter.RMII Signal Diagram RMII Signal Diagram50MHz Oscillator Solution 25MHz Crystal Solution2. General Design and Layout GuideIn order to achieve maximum performance with the RTL8208, good design attention is required throughout the design and layout process. The following recommendations will help implement a high performance system.2.1 General Guidelines• Create a good power source, minimizing noise from switching power supply circuits (<50mV).• Verify the quality of the components, such as clock source and transformer, to meet the application requirements. • Keep power and ground noise levels below 50mV.• Use bulk capacitors (4.7uF-10uF) between the power and ground planes.•Use 0.1uF decoupling capacitors to reduce high-frequency noise on the power and ground planes. • Keep decoupling capacitors as close as possible to the RTL8208. • Provide termination on all high-speed switching signals.2.2 Differential Signal Layout Guidelines• Keep differential pairs as close as possible and route both traces as identically as possible, meaning width, length and location.• Avoid vias and layer changes if possible.• Keep the transmit and receive pairs as far from each other as possible. Run them orthogonally or separated by a ground plane if possible.• Avoid right-angle signal tracesBbad !Bgood !2.3 Clock Circuit• The clock should be 25M/50MHz/125MHz 100ppm with jitter less than 0.5ns.• The length of the clock path to the RTL8208 should be equal to the length of the clock path to the MAC. • If possible, surround the clock by ground traces to minimize high-frequency emissions.• Keep the MDC trace away from the crystal X1 input path, to avoid unnecessary interference. This is especially important while using a crystal solution.• Keep signal traces from running parallel to clock traces. Traces parallel to clock traces are a worst case design and will pick up interference from the clock.2.4 2.5V Power• Do not connect a bead directly between the collector of the PNP transistor and VDDAL. Use of a bead will affect the stability of the 2.5V power significantly.• Use a bulk of capacitor (4.7uF-10uF) between the collector of the PNP transistor and the ground plane.• Do not use one PNP transistor for more than one RTL8208 chip, even if the rating is enough. Use one transistor for each RTL8208.8 2 0 88 2 0 82.5 Power Planes• Divide the power plane into 2.5V digital, 2.5V analog and 3.3V analog if you design a 4-layer PCB layout.• It is recommended to combine both 2.5V digital and analog power as a connected power-ring when designing a 2-layer PCB layout.• Use 0.1µF decoupling capacitors and bulk capacitors between each power plane and ground plane.2.6 Ground Planes• Keep the system ground region as one continuous, unbroken plane that extends from the primary side of the transformer to the rest of the board.• Place a moat (gap) between the system ground and chassis ground.• Ensure the chassis ground area is voided at some point such that no ground loop exists on the chassis ground area.3. Transformer Options• The magnetics support AutoMDIX and with 1:1 turn ratio on both the transmit and receive paths are valid for RTL8208. There are many venders improving their magnetics design to meet this requirement, and several are listed below.Vendor Model Vendor Model40ST1041AXPulse H1164 BothHandMagnetic 1 ML164 GTS FC-638L• The center-tap of the primary side of the transformer should not be connected to ground with capacitors, because of the RTL8208’s special design.4. 2.5V Power GenerationThe RTL8208 uses a PNP transistor to generate 2.5V from the 3.3V power supply. This 2.5V provides for digital core and analog receive circuits. When designs require more than one RTL8208 chip (a system greater than 8 ports), do not use one PNP transistor for all of the RTL8208 chips even if the rating is sufficient. Use one PNP transistor for each RTL8208 chip.VDDAH: 3.3VVDDAL: 2.5V2SB1197K47uFUsing a PNP Transistor to Produce 2.5VDo not connect any beads directly between the collector of the PNP transistor and VDDAL. This will affect the stability of the 2.5V power significantly if a bead is used in this manner.2.5V power withoutbeadPNP 2SB1197KThe power transistor is a 2SB1197K, and follows the following specifications. Absolute maximum ratings (Ta=25°C)Parameter Symbol Limits Unit Collector-base voltage VCBO -40 V Collector-emitter voltage VCEO -32 V Emitter-base voltage VEBO -5 V Collector current IC -0.8 A(DC) Collector power dissipation PC 0.2 W Junction temperature Tj 150 °C Storage temperature Tstg -55~+150 °CFor more information, refer to 5. Layout Guidelines for 2-layer BoardSome experimentation can determine better layout guidelines to achieve good performance according to the characteristics of the RTL8208. The illustrations in this section describe some critical points on layout to improve chip and thus system performances. This section includes a feedback control signal, VCTRL, and MDC vs. X1 signal, and power vs. ground descriptions.5.1 VCTRL SignalVCTRL controls the current flow to stabilize 2.5V power. Any beads between the PNP collector and the RTL8208 will affect the internal feedback circuit adjusting current flowing through the VCTRL trace.Better designs will provide an uninterrupted signal trace for the VCTRL signal, with no vias between the PNP transistor and the RTL8208. Vias tend to appear and act like a choke to the current.VCTRL With Two Vias(worst case layout)5.2 MDC and X1 LayoutA great deal of transmit jitter will be created if the MDC interferes with the X1 (crystal) signal. This interference and jitter will cause CRC errors on the link partner receive path. It is strongly recommended to keep the MDC and X1 signal traces as far from each other as possible, and to keep the traces in a non-parallel configuration to avoid interference. This is especially important in a 2-layer board design. Removing the interfering source on clock will gain significant improvement in Tx jitter.Avoid Running Traces Parallel to the X1 SignalKeeping the MDC and X1 Traces Separated and Divergent5.3Power and GroundIt is not easy to implement a dual-voltage layout in a 2-layer board design. For the RTL8208, keeping a stable 2.5V power source is more important than the 3.3V power source when problems occur. However, a continuous and solid ground plane is also important to reduce power bouncing and thus improve signal integrity. Bulk capacitors for power traces and decoupling capacitors for each power pin of the RTL8208 are necessary. The decoupling capacitors should be as close as possible to the RTL8208 chip.5.3.1 2.5V PowerThe 2.5V power source determines data recovery performance and transmit jitter. As high as a 2ns transmit jitter may cause CRC errors on the link partner. For 2-layer board designs, a power-ring around the RTL8208 is used instead of a power plane, which is, in turn, used for a ground plane to reduce possible EMI and power bouncing. 47µF bulk capacitors are placed on the corners of this ring to support large current. 0.1µF decoupling capacitors are placed around, and as close as possible to the RTL8208. The 2.5V power-ring is on the top layer of the PCB as illustrated below. There are no beads on the ring to separate digital and analog power. Also, there are no beads between the PNP transistor and the power-ring.2.5V Power-ring with Two 47uF and 0.1uF Capacitors5.3.2 3.3V powerThe 3.3V power source determines the transmit waveform. This power source contributes less impact on the receiver of the link partner compared to transmit jitter, which is dominated by the 2.5V power.The illustration below shows the 3.3V power trace on the bottom side of the board, with bulk and decoupling capacitors.3.3V Power Trace5.3.3 GroundA continuous solid ground plane reduces EMI and power bouncing issues and creates better signal integrity and chip performance. As illustrated below, the ground plane lies beneath the RTL8208 on both the top and bottom layers of the PCB. Also, a ground ring around the RTL8208 is used to supply the decoupling capacitors with a current return path for both 2.5V and 3.3V power.Chip Ground Plane and Ground Ring5.4 REFCLKWhen RTL8208 uses 25MHz crystal or 25MHz OSC as clock source at pin 114 and works in 10Base-T mode, depending on loading and power on timing, some CRC/alignment error packets may be observed due to the timing skew. Descriptions:Systems designed based on 50MHz oscillator are immune to this problem.Since the problem is related to the internal timing when RTL8208 is power on. This problem can be reproduced and observed much easier by power-off/on the system several times. And then start packet transmission after power on each time to take sample. The setting on the packet generator is basically irrelevant. However, continuous stream of packet transmission may increase the rate of error packet observed.Analysis of the captured error packets consistently shows that the last bit of each error packet is corrupted by RTL8208. Further analysis shows that the REFCLK output from RTL8208 may determine whether the data transferred from the controller is correctly received by RTL8208.Workaround:To remove this problem for current version of RTL8208, an additional 15pF capacitor placed on the trace to REFCLK pin is required.1.The 15pF capacitor should be placed on the side closed to RTL8208, rather than controller/MAC side. And it musthave the precision of at least 10%. (Note: Maximum capacitance should be limited to 18pF. )2.It is recommended that damping resistor on REFCLK pin to be removed or replaced with 0-ohm resistor. Thedamping resistor may cause unnecessary setup/hold time issues depending on trace length of REFCLK output from RTL8208.Please find a simplified schematic below,Realtek Semiconductor Corp.Headquarters1F, No. 2, Industry East Road IX, Science-basedIndustrial Park, Hsinchu, 300, Taiwan, R.O.C.Tel : 886-3-5780211 Fax : 886-3-5776047WWW: 。