硬件分频电路

高质量七倍分频电路的设计与实现

高质量七倍分频电路的设计与实现作者:张继刚李维忠来源:《现代电子技术》2008年第06期摘要:提出一种可实现占空比为50%的7倍时钟分频电路的高可靠性设计方案,并分别给出由分立元件组构和由Verilog HDL语言描述的2种实现方法。

与已有方案相比,该设计不仅可以节省器件资源,而且完全避免了冒险现象对于分频时钟波形造成的影响。

在Quartus环境下,分别对门级设计和基于Verilog HDL语言的行为级描述进行仿真验证,结果显示该方案合理可行。

关键词:奇数次分频器;格雷码计数器;时钟波形;FPGA中图分类号:TN772 文献标识码:B文章编号:1004-373X(2008)06-012-02Design and Implementation of High Quality 1∶7 Frequency DividerZHANG Jigang,LI Weizhong(Inner Mongolia University of Technology,Huhhot,010051,China)Abstract:Design method of high-reliability 1∶7 clock frequency divider with half duty cycle is brought forward,and then implementation method based on separate component or described by Verilog HDL is paring with former design method,not only can the method economize on hardware resource,but it can be absolutely avoided that waveform of divided frequency clock is interfered by hazard in this method.After function of gate level design as well as behavior level design based on Verilog HDL is simulated in Quartus software,the method is proved logical and feasible as a result.Keywords:odd number frequency divider;Gary code counter;clock waveform;FPGA1 引言数字电路设计中常采用对主频时钟分频的方法产生所需的时钟。

单片机分频

单片机分频实现

单片机分频是指通过单片机对时钟信号进行分频操作,从而得到

不同的频率信号。

这种技术在很多领域中都有广泛的应用,比如无线

通信、数字音频、数字信号处理等。

实现单片机分频的方法很多,常见的有软件分频和硬件分频两种。

软件分频是指在程序中通过计数器来实现分频的功能,其优点是

实现简单、灵活性大,但缺点是会占用CPU的大量时间,并且容易受

到程序中其他模块的影响。

硬件分频是指在电路中通过特定的分频器

或者PLL电路来实现分频的功能,其优点是分频精度高,速度快,而

且可以同时输出多路分频信号,但缺点是需要特定的硬件电路支持。

在实际的应用中,我们需要根据具体的需求选择合适的分频方法。

同时,在软件分频中,我们需要优化程序以提高分频精度和效率。

例如,可以采用定时器中断的方式来实现分频,从而避免占用CPU过多

的时间。

总之,单片机分频技术是一个广泛应用的技术,对于实现高速、

高精度的信号处理、通信等应用领域有着重要的意义。

在具体的应用中,我们需要根据具体情况选择合适的分频方法,并进行相应的优化

和调试。

VHDL语言各种分频器的设计

硬件描述

使用VHDL,设计师可以描述电路 的结构、行为和功能,而无需关 心具体的物理实现细节。

设计层次

VHDL适用于不同层次的设计,从 门级到系统级,使得设计者可以 专注于设计逻辑而不是物理实现。

VHDL语言基本结构

实体

描述电路的输入和输出端口。

结构体

描述电路的内部逻辑和行为。

库

包含预定义的元件和函数。

end if;

end process;

8分频器设计

end Behavioral;

```

16分频器设计

16分频器:将输入频率降低到原来的 十六分之一。

VHDL代码实现

```vhdl

16分频器设计

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

03

if count = 3 then

4分频器设计

q <= '1';

count <= 0;

4分频器设计

01

else

02

q <= '0';

03

count <= count + 1;

4分频器设计

end if;

end if; end process;

4分频器设计

end Behavioral; ```

配置

指定实体和结构体的关联方式。

VHDL语言数据类型

标量类型

包括整数、实数、布尔等。

记录类型

组合不同数据类型的结构体。

向量类型

如位向量,用于表示位或字节。

数组类型

用Verilog语言实现奇数倍分频电路3分频5分频7分频

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

eda 7分频代码

eda 7分频代码

在 EDA(电子设计自动化)中,可以使用 Verilog 或 VHDL 等硬件描述语言来实现 7 分频电路。

以下是一个使用 Verilog 实现 7 分频的简单示例代码:

```verilog

module七分频( input clk, output clk_out );

reg [6:0] count;

reg clk_out;

always @(posedge clk) begin

if (count == 6'd6) begin

count <= 6'd0;

clk_out <= ~clk_out;

end else begin

count <= count + 1'd1;

end

end

endmodule

```

上述代码中,我们使用了一个计数器`count`来对输入时钟`clk`进行计数。

当计数器的值达到 6 时,我们将输出时钟`clk_out`取反,并将计数器重置为 0。

这样就实现了 7 分频的功能。

在实际应用中,可能需要根据具体的需求对代码进行修改。

例如,如果需要使用异步复位信号来重置计数器,可以添加一个复位信号`rst`,并在代码中添加相应的复位逻辑。

请注意,上述代码只是一个简单的示例,实际的 7 分频电路可能需要考虑更多的细节和优化。

在设计实际电路时,建议使用专业的 EDA 工具进行综合、仿真和验证,以确保电路的正确性和可靠性。

数字频率计分频电路的设计

f

=

1 (65536 ×n +

m)

× T R ×2 K

其中 : n 为溢出次数 , m 为最后一次计数值 , K CL K CL R CL K MOV C ,DOU T RLC A DJ NZ R0 ,RD - AD

RET

312 MAX7219 显示子程序 MAX7219 显示程序就是 89C51 在 CL K ( P212) ,

LOAD ( P210) 时序的配合下 , 通过 D IN ( P211) 向

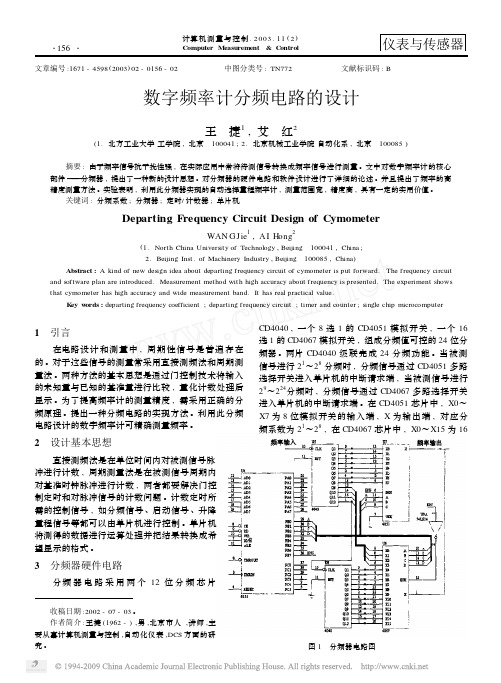

3 分频器硬件电路

分频 器 电 路 采 用 两 个 12 位 分 频 芯 片

CD4040 , 一个 8 选 1 的 CD4051 模拟开关 , 一个 16 选 1 的 CD4067 模拟开关 , 组成分频值可控的 24 位分 频器 。两片 CD4040 级联完成 24 分频功能 。当被测 信号进行 21~28 分频时 , 分频信号通过 CD4051 多路 选择开关进入单片机的中断请求端 , 当被测信号进行 29~224分频时 , 分频信号通过 CD4067 多路选择开关 进入单片机的中断请求端 。在 CD4051 芯片中 , X0~ X7 为 8 位模拟开关的输入端 , X 为输出端 , 对应分 频系数为 21~28 , 在 CD4067 芯片中 , X0~X15 为 16

4 分频原理

为了迅速确定分频系数 , 采用 16 位定时/ 计数器

进行定时计数 。方法如下 : 单片机内部定时计数器的

计数范围为 0~65535 。为保证测量精度 , 选择计数

分频器设计实验报告

分频器设计实验报告一、实验目的本次实验的主要目的是设计并实现一个分频器,以深入理解数字电路中频率分频的原理和实现方法,掌握相关的电路设计和调试技能。

二、实验原理分频器是一种数字电路,用于将输入的时钟信号的频率降低为原来的 1/N,其中 N 为分频系数。

常见的分频器有偶数分频器和奇数分频器。

偶数分频器的实现相对简单,可以通过计数器来实现。

当计数器计数值达到分频系数的一半时,输出信号翻转,从而实现偶数分频。

奇数分频器的实现则较为复杂,通常需要使用多个触发器和组合逻辑电路来实现。

在本次实验中,我们将分别设计一个偶数分频器(以 4 分频为例)和一个奇数分频器(以 3 分频为例)。

三、实验器材1、数字电路实验箱2、示波器3、逻辑分析仪4、集成电路芯片(如 74LS 系列芯片)四、实验步骤(一)4 分频器的设计与实现1、原理图设计使用 74LS161 四位二进制同步计数器作为核心器件。

将计数器的时钟输入端连接到输入时钟信号。

将计数器的输出端 Q2 和 Q0 通过与门连接到一个 D 触发器的时钟输入端。

将 D 触发器的输出端作为 4 分频器的输出。

2、硬件连接按照原理图在数字电路实验箱上进行芯片的插装和连线。

3、调试与测试输入一个频率稳定的时钟信号。

使用示波器观察输入时钟信号和输出分频信号的波形,验证是否实现了 4 分频。

(二)3 分频器的设计与实现1、原理图设计使用两个 D 触发器和一些组合逻辑门(如与门、或门等)来实现 3 分频。

第一个 D 触发器的输出作为第二个 D 触发器的输入。

通过组合逻辑门对两个 D 触发器的输出进行处理,得到 3 分频的输出信号。

2、硬件连接按照原理图在数字电路实验箱上进行芯片的插装和连线。

3、调试与测试输入一个频率稳定的时钟信号。

使用示波器观察输入时钟信号和输出分频信号的波形,验证是否实现了 3 分频。

五、实验结果(一)4 分频器实验结果通过示波器观察输入时钟信号和输出分频信号的波形,发现输出信号的频率为输入信号频率的 1/4,成功实现了 4 分频功能。

实验二 分频电路设计

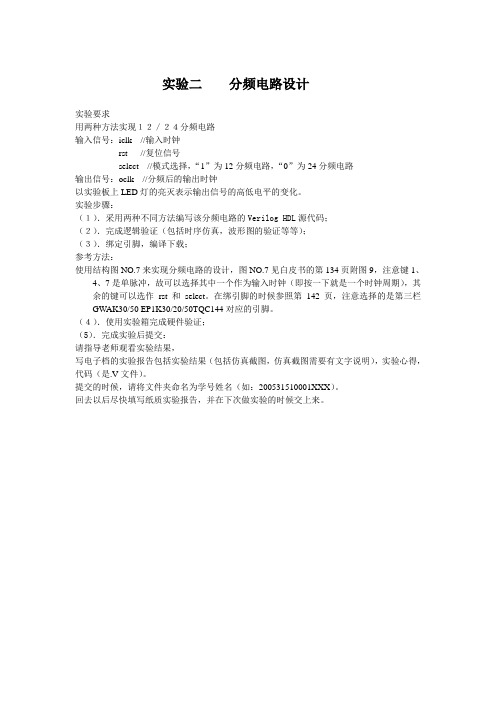

实验二分频电路设计

实验要求

用两种方法实现12/24分频电路

输入信号:iclk //输入时钟

rst_ //复位信号

select //模式选择,“1”为12分频电路,“0”为24分频电路

输出信号:oclk //分频后的输出时钟

以实验板上LED灯的亮灭表示输出信号的高低电平的变化。

实验步骤:

(1).采用两种不同方法编写该分频电路的Verilog HDL源代码;

(2).完成逻辑验证(包括时序仿真,波形图的验证等等);

(3).绑定引脚,编译下载;

参考方法:

使用结构图NO.7来实现分频电路的设计,图NO.7见白皮书的第134页附图9,注意键1、

4、7是单脉冲,故可以选择其中一个作为输入时钟(即按一下就是一个时钟周期),其

余的键可以选作rst和select。

在绑引脚的时候参照第142页,注意选择的是第三栏GW AK30/50 EP1K30/20/50TQC144对应的引脚。

(4).使用实验箱完成硬件验证;

(5).完成实验后提交:

请指导老师观看实验结果,

写电子档的实验报告包括实验结果(包括仿真截图,仿真截图需要有文字说明),实验心得,代码(是.V文件)。

提交的时候,请将文件夹命名为学号姓名(如:200531510001XXX)。

回去以后尽快填写纸质实验报告,并在下次做实验的时候交上来。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件分频电路

硬件分频电路是一种电子电路,用于将输入信号的频率减小至所

需的频率。

它被广泛应用于通信系统、音频系统以及数字系统等领域。

硬件分频电路的作用是通过将输入信号的周期延长来降低频率。

在这个过程中,输入信号经过一系列的分频器和计数器,以使输出信

号的频率满足特定的要求。

硬件分频电路通常由计数器、分频器、锁

存器和频率控制器等元件组成。

计数器是硬件分频电路中的关键元件之一。

它可以通过计数来确

定输入信号的周期,并将其送入分频器,以便进行分频。

计数器通常

由触发器和逻辑门组成,用于实现计数功能。

分频器则根据计数器的

输出进行分频,将输入信号的频率降低至所需的频率。

锁存器是另一个重要的元件,用于存储分频器的输出,并在需要

时将其提供给其他部件。

它可以通过控制信号来决定何时锁存,并在

锁存时将分频器的输出信号保存下来。

锁存器通常由触发器和开关组成,用于实现锁存功能。

频率控制器则用于调节硬件分频电路的输出频率。

它可以根据需要调节分频系数,以改变输出信号的频率。

频率控制器通常由可变电阻、电容或电感等元件组成,用于调节分频器的输入信号。

通过改变这些元件的值,可以实现对输出频率的精确控制。

总之,硬件分频电路是一种用于降低输入信号频率的电子电路。

它由计数器、分频器、锁存器和频率控制器等元件组成,通过计数、分频和锁存等过程,将输入信号的频率降低至所需的频率。

硬件分频电路在通信系统、音频系统以及数字系统等领域都有着广泛的应用。

通过合理设计和调节,可以实现对输入信号频率的精确控制。