基于c6455_DSP的中断设置

C6455基于BIOS的GPIO中断配置说明

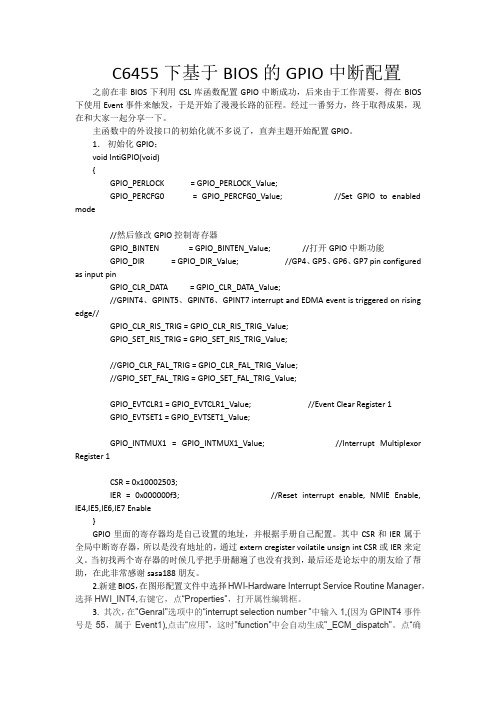

C6455下基于BIOS的GPIO中断配置之前在非BIOS下利用CSL库函数配置GPIO中断成功,后来由于工作需要,得在BIOS 下使用Event事件来触发,于是开始了漫漫长路的征程。

经过一番努力,终于取得成果,现在和大家一起分享一下。

主函数中的外设接口的初始化就不多说了,直奔主题开始配置GPIO。

1.初始化GPIO;void IntiGPIO(void){GPIO_PERLOCK = GPIO_PERLOCK_Value;GPIO_PERCFG0 = GPIO_PERCFG0_Value; //Set GPIO to enabled mode//然后修改GPIO控制寄存器GPIO_BINTEN = GPIO_BINTEN_Value; //打开GPIO中断功能GPIO_DIR = GPIO_DIR_Value; //GP4、GP5、GP6、GP7 pin configured as input pinGPIO_CLR_DATA = GPIO_CLR_DATA_Value;//GPINT4、GPINT5、GPINT6、GPINT7 interrupt and EDMA event is triggered on rising edge//GPIO_CLR_RIS_TRIG = GPIO_CLR_RIS_TRIG_Value;GPIO_SET_RIS_TRIG = GPIO_SET_RIS_TRIG_Value;//GPIO_CLR_FAL_TRIG = GPIO_CLR_FAL_TRIG_Value;//GPIO_SET_FAL_TRIG = GPIO_SET_FAL_TRIG_Value;GPIO_EVTCLR1 = GPIO_EVTCLR1_Value; //Event Clear Register 1GPIO_EVTSET1 = GPIO_EVTSET1_Value;GPIO_INTMUX1 = GPIO_INTMUX1_Value; //Interrupt Multiplexor Register 1CSR = 0x10002503;IER = 0x000000f3; //Reset interrupt enable, NMIE Enable, IE4,IE5,IE6,IE7 Enable}GPIO里面的寄存器均是自己设置的地址,并根据手册自己配置。

C6455初始化

6455初始化流程(DSP_FFT)第一步:首先设置PLL控制寄存器参考文档:SPRUE56,见附录2针对本例的设置如下,其他应用可参考。

PLLM_val = 20; 扩频20倍。

PREDIV_val =1; 预分频设置为1,不预分频。

PLLDIV4_val = 8; 设置输出4为8分频;PLLDIV5_val = 4; 设置输出5为4分频;以下是PLL初始化过程:1:CSR &=~(0x1);功能:关闭中断。

2:PLLCTL_1 &= ~(0x00000020);功能:PLLCTL第5位置0,使能PLLEN。

3:PLLCTL_1 &= ~(0x00000001);功能:设置为旁路模式。

4:for (i=0 ; i<100 ; i++);功能:执行空语句,根据要求等待4个最慢周期。

5:PLLCTL_1 |= 0x00000008;功能:写入PLLRST = 1。

6:PLLM_1 = PLLM_val - 1;功能:执行输入频率20倍频,在寄存器中的19代表20倍频,因此要减一。

7:PREDIV_1 = (PREDIV_val - 1) | 0x8000;功能:设置使能,同时设定预分频比例。

8:while( (PLLSTAT_1) & 0x00000001);功能:执行GO OPERATION是否完成的判断。

9:PLLDIV4_1 = (PLLDIV4_val - 1) | 0x8000;功能:设置输出4使能及设定分频比例。

10:PLLDIV5_1 = (PLLDIV5_val - 1) | 0x8000;功能:设置输出5使能及设定分频比例。

11:PLLCMD_1 |= 0x00000001;功能:开启GO OPERATION 状态。

12:while( (PLLSTAT_1) & 0x00000001);功能:检测GO OPERATION状态是否完成,即,检测赋值过程是否完成,因为GO OPERATION是赋值过程的标识。

基于TMS320C6455 DSP的PCI接口设计

第12卷 第1期 太赫兹科学与电子信息学报Vo1.12,No.1 2014年2月 Journal of Terahertz Science and Electronic Information Technology Feb.,2014 文章编号:2095-4980(2014)01-0136-05基于TMS320C6455 DSP的PCI接口设计熊 璐(中国电子科技集团公司 第10研究所,四川 成都 610036)摘 要:TMS320C6455是TI公司的一款高性能数字信号处理芯片(DSP),具有丰富的外部接口。

本文介绍了该芯片外围设备组件互连(PCI)接口控制器的性能特点,DSP内部的工作机制,地址映射方式,详细分析了2种工作方式的总线传输特点和性能,并给出了将其应用于卫星基带信号接收卡的设计实例。

通过使用TMS320C6455 DSP的PCI控制器简化了硬件接口设计,具有灵活高效的特点,已在工程应用中取得了良好效果。

关键词:TMS320C6455接口;外围设备组件互连;地址映射;总线传输;中断中图分类号:TN111文献标识码:A doi:10.11805/TKYDA201401.0136Peripheral Component Interconnect interface design based onTMS320C6455 Digital Signal ProcessingXIONG Lu(The 10th Research Inst. of the CETC,Chengdu Sichuan 610036,China)Abstract:TMS320C6455 is a kind of high-performance fixed-point Digital Signal Processing(DSP), which integrates various peripherals. This paper firstly introduces the features of the PeripheralComponent Interconnect(PCI) interface controller, the way to communicate with other modules in DSP andthe address mapping of slave/master work mode. Then bus transfer characteristics and performance of twowork modes is analyzed in detail and the application of its PCI interface controller on satellites basebandsignal receiver is also given. TMS320C6455’s PCI interface controller can simplify the hardware design,and have the characteristics of flexible and efficient, therefore it has good application prospects inengineering practice.Key words:TMS320C6455;Peripheral Component Interconnect;address mapping;bus transfer;interruptPCI总线是一种高性能局部总线,其数据总线为32 bit,可扩展为64 bit,最大数据传输速率为128 MBps~ 528 MBps。

基于TMS320C6455的DSP加载模式研究

基于TMS320C6455的DSP加载模式研究引言数字信号处理技术广泛应用于雷达、通信、图像处理等领域,其中有些信号处理运算量很大、算法结构复杂,且要求高速实时、高性能、灵活地完成各种处理任务。

近年来,以数字信号处理器(DSP)为基础的通用信号处理模块[1~5]的研制受到人们的重视,它的研制成功满足了信号处理系统实时性和通用性的要求。

由于在DSP程序运行前,都有程序加载的问题,尤其当信号处理模块由多DSP构成时,要充分考虑到上位机与DSP间、主DSP与从DSP间的加载关系,DSP也提供了多种灵活的加载方式以满足应用要求。

因此在设计通用信号处理模块前,有必要研究DSP的多种加载方式[6~8]。

TMS320C6455是世界上最大的DSP(数字信号处理)芯片商—TI(德州仪器)新推出的高端DS P芯片,也是目前单片处理能力最强的定点DSP。

与另一DSP芯片商ADI的高端产品TigerSHARC系列TS201相比:TS201时钟频率为600MHz,16位定点处理能力为4800MMAC/s;TMS320C6455时钟频率为1.2GHz,16位定点处理能力为9600MMAC/s。

可见,单片DSP的定点处理能力,TMS320 C6455强于TS201。

另外,ADI逐渐把精力投入到Blackfin系列DSP[9],TigerSHARC系列DSP不再升级;TI却仍在不断打造自己的高端市场,TMS320C6455后续产品也在不断跟进。

ADI的TigerSH ARC系列DSP拥有独特的link口,适合于构建多处理器平台。

在推出TMS320C6455以前,TI的DS P单片处理能力较强,但是芯片间的数据传输问题没有解决,构建多处理器平台比较复杂[10]。

但是新推出的TMS320C6455,采用了Serial RapidIO接口技术,互连速率每秒高达25Gbits,很好的解决了芯片间的数据传输问题,搭建多处理器平台变得简单方便。

(完整版)TMS320C6455高速SRIO接口设计

TMS320C6455高速SRIO接口设计引言数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国模拟器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片DSP 仍然显得力不从心。

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。

采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。

TI公司最新推出的高性能TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。

本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO 的数据通信和加载技术的软硬件设计与实现。

这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。

最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。

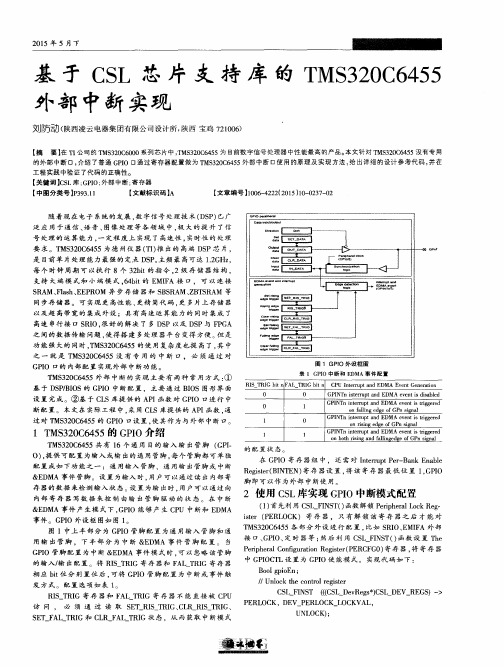

基于 CSL 芯片支持库的 TMS320C6455外部中断实现

o n b o t h i r s i n g a n d f a l l i n g e d g e o f GP n s i g n a l

的 配置 状 态。

O) , 提 供 可 配 置 为输 入 或 输 出的 通 用 管 脚 。 每 个 管脚 都 可 单独

图1 GP l O 外设框 图

表 l GP I O中断和 E DMA 事 件 配 置

RI S

_

T M ¥ 3 2 0 C 6 4 5 5外 部 中 断 的 实现 主要 有 两种 常 用 方 式 : ①

基于D S P / B 1 0 S的 G P I O 中 断 配 置 .主 要 通 过 B I O S图形 界 面

高速 串行 接 口 S R1 0. 很 好 的 解 决 了 多 DS P以及 Ds P与 F P GA

之 间 的数 据 传 输 问题 , 使得 搭 建 多处 理 器 平 台 变得 方便 。 但 是 功能 强大的同时, T M¥ 3 2 0 C 6 4 5 5的 使 用 复 杂 度 也提 高 了 , 其中 之一就是 T M¥ 3 2 0 C 6 4 5 5没 有 专 用 的 中 断 口 。 必 须 通 过 对 G P I O 1 2 " 的 内部 配 置 实现 外 部 中断 功 能

配置 成 如 下功 能 之 一 : 通 用 输入 管脚 、 通 用 输 出管 脚 或 中 断

T R I G b i t n l F A L _ T R I G b i t n C P U I n t e r r u p t a n d E D M A E v e n t G e n e r a t i o n

0 O

l 1

设置 完成 。② 基于 C L S库提供 的 A P I函数对 G P I O 口进行 中

DSP中断设置简明教程(精)

DSP中断设置简明教程(精)[DSP+ARM] [转载]DSP中断设置简明教程定时器, 工作, 寄存器, 通用, 程序一、简述本文介绍TMS320C6000系列中断设置的简明方法。

通过示例定时器中断,MCBSP串口接收中断及外部中断这三种中断实现过程,介绍如何实现中断各个寄存器的配置,中断向量表书写以及中断服务函数。

最后提供一个简要的示例程序可供大家下载使用。

此示例在DSK6416的TI官方实验板上通过测试。

由于定时器和串口工作模式较繁,因此对中断无关部分不做介绍。

二、实现DSP中断需要做哪些通用工作设置允许哪些非屏蔽中断设置各个允许的非屏蔽中断的中断来源设置开启总中断设计中断向量表将中断向量表通过cmd文件挂载到指令内存提供中断处理函数如果中断向量表首地址挂载的不是0地址,那么需要设置中断向量表地址寄存器对于不同的中断源,需要做各个自己的工作,比如如果是外部中断,那么需要设置管脚极性,即由高->低产生中断抑或反之。

为了照顾知识较少的读者,下面将从一个新工程出发,引导大家建立一个中断示例程序。

如果您对建立工程很熟悉,可以跳过此步。

三、建立新工程1.点击Project->New,设置Project Name为intexample,Project Type为Executable,Target选择您需要的器件,在此由于本人使用的是DSK6416评估板。

因此选择TMS320C64XX。

2.添加标准库rts6400.lib,以便自动产生c_int00等函数。

右击当前工程,选择“Add Files to Project”,选择库所在路径,一般为CCS 安装自带,可参考本CCS3.1版本的路径地址:CCStudio_v3.1C6000cgtoolslibrts6400.lib如果您使用的是其他器件类型,请在lib文件夹内选择其他器件库。

添加源文件,选择File->New->Source File,保存为main.c到工程路径下。

C54x+DSP混合编程及中断的C语言实现

!"# $%&#’ ()*+,)+# -./+.)00%*+ )*’ 1"# 2*1#..,31 4#)5%6)1%/* %* 7 ()*+,)+# 8/. ’ 7*+ & 9:$;(< => 8 ?@. , A(# ;B@C 8 DE>/

( . ! "#$%&’ ()*#$’+ ,’#-&./#01, "#$%&’ 12.33* , 23#’$; / ! 45.03&$/0 6#7.5&8&70.5’#7/ 9’/0#0)0&, :3&’1$’+ ..331/ , 23#’$)

0 ,期

陈丽安等: ’ !"#$ %&’ 混合编程及中断的 ! 语言实现

・ " ,・

在 ! 语言程序中可以直接插入 %&’ 的汇编指 令, 格式如下: ()*( “ 汇编指令” ) ; 用这种方式可在 ! 程序中直接修改 %&’ 寄存 器值或实现一些硬件控制功能。但要特别注意不能 破坏 ! 的运行环境。 (+) 手工修改 ! 程序编译后所生成的汇编代码 通过控制编译器, 由 ! 程序可生成具有交叉列 表的汇编程序。手工修改该程序并进行汇编, 产生 目标文件。用这种方法也应注意不能破坏 ! 的运 行环境。 (,) 在 ! 程序中调用 %&’ 的内联函数 -.&,+/!"#$ %&’ 的 ! 编译器支持内联函数的 功能。内联函数实为 %&’ 的特殊函数, 在 ! 程序中 调用时, 函数名前需加下划线。举例如下: 0 0 0 0 12345678 9 23:;2378<)= > ? 23: $+ , $, , @; 5A3B $C ; @ D E)*(4; ( $C , $+ , $, ) ;

TMS320C6455高速SRIO接口设计

TMS320C6455高速SRIO接口设计引言数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国模拟器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片DSP 仍然显得力不从心。

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。

采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。

TI公司最新推出的高性能TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。

本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO 的数据通信和加载技术的软硬件设计与实现。

这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。

最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。

TMS320C6455外部中断实现 浅谈外部中断的使用

TMS320C6455外部中断实现浅谈外部中断的使用本文主要是关于TMS320C6455的相关介绍,并着重对TMS320C6455外部中断实现进行了详尽的阐述。

TMS320C6455TMS320C6455是TI公司推出的的一款新型高性能单核定点DSP.它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品,在通信,医疗图像,无线传输方面都可以大有作为.TMS320C6455主频达到了1GHz,1ns的指令周期.每周期执行8条32位指令,最大峰值速度达到8000MIPS.这意味着.在1G时钟频率下,8000个16位“16位的MACs能在1秒钟发生.TMS320C6455还带有Seria/RapidlOfr)总线,互连速率每秒高达25Gbits,实现了极高的多处理性能,降低了系统消耗,比此前的外部存储器接口快12倍,这使得多DSP级连变得十分方便.TMS320CC6455片内是基于C64xx内核的L1/L2存储结构.片上集成有大量的存储空间.L1P为32K字节,L1D 为32K字节L2为2M字节、比此前C64x器的存储器容量件翻一番,其中L1P和L2都可直接映射到存储空间。

TMS320C6455的外围总线包括:一个内部集成电路总线(I2C).两个多路缓冲串口总线fMcBSPs),两个64位通用定时器(可以配置成4个32位定时器),一个可配置的16位或32位主机接口(HPI6/HPI32).一个PCI总线,一个16管脚的通用输入/输出端口(GPIO),一个10/100/1000M 以太网媒体访问控制器(EMAC)。

一个无缝外部存储器接口(64一bit EMIFA),一个32位DDR2 SDRAM接口。

C6455由于自带千兆EMAC,外接PHY物理层芯片即可实现一个千兆以太网口。

千兆以太网的实现使得C6455嵌入式处理器与台式机等设备的数据传输变得异常方便。

TI为C6455等处理器提供了NDK(Network Develop Kit),通过NDK的使用可以简化C6455中TCP/IP或者UDP等数据传输协议的实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于C6455_DSP的中断设置

一、中断概述

6455DSP提供了复位中断,NMI中断和可屏蔽中断。

RESET 是优先级最高的中断,它连接到外部的RESET/管脚,非屏蔽中断。

复位是最高优先级的中断,用来将CPU 返回到固定的状态。

复位是一个低有效信号,所有别的中断信号是高有效。

为了使CPU 正确的初始化,复位低电平必须保持10 个时钟周期。

正在执行的指令停止,寄存器回到默认状态复位的ISFP 必须在地址“0”

NMI 为第二优先级的中断,它对应外部的NMI 管脚。

要使能NMI 中断,需将IER 中的NMIE 位置“1”,跳转的延迟等待会阻止NMI 中断的进程。

复位时NMIE 被清“0”,当NMI 产生时,NMIE 被清“0”,手动无法清除NMIE,但可以设置NMIE 来允许中断嵌套。

INT4-INT15 为较低优先级的中断(INT15 优先级为最低)。

6455DSP提供了128个中断源,通过中断选择器,组合器等分配给12个可用中断号。

二、常用中断寄存器

常用的中断寄存器包括中断多路复用寄存器(INTMUX n),中断状态控制寄存器(CSR),中断使能寄存器(IER),中断清除寄存器(ICR),中断服务表指针寄存器(ISTP)。

INTMUXn用来将128个中断源分配给12个中断号,6455有3个INTMUX。

每个INTMUX对应4个中断号。

CSR用来控制全局中断的使能与否,当其最低位GIE为1时,使能全局中断。

IER寄存器用来使能对应中断号,

ICR寄存器用来清除中断事件标志。

三、中断的使用

1、NMI中断。

设置IER寄存器中的NMIE为1,来使能NMI中断。

2、可屏蔽中断的使用。

使用可屏蔽中断包括3个主要部分,中断函数,中断向量表,及中断向量表所对应的段。

可屏蔽中断的使用步骤:(1)设置INTMUXn,将中断源与中断号绑定。

(2)

设置ICR清除中断标志寄存器,(3)设置IER使能相应的中断号。

(4)设置CSR 使能全局中断。

3、中断函数

中断函数要以interrupt开头作为标识。

4、中断向量表

要实现正确的中断响应,中断向量表是必不可少的一部分。

中断向量表的格式如下。

程序执行中断时会参考中断向量表,中断向量表中包含中断服务程序的指令包,每个中断服务指令包包含8条指令。

在设置中断向量表时,当语句不足8条时,应该以nop语句填充补足8条语句。

unused .macro id

.global unused:id:

unused:id:

b unused:id: ; nested branches to block interrupts

nop 4

b unused:id:

nop

nop

nop

nop

nop

.endm

.sect ".vectors" ;为中断向量定义一个命名段

.ref _c_int00 ; C entry point

.ref _timer0_isr ;中断函数的入口

.align 32*8*4 ; must be aligned on 256 word boundary

RESET: ; reset vector;复位引起的中断mvkl _c_int00,b0 ; load destination function address to b0

mvkh _c_int00,b0

b b0 ; start branch to destination function

;mvc PCE1,b0 ; address of interrupt vectors

; mvc b0,ISTP ; set table to point here

nop 3 ; fill delay slot

nop

nop

nop

nop

;

; plug unused interrupts with infinite loops to

; catch stray interrupts

;

unused 1

unused 2

unused 3

unused 4

unused 5

unused 6

unused 7

unused 8

unused 9

unused 10

unused 11

INT12:

mvkl _timer0_isr,b0 ; load destination function address to b0

mvkh _timer0_isr,b0

b b0 ; start branch to destination function

;mvc PCE1,b0 ; address of interrupt vectors

; mvc b0,ISTP ; set table to point here

nop 3 ; fill delay slot

nop

nop

nop

nop

unused 13

unused 14

unused 15

在中断向量表中,一般

5、cmd文件的修改

中断向量表中有vectors段,在cmd文件中要为vectors设置对应的数据空间。