重庆大学数字电子技术试卷2007-2008(1)答案

数字电子技术参考答案

数字电子技术试卷(1)参考答案一.填空1. 1111011,7B2. 8613. 与,或,非 4. 0,1,高阻5. 真值表,逻辑图,逻辑表达式,卡诺图,波形图(时序图) 6. 波形的整形 7. 20伏8. 并行A/D ,串并行A/D ,逐次比较A/D ,双积分A/D (写出三种) 二.判断题1.× 2.√ 3.× 4.√ 5.√三.化简逻辑函数1.D B A Y +=-2.--+=D B A Y四.C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.AQ Q Qn +=-+1,A Q n =+1六.采用D 触发器,-=122Q Q D ,--=231Q Q D ,1230Q Q Q D -+=电路图略。

将非工作状态101,110,111带入方程得次态,101→001,110→101→001, 111→001,电路可以自启动。

七.f =65Hz数字电子技术(2)参考答案 一.填空题(16)1. 100011.110,23.C 2. 0,13. 当前输入,原状态4. 0,1,高阻;任何时候,只能有1个三态门被选通。

5. 有两个稳态,在触发信号作用下状态可相互转变,有记忆功能 6. 延时 7. 5.5v 8. 13二.判断题(10)1.√ 2.× 3.×4.√ 5.√三.化简题(14)1. B Y =2. -++=D A C B Y 四.(15)CD A B A Y --+= 五.(15)--+=B A Qn 11, Q B Q A Qn ---++=21六.(15)驱动方程:1,121=⊕=-K Q X J ,1,212=⊕=K Q X J逻辑功能:X=0时,同步三进制计数器;X =1时,同步三进制减法计数器。

该电路为同步三进制可逆计数器,并且能自启动。

七.(15)数字电子答案3 一.填空题(16)1. 1010110,100001102. 7 3. 16,64. 状态转换表,状态转换图,特性方程5. 06. 256×4bit 7. 5.275伏8. 转换精度,转换速度二.回答问题(10)1. 不正确。

数字电子技术测试试卷与答案精选全文完整版

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

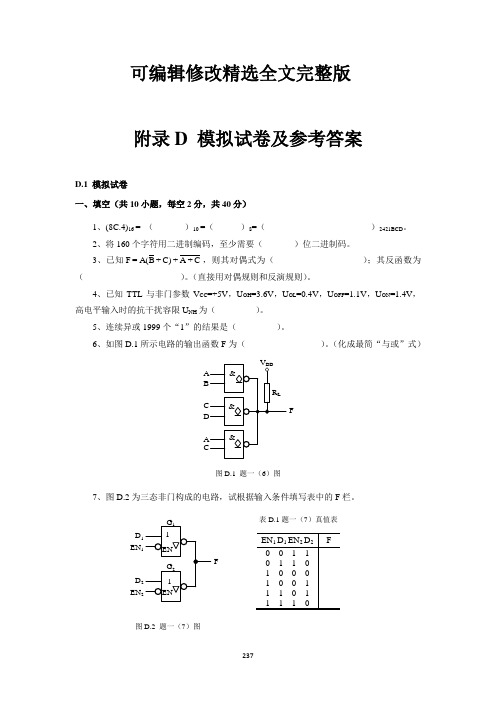

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

(NEW)重庆大学光电工程学院《832电子技术一(含模拟电路、数字电路)》历年考研真题汇编

目 录2002年重庆大学584电子技术(1)(含模拟电路、数字电路)考研真题2003年重庆大学471电子技术(1)考研真题2004年重庆大学474电子技术1(含模拟和数字电子技术)考研真题2005年重庆大学474电子技术1(含模拟和数字电子技术)考研真题2006年重庆大学433电子技术(含模拟电路、数字电路)考研真题2007年重庆大学442电子技术1(含模拟电子技术和数字电子技术)考研真题2008年重庆大学841电子技术1(含模拟电子技术和数字电子技术)考研真题2009年重庆大学841电子技术1(含模拟电子技术和数字电子技术)考研真题2010年重庆大学832电子技术一(含模拟电路、数字电路)考研真题2011年重庆大学832电子技术一(含模拟电路、数字电路)考研真题2012年重庆大学832电子技术一(含模拟电路、数字电路)考研真题2013年重庆大学832电子技术(含模拟电路、数字电路)考研真题2014年重庆大学832电子技术一(含模拟电路、数字电路)考研真题2015年重庆大学832电子技术(含模拟电路、数字电路)考研真题2002年重庆大学584电子技术(1)(含模拟电路、数字电路)考研真题2003年重庆大学471电子技术(1)考研真题一、各三极管3个电极对地电位如图一所示,判断各管所处的状态。

(15分)图题一二、放大电路如图题二所示,已知,,,,,试求:(1)电路的Q点;(2)电压增益、输入电阻及输出电阻;(3)若,求。

(20分)图题二三、分析图题三电路,要求:(20分)1.判断电路的级间反馈的极性及组态;2.说明反馈对电路的输入电阻,输出电阻有何影响(增大或减小);3.在深度负反馈条件下,推出电流的计算式。

图题三四、在题图四所示电路中,设、为理想运放,、为理想二极管。

(20分)1.写出与的关系式;画出相应的电压传输特性曲线(不考虑运放最大输出电压范围对的限制);2.若输入电压为正弦波,即,试画出与对应的波形。

数字电子技术试卷和问题详解

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.100001100001是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为。

8.实现A/D 转换的主要方法有 , , 。

二.判断题(10)1.BCD 码即8421码 ( 错 )2.八位二进制数可以表示256种不同状态。

( 对 )3.TTL 与非门与CMOS 与非门的逻辑功能不一样。

( )4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。

(对 )5.计数器可作分频器。

( 对 )三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1 六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

数字电子技术试卷答案

<<数字电子技术>>试卷(2007.1)A(答案)一. 单项选择题:〔在每题的备选答案中选出一个正确的答案,并将正确答案的字母填入下表中对应的格子里。

每题2分,共20分。

〕(每题2分,共20分)1.CMOS传输门的静态功耗特别小,当输入信号的频率增加时,其功耗将增大。

真值表、逻辑电路图、逻辑函数式、卡诺图。

3.逻辑电路中,高电平用1表示,低电平用0表示,那么称为正逻辑;4. 把JK触发器改成T触发器的方法是J=K=T。

5.组合逻辑电路是指电路的输出仅由当前的输入确定。

6.5变量输入译码器,其译码输出信号最多应有32个。

7.输入信号的同时跳变引起输出端产生尖峰脉冲的现象叫做竞争-冒险现象。

8.一片ROM有10根地址线,8根数据输出线,ROM共有8192个存储单元。

9.N个触发器组成的计数器最多可以组成2n进制的计数器。

8.根本RS触发器的约束条件是RS=0。

三.电路分析题〔36分〕1.图3-1(a)所示电路,移位存放器原来的数据是,数据从Di依次输入到移位存放器,试问:在图3-1(b)所示输入波形作用下,在T1到T2期间,输出端X、Y的波形? 〔12分〕(1)2.图3-2为两个时钟发生器,图中R1=510Ω, R2=10KΩ,C=0.1uF。

〔12分〕〔1〕写出触发器的状态方程及输出V1、V2的方程;〔2〕画出555定时器的输出VO 以及V1、V2的波形;〔3〕计算V1的周期和脉冲宽度Tw.〔1〕,〔2〕〔3〕3.双积分A/D转换器如图3-3所示,试答复以下问题:〔12分〕(1)假设被测电压Vi的最大值为2V, 要求可分辩的电压小于0.1mV, 问二进制计数器是多少位的?(2)假设时钟脉冲频率为200kHz, 那么对Vi进展采样的时间T1为多长?(3)假设时钟脉冲频率为200kHz, , ,输出电压Vo的最大值为5V, 积分时间常数是多少?(1),所以(2)(3), 所以四.电路设计题(24分)1〕试用一片双4选1的数据选择器74LS153和必要的门电路,设计下面逻辑函数,并在器件图上画出相应的电路图。

数字电子技术基础A卷参考答案及评标

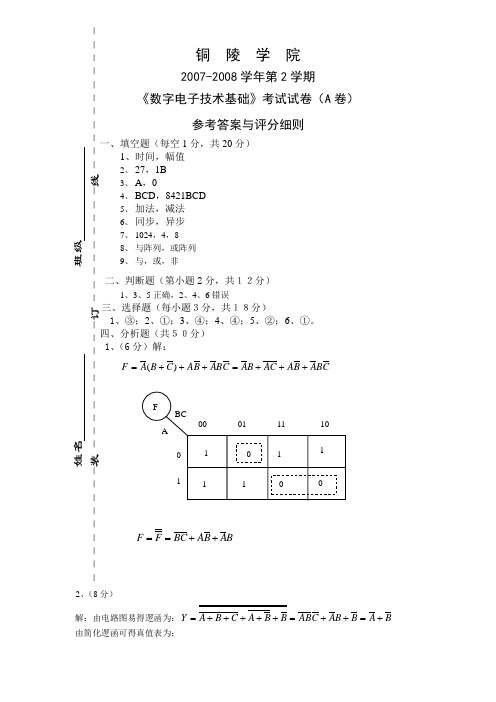

铜 陵 学 院2007-2008学年第2学期《数字电子技术基础》考试试卷(A 卷)参考答案与评分细则一、填空题(每空1分,共20分)1、时间,幅值2、 27,1B3、 A ,04、 BCD ,8421BCD5、 加法,减法6、 同步,异步7、 1024,4,8 8、 与阵列,或阵列 9、 与,或,非二、判断题(第小题2分,共12分)1、3、5正确,2、4、6错误三、选择题(每小题3分,共18分)1、③;2、①;3、④;4、④;5、②;6、①。

四、分析题(共50分) 1、(6分)解: C B A B A C A B A C B A B A C B A F +++=+++=)(B A B AC B F F ++==2、(8分)解:由电路图易得逻函为:B A B B A C B A B B A C B A Y +=++=+++++= 由简化逻函可得真值表为:00 01 11 100 1ABCF 1 1110 1姓名 班级 ―――――――――装――――――――――订―――――――――线―――――――――――0100 0101 0110 0111 100010011010101111001101111011110000 0001 0010 0011 A B Y 0 0 1 0 1 1 1 0 1 1 1显然,该电路具有与非逻辑功能。

3、(6分) 解: 4、(6分)解:解:八选一数据选择器的出入关系为:126012501240123012201210120012A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y +++++++=需实现的逻函表达式为:C B A C B A ACZ ++=若令Z Y D D C A B A A A i =====,,,,012,则比较以上两表达式易知:0,164307521========D D D D D D D D 。

重庆大学数电试卷合集

重庆大学《数字电子技术(Ⅱ)》课程试卷2012 ~2013 学年第 2 学期开课学院:电气工程学院课程号:考试日期: 2013-6考试方式:考试时间: 120 分钟一、设计题(20分):采用同步置数的方式,利用74LS160设计365进制的计数器,各位之间为十进制关系。

解:二、分析题(20分):下图为16×4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

在CLK信号作用下,输出波形如图所示。

计算ROM中的数据表。

解:三、设计题(10分):用D触发器设计一个同步串行数据检测电路,当连续输入3个或3个以上1时,电路的输出为1,其它情况下输出为0。

例如:输入A 101100111011110输出Y 000000001000110解:1)画出原始状态图2)状态化简3)状态编码原始状态图化简以后的状态图1/0A/Y0/01/00/0由状态图可得到复合卡诺图图:n AQ Y 1=nn n n n n Q Q A Q AQ AQ Q 01101011⋅=+=++D 触发器的特性方程为1,01==+i D Q in i得:n n n n QQ A D AQ AQ D 010101⋅=+=5) 检查自启动:可以自启动。

6)画逻辑图四、分析题(10分): 试分析下图时序电路的功能。

解:1))()()(2101201110210↓=↓=↓⋅=+++CP Q Q Q Q Q Q Q CP Q Q Q nn n n n n n nn2) 画出波形图:(略) 3) 画出状态图异步五进制加法计数器1Q的卡诺图 nn Q Q 01 00 01 11 10 A 0 1nn Q Q 01 00 01 11 10 A 0 110+n Q的卡诺图1/00/0nn Q Q 01 00 01 11 10 A 01nn Q Q 01 00 01 11 10 A 0 1输出Y 的卡诺图五、分析题(10分)利用计算公式解释超前进位加法器的基本思想。

数字电子技术期末试卷

重庆大学数字电子技术I (双语)课程试卷2006~2007 学年 第2学期开课学院:通信工程学院课程号:考试日期:考试方式:考试时间: 120 分钟注:1.大标题用四号宋体、小标题及正文推荐用小四号宋体;2.按A4纸缩小打印I. Multiple choice (1 pts/ea, 15 pts total)1) How is the invalid state problem associated with the S -R flip -flop overcome? a) The R terminal is eliminated. b) The R input is fed through an inverter. c) A single input terminal is used (D). d) Both B and C are correct.2) This is the timing diagram for a 2-input ________ gate.a) NAND b) AND c) Exclusive-OR d) OR 3) What is the meaning of RAM, and what is its primary role?a) R andom A ccess M emory; it is memory that is used for short-term temporary data storage within the computer.b) R eadily A vailable M emory; it is the first level of memory used by the computer in all of its operations.c) R andom A ccess M emory; it is memory that can be reached by any sub-system within a computer, and at any time.d) R esettable A utomatic M emory; it is memory that can be used and then automatically reset, or cleared, after being read from or written to..4) Which rule of Boolean algebra does the example below represent?a) A + 1 = 1 b) A ∙ 0 = 0 c) A + 0 = A d) A ∙ 1 = A5) The circuit shown below is ________.a) decade counter b) BCD counter c) Johnson counter d) ring counter 6) The circuit below is most likely a ________.a) full-adder b) demultiplexer c) multiplexer d) comparator7) For a negative-logic pulse, the trailing edge is the ________. a) negative-going edge b) positive-going edge c) HIGH-to-LOW transition d) falling edge 8) The 2's complement of binary 110110 is ________.a) 0010012 b) 0010102 c) 1101002 d) 10101029) Which of the following statements best describes the operation of an UP/DOWN SYNCHRONOUS COUNTER?a) The counter can be reversed, but must be RESET before counting in the other direction.b) In general, the counter can be reversed at any point in its counting sequence.c) The counter can count in either direction, but must continue in that direction once started.d) The count sequence cannot be reversed, once it has begun, without first resetting the counter to zero. 命题人:组题人:审题人:命题时间:教务处制学院 专业、班 年级 学号 姓名公平竞争、诚实守信、严肃考纪、拒绝作弊封线密Figure 5-110) Which of the following logic expressions represents the logic diagram in Fig 5-1? a) AB B A X += b) B A AB X += c) B A B A X += d) AB AB X += 11) For an ideal digital pulse, transition times are ________. a) infinite; b) measured between 0 and 90% of the amplitude; c) measured between 10% to 90% of the amplitude; d) zero;12) When performing binary addition using the 2's complement method, an________ can occur if ________ are of the same ________; the error is indicated by a(n) ______. a) overflow, both numbers, sign, incorrect sign bit b) error, both numbers, magnitude, negative sign c) overflow, signs, magnitude, incorrect sum d) error, the signs, polarity, incorrect polarity13) Which of the following combinations cannot be combined into Karnaugh -map groups? a) Corners in the same column; b) Corners in the same row; c) Overlapping combinations; d) Diagonal corners;14) A positive edge-triggered J-K flip-flop is used to produce a two-phase clock. However, when the circuit is operated it produces erratic results. Close examination with a scope reveals the presence of glitches. What causes the glitches, and how might the problem be corrected?a) The PRESET and CLEAR terminals may have been left floating; they shouldbe properly terminated if not being used.b) The problem is caused by a race condition between the J and K inputs; aninverter should be inserted in one of the terminals to correct the problem. c) A race condition exists between the Q and Q outputs to the AND gate; theAND gate should be replaced with a NAND gate.d) A race condition exists between the CLOCK and the outputs of the flip-flopfeeding the AND gate; replace the flip-flop with a negative edge-triggered J-K flip-flop.15) When both inputs of a J -K edge -triggered FF are high, and the clock cycles, the output will a) not change; b) toggle;c) remain unchanged; d) be invalidII. Compute and fill in the blank (3 pts/ea, 30 pts total)1) How many input lines would be required for a 1-of-8 decoder?2) Suppose that a 3-digit BCD digital-to-analog converter has a full-scale output of 49.95 mA. What is the percentage resolution of the DAC?3) With current technology, a 12-bit flash A/D converter would require __________ comparators.4) How many truth table entries are necessary for a 4 input circuit? 5) Given the Boolean expression )(G D LMN X += and the values L=1, M=0, N=1, D=1, and G=0, the value of X is:6) A retriggerable one-shot has a pulse width of 10mS; 3mS after being triggered, another trigger pulse is applied. The resulting output pulse will be ________ ms 7) The equation for the output frequency of a 555 timer operating in the astable mode is: f = 1.44/((R1 + 2*R2)*C). What value of C will be required if R1 = R2 = 1K and f = 1KHz?8) A certain IC logic gate draws 1.8 mA when its output is HIGH and 3.8 mA when its output is LOW. Assume a 50% duty cycle and calculate the average I cc current drain.9) A certain logic device has the following specifications: V OL(max) = 0.5 v, V IL(max) = 0.9 v, V OH(min) = 2.6, and V IH(min) = 2.1 v. Determine the low-state dc noise marginFigure 8-910) What is the modulus of the counter shown in Figure 8-9?III. for the circuit below, plot each output waveform for the inputs shown.(5 pts)IV. If the input waveforms are applied to the circuit below, sketch the output waveform (5 pts)V. Design a 7-segment decoder logic for segment a.(12 pts)VI. Design a counter to produce the following binary sequence. Use J-K flip-flops. (15 pts)0, 9, 1, 8, 2, 7, 3, 6, 4, 5, 0,…for truncated states, check auto-reentry property.VII. A 555 timer is configured to run as an astable multivibrator as shown below, determine following parameters: (8 pts)Given: R1R2C = 15.4 pFFind: f, t H, t L, Duty cycleVIII. The shift register is given below, the SER is a 0. develop data-output waveform in relation to the input. (5 pts)IX. Draw output waveform. The data inputs have a low value of 0V and a high value of +5V. (5 pts)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

2

4

7

七、 (12 分)

利用 Q3Q2Q1Q0 的 0111 状态置零,故置零端 的逻辑关系为

。

0000

0001

0111

0110 0101

0010 0100

0011

(4 分) 状态转换图为: Q3Q2Q1Q0(6 分)

能自启动(2 分) 七、(12 分)

同步计数器

1111 1110 1101 1100 1000 1001 1010 1011

STB STC STA

Ci-1 Bi Ai

1

C i

A B C i i i1

A B C i i i1

A B C i i i1

A B C i i i1

(Y Y Y Y )

3

5

6

7

S i

A B C i i i1

A B C i i i1

A B C i i i1

A B C i i i1

(Y Y Y Y )

1、√ 2、 √ 3、 √ 4、 × 5、 ×

6、× 7、 × 8、 × 9、 √ 10、 ×

三、用卡诺图法化简函数,写出它们的最简与或表达式。(各 4 分,共 12 分)

1. Y AB BC CD 1

2. Y BD AC ABD 2

3.

Y ABC BCD ABC BCD

四

3

、请根据题图和题表, 完成以下要求:(14 分)

驱动方程:F1: J X Q Q X Q Q , K 1;(2 分)

1

12

12

1

F2:

J K Q

2

2

1

(2 分)

输出方程: Z CP Q Q (2 分)

1

2

1234

5

6 78 9

CP

X

0

1

Q1 0

Q2 0

Z

(6 分)

八、(10 分) 1.完善电路图(4 分),电压传输特性(3 分)。2.输出波形。(3 分)

答案:

VCC

+9V

DIS

84

uo

ui

7

3

TH

6

TL

2

5

CV

1

GND

六、列写全加器的真值表(3 分),输出函数的最小项表达式(3 分),在译码器 74LS138 上连线、标注 (6 分)

Ai

Bi

Ci-1

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

11Leabharlann 0011

1

1

1

1

Si

Ci

Ci &

& Ci

&

&

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

A0 A1 A2

数字电子技术 2007-2008(一)课程试卷 B 卷 答案

一、填空题(每空 1 分,共 10 分)

1、 10100 ; 24 ;

B A(C D) ( A B)C D 2、

3、 高阻 ;4、 双稳态 ; 5、 8K 或 213 。

6、 门电路 ;触发器 ; 7、 16 8、 高

二、判断题(每题 1 分,共 10 分)

表和图中填充的内容各 1 分;

F1

F2

F3 F4

F5

&

1 =1

=1 1

VCC

F6

R F7

A B C D

表1

F1

F2

F3

F4

1

2

1

0

1

0

五、 (8 分)

(1) Z AD AC BCD

F5

F6

F7

OC 或 OD 三态门 门

0

0

0

共有三种情况可以通过议案:A、C 同意;A、D 同意;B、C、D 同意(6 分); (2)A 的权力最大(2 分)