数模混合仿真详细文档

SpectreVerilog软件做数模混合仿真简单教程

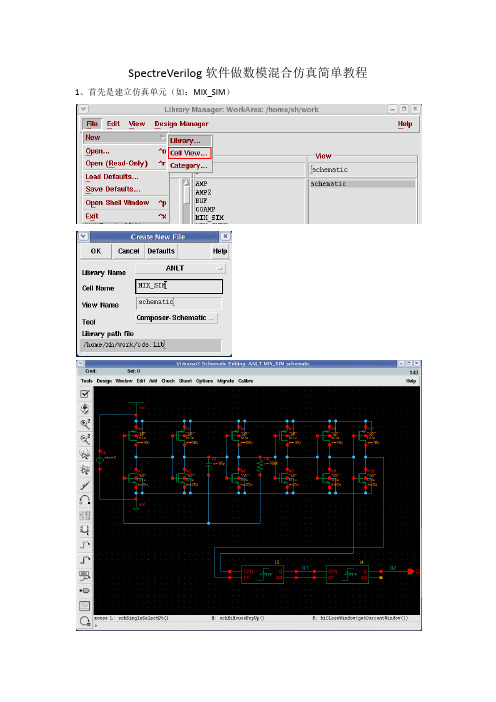

SpectreVerilog软件做数模混合仿真简单教程1、首先是建立仿真单元(如:MIX_SIM)

2、建立config文件,如下图所示,点击OK。

在出现下图表中点击Browse,选择好cell的View=schematic,然后点击OK

然后分别按下面图示操作。

3、打开MIX_SIM的config文件,如下图所示。

4、设置模数转换以及数模转换接口,注意下图所示的设置方法要求数模模数转换接口处用的是functional,设置才有效。

5、打开模拟仿真器,选择模拟软件工具为SpectreVerilog,并填好用于仿真的目录。

6、选择仿真模型库

7、如果需要添加仿真激励信号,按下图操作,加入激励信号,保存退出。

8、选择仿真模式,瞬态仿真的话填入仿真时间以及步长设定。

9、选择探测信号,接着选择出网表并运行仿真。

数字模拟混合设计及其仿真

数字模拟混合设计及仿真数模混合电路的设计,一直是硬件电路设计中性能提高的瓶颈。

众所周知,现实的世界都是模拟的,如果将模拟的信号转变成数字信号,可以方便的做进一步的处理。

模拟信号和数字信号的转变是否实时、精确,是电路设计的重要指标。

除了器件工艺,算法的进步会影响系统数模变换的精度外,实际工作环境中的众多干扰,噪声也是影响数模电路性能的主要因素。

在使用计算机来进行仿真时,选择合适电路设计的仿真方式会使该问题得到一定的解决,一般情况下的仿真多是解决线性、连续工作的稳态电路。

也有既可解决线性电路,也适合非线性电路;既可解决模拟电路,也适合数字电路;既可解决连续状态工作问题,也适合不连续状态工作的问题;既可解决连续稳定工作电路,也适合开关调节的启动工作电路。

总之,电气工程电路均可仿真。

仿真时,要读取电路中任何一点电流、任何两点间的电压都很容易,还可以进行频率响应、频谱分析、温度分析、参数变化分析、蒙特卡罗分析、最坏情况分析、噪声分析等等。

可以说,后面几种分析在面包板实验中是无法模拟进行的,加之,仿真软件是在计算机上运行,所以有使用方便、简单的优点。

数字模拟混合设计的特点1. 数模混合设计中的困难点1.1 数模混合电路设计当中,如何来分辨干扰源、干扰对象和干扰的路径是相当重要的,这是分析数模混合设计干扰的基础。

通常的电路中,模拟信号上由于存在随时间变化的连续变化的电压和电流有效成分,在设计和调试过程中,需要同时控制这两个变量,而且他们对于外部的干扰尤其敏感,因而通常作为被干扰对象做分析;数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰有较高的承受能力,但是这类信号变化快,特别是上升下降沿速度快,尤其是一些高速信号,一般上升下降沿在几百纳秒的级别,并且同时还伴随有较高的高频谐波成分,对外释放能量,通常作为干扰源。

t/ = t7(r)模拟电路r 数字电路7 = J⑴图1模拟电路和数字电路的信号一般的干扰源分为电压型干扰源和电流型干扰源。

第二讲ORCAD之PSPICEAD数模混合仿真模块-文档资料

请看演示…….

PSpice 交流分析

运行仿真程序,放置电压探针在out端(或者在 Probe 演示窗口中加入V(out)波形 ) 仿真结果如下:

PSpice 中的噪声分析

噪声分析是针对电路中固有噪声(如电阻和半导体的工作 噪声)所做的分析,它的计算结果时所求节点相对于输入 独立源的等效噪声。 伴随AC交流分析而进行 所涉及的噪声种类:

PSpice 中的噪声分析

V(INOISE)和V(ONOISE) (菜单 Trace>Add Trace…或 快捷 键 ) INOISE 即INPUT NOISE ONOISE 即OUTPUT NOISE

5.确定后,运行仿真。在PSpice A/D窗口中加入波形

噪声的计算方法: 输出节点的总噪声除 以相对输入激励源的 电路的总增益

编写VHDL (EXPRESS) 绘制电路图 (CAPTURE) 进行电路混合仿真 (PSPICE A/D) 设计电路板 (LAYOUT)

VHDL仿真 (EXPRESS)

运用 PSpice 的基本条件

1.待仿真的元器件模型必须是PSpice的仿 真模型 2.电路中应该含有激励源,并且符合相应 的电路特性分析类型的要求 3.必须设置好合适的电路特性分析类型

热噪声: 电子的无序运动引起 散弹噪声:单位时间通过PN结的载流子数目变化造成 闪烁噪声: 能量主要集中在低频段,由于生产工艺的缺陷而引起

等效噪声:将整个电路中的噪声源都集中折算到选定的独 立源处,然后计算在等效的噪声源的激励下,所求节点处 产生的噪声。 PSpice可以分析每个频率点上指定节点的等效输出噪声电 压和指定输入端的等效输入噪声电压。噪声电压的单位是 V A 或 Hz ,即把噪声电平对噪声带宽的均方根进行归 Hz 一化

第1-2讲 SPICE数模混合仿真程序的设计流程及方法

39

3

40

计算反相器链电路的延迟时间

.TITLE 1.2UM CMOS INVERTER CHAIN

.INCLUDE "models.sp"

……

X1 IN 1 INV WN=1.2U WP=3U

X2 1 2

.enddata

X1 IN 1 INV WN=wu WP=wpt

X2 1 2 INV WN=wu WP=wpt

X3 2 OUT INV WN=wu WP=wpt

CL OUT 0

1pf

……

.TRAN 1N 200N sweep data=cv

.measure tran td trig v(in) val=2.5 td=8ns

45

一个例子:缓冲驱动器分析

——HSPICE分析举例

46

准备模型文件

选用1.2um CMOS工艺level II模型 (Models.sp)

.MODEL NMOS NMOS LEVEL=2 LD=0.15U TOX=200.0E-10 VTO=0.74 KP=8.0E-05 +NSUB=5.37E+15 GAMMA=0.54 PHI=0.6 U0=656 UEXP=0.157 UCRIT=31444 +DELTA=2.34 VMAX=55261 XJ=0.25U LAMBDA=0.037 NFS=1E+12 NEFF=1.001 +NSS=1E+11 TPG=1.0 RSH=70.00 PB=0.58 +CGDO=4.3E-10 CGSO=4.3E-10 CJ=0.0003 MJ=0.66 CJSW=8.0E-10 MJSW=0.24

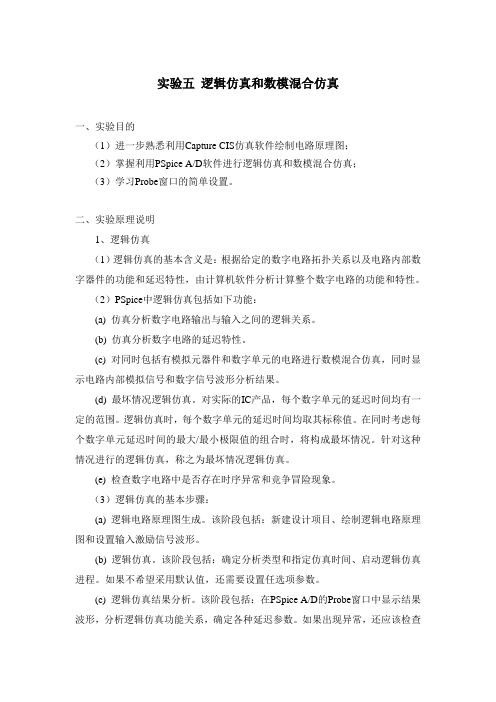

实验五 逻辑仿真和数模混合仿真

实验五逻辑仿真和数模混合仿真一、实验目的(1)进一步熟悉利用Capture CIS仿真软件绘制电路原理图;(2)掌握利用PSpice A/D软件进行逻辑仿真和数模混合仿真;(3)学习Probe窗口的简单设置。

二、实验原理说明1、逻辑仿真(1)逻辑仿真的基本含义是:根据给定的数字电路拓扑关系以及电路内部数字器件的功能和延迟特性,由计算机软件分析计算整个数字电路的功能和特性。

(2)PSpice中逻辑仿真包括如下功能:(a) 仿真分析数字电路输出与输入之间的逻辑关系。

(b) 仿真分析数字电路的延迟特性。

(c) 对同时包括有模拟元器件和数字单元的电路进行数模混合仿真,同时显示电路内部模拟信号和数字信号波形分析结果。

(d) 最坏情况逻辑仿真。

对实际的IC产品,每个数字单元的延迟时间均有一定的范围。

逻辑仿真时,每个数字单元的延迟时间均取其标称值。

在同时考虑每个数字单元延迟时间的最大/最小极限值的组合时,将构成最坏情况。

针对这种情况进行的逻辑仿真,称之为最坏情况逻辑仿真。

(e) 检查数字电路中是否存在时序异常和竞争冒险现象。

(3)逻辑仿真的基本步骤:(a) 逻辑电路原理图生成。

该阶段包括:新建设计项目、绘制逻辑电路原理图和设置输入激励信号波形。

(b) 逻辑仿真。

该阶段包括:确定分析类型和指定仿真时间、启动逻辑仿真进程。

如果不希望采用默认值,还需要设置任选项参数。

(c) 逻辑仿真结果分析。

该阶段包括:在PSpice A/D的Probe窗口中显示结果波形,分析逻辑仿真功能关系,确定各种延迟参数。

如果出现异常,还应该检查分析异常原因。

2、数模混合仿真数模混合电路是指电路中同时包括数字逻辑单元和各种模拟元器件。

也就是说电路中既包括1和0表示的数字信号,又包括连续变化的模拟信号。

对于数模混合电路,其内部节点可分为模拟型节点、数字型节点和接口型节点三种,其中接口型节点是指同时与逻辑器件和模拟器件相连的节点。

在对数模混合电路进行仿真分析时,关键是如何处理接口型节点,实现数字信号和模拟信号之间的转换。

数模混合仿真胡宗杰

将上面电路打包为analog_mix

analog1

X1

opa1

与 或B D

非非

门门

opa2

OUT E

MODULE analog_mix(IN,OUT) INPUT IN; OUTPUT OUT; WIRE X1; Digital digital1(.A(IN),.D(X1)); AD1 analog1(.D(X1),.E(OUT)); ENDMODULE

Interface A/D and D/A Signal Conversions

模拟电路

数字电路

连接模拟和数字电路的接口在进行通信时要进行数据转换

信号从模拟电路进入数字电路,需要将模拟电信号转换为数字 逻辑信号,需要一个阈值判断 a2d loth=0.35 hith=0.65 node=top.dout;

endmodule ‘inc“analog_mix.v’’

‘inc “digital_mix.v”

‘inc “digital.v”

一个问题:testbench里面并不包含模拟电路文件, 则仿真器如何调用模拟电路呢?

基于VCS-XA的混合仿真方法

电路系统

VCS: Verilog compile simulator 数字电路仿真器

将这段代码另存为一个 analog_mix.v文件

模拟电路端口全部与数字电路相连

IN

D digital2

A

X1

digital3

A analog2

digital4

E OUT1

B X2 B

C X3 C F OUT2

Digital digital2(.A(X1),.D(IN)); Digital digital3(.B(X2),.E(OUT1)); Digital digital4(.C(X3),.F(OUT2)); AD2 analog2(.B(X2),.C(X3),.A(X1));

第八章数模混合模拟

第八章数/模混合模拟上一章介绍了对数字电路进行逻辑模拟的基本概念以及模拟步骤和结果分析方法。

本章在此基础上进一步讨论数/模电路的混合模拟和最坏情况逻辑模拟。

虽然这两种模拟技术涉及到新的概念和特殊的处理方法,但这些处理和模拟过程是由系统自动完成的。

用户在调用PSpice A/D进行这两种模拟时,只是新增几个分析参数的设置,基本步骤与第七章介绍的逻辑模拟相同。

本章最后还简要介绍逻辑模拟过程中出错信息的显示和处理等问题。

8-1 数/模混合模拟顾名思义,数/模混合电路中同时包括有数字逻辑单元(如:门电路、触发器等)和各种模拟元器件(如电阻、电容、晶体管等)。

由于数字信号是以高低电平(1,0)为特征的数字量,模拟信号是连续变化的电信号,这是两类性质完全不同的电学量,这就给数/模混合电路的模拟分析带来新的问题。

本节在介绍数/模混合电路特点和处理方法的基础上,介绍PSpice A/D进行数/模混合模拟的基本步骤,重点说明如何设置与数/模混合模拟有关的参数。

8-1-1 数/模接口等效电路1. 接口型节点如7-1-1节所述,不管数/模混合电路多么复杂,同时与逻辑器件和模拟元器件相连的节点,在对数/模混合电路进行模拟分析时,关键问题是如何处理这类接口型节点,实现数字信号和模拟信号之间的转换。

2. 接口等效电路PSpice A/D处理接口型节点的基本方法是对数字逻辑单元库中的每一个基本逻辑单元都同时配备AtoD和DtoA两类接口型等效子电路。

其中AtoD子电路的作用是将模拟信号转化数字信号,DtoA子电路则用于将数字信号转化为模拟信号。

如果一个逻辑单元输入端与接口型节点相连,进行数/模混合模拟时,系统将在该输入端自动插入一个AtoD子电路。

将接口型节点处的模拟信号转化为数字信号,送至逻辑单元的输入端。

同样,如果逻辑单元的输出端与接口型节点相连,则系统将在该输出端自动插入一个DtoA子电路,将该输出端的数字信号转化为模拟信号送至接口型节点。

数模混合仿真.

《数模混合集成电路设计》课程报告数模混合仿真报告专业:集成电路班级:电子0 6 0 4学号:200681131姓名:高丕龙TTL IC脉冲发生器一.实验目的1.学习模拟数模混合电路的方法。

2.熟悉应用pspice软件进行电路仿真的流程。

3.学习使用pspice中库文件中不同的元件应用特点和参数设置。

二.实验原理1.实验原理图:2.原理分析:实际电路中,应靠元件的自然噪声来触发震荡,然而仿真中用的元件都已理想化,无法起振,使电路各节点均保持偏压点的电压值。

解决方法是给电容C1C2赋予IC(初始条件),迫使电路从非偏压点位置开始仿真。

由上图,知电路初态时V A=-1.061V,VB=2.501V,VC=4.501V,VD=0.939V,E=1即A为低压,B为高压,C为高压,D为低压。

当A为低压时,B为高压,C为高压,D为低压:B经由R1向电容C2充电使A点电压升高,C1经由R2放电使C点电压下降。

当A点和C点达到临界电压时,U7A和U8A就会改变状态。

使A 为高压时,B为低压,C为低压,D为高压。

当A为高压时,B为低压,C为低压,D为高压:D经由R2向电容C1充电使C电压升高,C2经由R1放电使A电压下降。

当A 点和C点达到临界电压时,U7A和U8A就会改变状态。

使A为低压,B为高压,C为高压,D为低压。

这样由于反相器U7A和U8A的迟滞特性和电容C1,C2的周期性充放电产生震荡脉冲,经U9A整形后即可输出规范的周期性方波了。

三.实验步骤1.建立新工程TTL,选择类型为anglog or mixed ,并设置存储地址为D:work文件夹。

2.从pspice元件库中取出三个7414,两个R,两个C。

并设置相关元件的参数。

3.按照原理图进行连线,并对通过Place Net Alias对输入输出信号线进行命名。

4.保存原理图文件并生成电路网表如下:* source TTLX_U7A A B $G_DPWR $G_DGND 7414 PARAMS:+ IO_LEVEL=0 MNTYMXDLY=0C_C2 D A 0.01u IC=2VR_R1 A B 1kX_U8A C D $G_DPWR $G_DGND 7414 PARAMS:+ IO_LEVEL=0 MNTYMXDLY=0X_U9A D E $G_DPWR $G_DGND 7414 PARAMS:+ IO_LEVEL=0 MNTYMXDLY=0R_R2 C D 1kC_C1 C B 0.01u IC=2V5.建立一个新的仿真文件,命名为TTL,并设置分析类型为瞬态分析和其他仿真参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用SpectreVerilog进行模数混仿,以Sigma-Delta ADC为例

SpectreVerilog模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL. 所以还需要安装Cadence LDV软件, 其内含Verilog-XL仿真器.

这里以自行设计的二阶全差分Sigma-Delta ADC为例, 详细介绍用SpectreVerilog的仿真过程. 所用工艺库为TSMC 0.18u,电源电压:1.8V.

1. 准备

Sigma-Delta ADC分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器. 如下图. 其中out为调制器的输出, 这里是1位0,1数据流. 数字滤波器为Verilog RTL级代码.

Schematic:

Symbol:

Verilog Code:

module DigitalFilter (in2out, out, clk, clr, in);

output in2out;

output [`wordsize-1:0] out;

input clk;

input clr;

input in;

reg in2out;

wire clk_half1, clk_half2;

……

Endmodule

同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分, 用ModelSim或Verilog-XL等仿真数字部分. 这里假定我们已有:

1) 模拟部分的原理图(包括Symbol);

2) 数字部分的Verilog代码,DigitalFilter.v, 模块名:DigitalFilter(in2out,out,clk,

clr,in);

3) 数字部分的TestBench代码, DigitalFilter_TB.v, 模块名: DigitalFilter_TB.

下图为最终的系统图:

2. 创建数字模块的Symbol

1) 新建一个Cell, View Name为symbol, Tool: Composer-Symbol.

2) 画Symbol. 简单地, 画一个矩形框, 添加几个Lable, 然后添加Pin.

3) 添加Pin. 左边输入, 右边输出. 对于多位的pin可以用如out<7:0>的样式作为pin的名字. 注意: 与模拟部分相连的多位Pin最好不要用一个pin, 而要用多个. 如下图.

4) 创建对应的Verilog文件. 在symbol编辑器中, Design菜单->CreatCellView->From CellView.

会弹出的对话框, Tool/Data Type一栏选择Verilog-Editor, 则To View Name会变为functional.

点击OK, 会弹出错误对话框, 点No. 自动弹出VI编辑器, 可以看到已经生成Verilog代码的空壳.

代码文件的路径在VI编辑器的标题栏上. 下面要做的就是把我们的数字模块(不是TestBench)的

代码填进去. 如果不想用VI编辑器, 也可以用其他文本编辑器. 复制代码时最好不要动自动生成

的代码. 经测试, 所有代码最好放在一个文件中.

这一步之后,数字部分就会有functional和symbol两个View。

这样基于Verilog代码的Symbol就创建完了.

3. 创建理想DAC

这里用Cadence自动生成的理想DAC。

同步骤2,首先创建Symbol,如下图:

类似步骤2,Design菜单->CreatCellView->From CellView. Type选择VerilogA-Editor

OK,弹出对话框,可以直接按OK,默认设置。

弹出新的对话框,选择Digital to Analog Converter, 然后Next。

设置位数,电压范围等参数。

如下图:

Next之后,会出现VerilogA代码,再Save和Finish。

完毕。

4. 创建顶层原理图.

1) 新建步骤1中所说的顶层Schematic视图, 这里名为MixSim, 把模拟的Symbol和上面建立的

数字块Symbol放到新建的原理图中, 并连好线. 模拟块输入端的激励源都要加上.

2) 添加数字块的Pin. 把数字块中除了和模拟块相连的输入端添加Pin. 这里的数字块输入端

信号与模拟块共用,因此没有输入Pin。

5. 创建config视图

1) 新建Cell, 名字和步骤4中的原理图名字一致. Tool选择 Hierarchy-Editor, 则View Name 会自动为config. OK,

2) 在新出现的New Configuration窗口中View: 文本框为空, 填入: schematic, 注意大小写. 点击下方的Use Template…, -> Name一栏选择: spectreVerilog, OK,

3) 再OK关闭New Configuration. 点击Cadence hierarchy editor窗口的保存按钮, 关闭退出.

4) 这时MixSim有两个View: config, schematic. 打开config, 会提示打开模式, 直接OK, 则原理图会被打开,并可以进行修改。

6. 建立仿真环境

1) 打开config视图, 菜单Tools->Analog Environment, 打开ADE.

2) ADE, 菜单Setup->simulator, Simulator选择spectreVerilog, OK.

3) ADE, 菜单 Setup->Stimuli->Analog, 弹出Setup窗口, 选中Global Sources, 把电源电压填上, 这一步和spectre一样, 另外别忘了添加模型库. 不再赘述.

4) 添加数字块的测试向量. ADE, 菜单 Setup->Stimuli->Digital, 弹出VI编辑窗口, 窗口的标题栏和信息栏都有测试向量的文件路径, 可以直接修改它. 系统自动生成了一个initial块, 这个initial块不能改动. 现在就可以把Testbench中的代码复制到这个文件中了. 注意: `timescale不要复制, 模块名和端口定义不要复制, 模块实例引用不要复制. 也就是只能复制initial块和always块以及parameter语句. 同时注意到, 系统生成的的initial块中把输入信号初始化为零, 因此复制进来的语句一定要避免在0时刻给这些信号赋值. 本例数字块的输入与

模拟块共用,因此不用添加代码。

5) 打开Config视图,菜单Tools->Mix Signal Opts., 会新增加一个Mixed-Signal菜单栏。

菜单Mixed-Signal -> Interface Elements -> Library…

主要修改两个参数d2a-vh,d2a-vl,他们是输出数字信号的0,1电压

把Model IO选为Input,修改a2d_v0, a2d_v1,他们是模拟转数字的阈值电压,这里为0.6V 和

1.2V

7. 仿真.

仿真过程与Spectre一样,设置瞬态仿真时间,输出节点电压。

这是ADC仿真结果图:

由于搭建整个仿真环境比较复杂, 因此经常会出错, 需要耐心调试,尤其是Verilog代码错误,

仿真器只说有错, 但不知道错在何处, 很不爽.

本教程仅适用于初学者,同时请高手指点一二,错误和走弯路都在所难免,谢谢。