数电第五版(阎石)第三章课后习题及答案

《数字电子技术基本教程第》阎石习题详解

51Ω 1.5KΩ 100KΩ ∞

0

0

0 不定

5

5

5 不定

图 2.44 习题 2-3 电路图

图 2.45

3.16 答案:

RP(m a x)

VCC VOH nIOH IL

5 3.6 2 0.1103 3 20106 5.4K

RP(m in)

VOH mI IH

10106

5 3.5 3 1106

6

41.7K

RP(m in)

VDD VOL IOL(max) mI IL

5 0.3 4103 1106

6

1.2K

图 2.53 习题 2-17 图

3.13 答案:

图 2.44 习题 2-3 电路图

vI1/V 悬空 接地 51Ω 3.6 50KΩ 0.2 vI2/V 1.4V 0V 0V 1.4V 1.4V 0.2V

2.7 答案:

0

1

1

0

0

1

高阻态

0 0

1

2.8 答案: 1

1 0

0

1

0 0

1

2.9 答案:

图 2.48 习题 2-9 图

2.12 答案:

F A B AB AB 1 B 1 B B

最多可以接10个同样的门电路

图 2.55 习题 2-19 图

3.20 答案:

IOH(max) 0.4mA

IIH(max) 20 A

IOL(max) 8mA IIH(max) 0.4mA

2nIIH(max) IOH(max)

n

IOH (max) 2I IH(max)

数字逻辑电路第三章部分答案

Hale Waihona Puke 根据与非与非式即可画出逻辑图其实将余3码直接当作一个二进制数十进制bcd代码再加3减去3就还原成为一位十进制数的bcd码设输出变量为ryg且低电平时点亮led即低电平输出有效

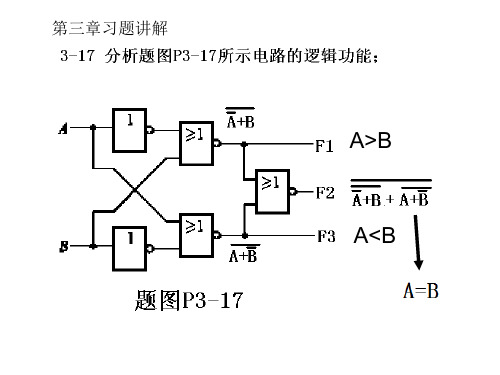

第三章习题讲解

A>B

A<B

同或电路

2线—4线译码电路

结果:

根据与非与非式即可 画出逻辑图

其实,将余3码直接当 作一个二进制 数(十进 制BCD代码再加3), 减去3就(还原)成为 一位十进制数的BCD码

8-1 MUX74151 功能表

功 能 表

S2 X 0 0 0 0 1 1 1 1 输入 S1 X 0 0 1 1 0 0 1 1 S0 X 0 1 0 1 0 1 0 1 使能 E 1 0 0 0 0 0 0 0 0 输出 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y Y

设输出变量为R、Y、G,且低电平时点亮LED(即低电平输出有效)。 故可以列出真值表如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

列出最小项表达式 如下:

经变换 ,可以列出真值表如下:

卡诺图:

经变换 ,可以列出真值表如下:

根据简化后的与非与非式,选择合适的门电路 (与非门、OC输出门等)实现电路功能

11

D00 D D11 D D22 D D33 D D44 D D55 D D66 D D77 D

根据:

可得:

D0、D3、D4、D6为1; D1、D2、D5、D7为0。

则F的状态依次为: D0、D1、D2、D3、D4、D5、D6、D7、D0、D1………… 1 0 0 1 1 0 1 0 1 0 : D0、D3、D4、D6为1; D1、D2、D5、D7为0。

数字电路教案-阎石-第三章-逻辑门电路

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

阎石《数字电子技术基础》(第5版)(课后习题 数制和码制)【圣才出品】

1.3 将下列二进制小数转换为等值的十进制数。

(1)(0.1001)2

;(2)(0.0111)2

;(3)(0.101101)2

(0.001111)2 。

解:(1) (0.1001)2 1 21 0 22 0 23 1 24 0.5625 (2) (0.0111)2 0 21 1 22 1 23 1 24 0.4375

3/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

1.9 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点

以后 4 位有效数字。

Байду номын сангаас

(1)(25.7)10 ; (2)(188.875)10 ; (3)(107.39)10 ; (4)

(174.06)10 。

2/8

圣才电子书

十万种考研考证电子书、题库视频学习平

台

。

解:(1)

8C 16

1000

1100 2

(2) 3D.

BE 16

0011 1101.1011 1110 2

(3)

8F

.FF

16

1000

1111. 1111

1111 2

(4) 10.

00 16

0001

0000.0000

(4) (255)10 (11111111)2 (FF )16

1.8 将下列十进制数转换为等值的二进制数和十六进制数。要求二进制数保留小数点 以后 8 位有效数字。

(1)(0.519)10 ; (2)(0.251)10 ; (3)(0.0376)10 ; (4) (0.5128)10 。

解:(1) (0.519)10 (0.10000100)2 (0.84)16 (2) (0.251)10 (0.01000000)2 (0.40)16 (3) (0.0376)10 (0.00001001)2 (0.09)16 (4) (0.5128)10 (0.10000011)2 (0.83)16

课后习题答案_第3章_门电路

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

数电第五版答案阎石第一三章(完整资料).doc

【最新整理,下载后即可编辑】第一章1.1 二进制到十六进制、十进制(1)(10010111)2=(97)16=(151)10 (2)(1101101)2=(6D)16=(109)10(3)(0.01011111)2=(0.5F)16=(0.37109375)10 (4)(11.001)2=(3.2)16=(3.125)10 1.2 十进制到二进制、十六进制(1)(17)10=(10001)2=(11)16(2)(127)10=(1111111)2=(7F)16(3) (0.39) 10 (0.0110 0011 1101 0111 0000 101 0)2 (0.63 D70 A )161.8 用公式化简逻辑函数(1)Y=A+B(2)Y ABC A B C 解:Y BC A B C C A B C (1 A+A=1)(4)Y ABCD ABD ACD 解:Y AD(BC B C ) AD(B C C) AD(5)Y=0(4) (25.7) 10 (11001.101 1 0011)2 (19.B3)16(3)Y=1(7)Y=A+CD(6)Y AC(CD AB) BC(B AD CE) 解:Y BC(B AD CE) BC(B AD) CE ABCD(C E ) ABCDE(8)Y A (B C)(A B C)(A B C) 解:Y A (B C)(A B C)(A B C) A (ABC BC)(A B C) A BC( A B C) A ABC BC A BC(9)Y BC AD AD(10)Y AC AD AEF BDE BDE1.9 (a) Y ABC BC(b)(c) Y1 AB AC D,Y2 AB AC D ACD ACD (d) Y1 AB AC BC,Y2 ABC ABC ABC ABC 1.10 求下列函数的反函数并化简为最简与或式Y ABC ABC(1) (2)Y A C DY AC BC(3)Y (A B)(A C)AC BC 解:Y ( A B)(A C)AC BC [(A B)(A C) AC] BC(4)Y A B C ( AB AC BC AC)(B C) B C【最新整理,下载后即可编辑】(5)Y AD AC BCD C 解:Y (A D)(A C)(B C D)C AC(A D)(B C D) ACD(B C D) ABCD1.11 将函数化简为最小项之和的形式(6)Y 0(1)Y ABC AC BC 解:Y ABC AC BC ABC A(B B )C ( A A)BC ABC ABC ABC ABC ABC ABC ABC ABC ABC(2)Y ABCD ABCD ABCD ABCD ABCD ABCD (3)Y A B CD解:Y A(BC D BCD BCD BCD BC D BCD BCD BCD) B( ACD ACD ACD ACD AC D ACD ACD ACD) (AB AB AB AB)CD ABC D ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABCD (13)(4)Y ABCD ABCD ABCD ABC D ABCD ABCD ABCD ABCD (5)Y LM N LMN LMN LMN L M N LMN1.12 将下列各函数式化为最大项之积的形式(1)Y (A B C )( A B C)( A B C )(2)Y (A B C)( A B C)( A B C)(3)Y M 0 M 3 M 4 M 6 M 7(4) Y M 0 M 4 M 6 M 9 M12 M13(5)Y M 0 M 3 M 51.13 用卡诺图化简法将下列函数化为最简与或形式:(1)Y A D(3)Y 1(2)Y AB AC BC CD(4)Y AB AC BC(5)Y B C DY C D AB(7)(9)Y B D AD BC ACD (8)Y ( A, B, C, D) m (0,1,2,3,4,6,8,9,10,11,14)Y AB AC(6)Y AB AC BCY C(10)Y ( A, B, C) (m1,m4 , m7 )Y B CD AD 【最新整理,下载后即可编辑】Y ABC ABC ABC1.14 化简下列逻辑函数 (1)Y A B C D (3)Y AB D AC (5)Y AB DE CE BDE AD ACDE1.20 将下列函数化为最简与或式 (1)Y ACD BCD AD (3)Y A B C (5)Y 1 第三章3.1 解:由图可写出 Y1、Y2 的逻辑表达式:Y1 ABC ( A B C) AB AC BC ABC ABC ABC ABCY2 AB AC BC真值表:(2)Y CD ACD (4)Y BC BD(2)Y B AD AC (4)Y A B D (6)Y CD B D AC3.2 解: , comp 1、Z 0 时,Y1 A,Y2 A2,Y3 A2 A3 A2 A3,Y4 A2 A3 A4comp 0、Z 0 时,Y1 A1,Y2 A2,Y3 A3,Y4 A真值表:3.3 解:【最新整理,下载后即可编辑】3.4 解:采用正逻辑,低电平=0,高电平=1。

数字电子技术基础第五版第三章

iC f (VCE )

三、双极型三极管的基本开关电路

只要参数合理,则:

VI=VIL时,T截止,VO=VOH VI=VIH时,T导通,VO=VOL

四、三极管的开关等效电路

截止状态

饱和导通状态

若 VGS (th)P VI VDD ,则T2导通

所以VI在0 ~ VDD ,T1和T2至少一个导通 VI与VO之间为低电阻

(2) 当C=1, C’=0

则T1导通 则T2导通

|VGS|=|0-VI|>|VGS(th)P| VGS= VDD-VI>VGS(th)N

2. 双向模拟开关

C=1时,开关导通; C=0时,开关截止.

iD

I

DS

( VGS VGS ( th)

1)2

当VGS

VGS

(

下

th)

,i

D

VGS 2

可变电阻区:当VDS 较低(近似为0),VGS 一定时

VDS iD 常数(电阻) 这个电阻受VGS 控制,可变。

三、MOS管的基本开关电路

因为 ROFF 109 , RON 1K 只要RON RD ROFF , 则:

一、双极型三极管的结构

管芯 + 三个引出电极 + 外壳

二、三极管的输入特性和输出特性

三极管的输入特性曲线(NPN) VON :开启电压

• 硅管,0.5 ~ 0.7V • 锗管,0.2 ~ 0.3V

近似认为:

• 若VBE < VON , 则 iB= 0;

•

若VBE ≥VON ,则 iB 的大小 由外电路电压和电阻决定:

数字电路第五版课后答案

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E++ +( ) = + +解:A+ABC ACD C D E++ +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式 (3)ABC B( +C)解:ABCB( +C)= + +(A B C B C)( + )=AB AC BB BC CB C+ + + + +=AB C A B B+ ( + + +1)=AB C+(6)(A + + + +B A B AB AB ) ( ) ( )() 解:(A + + + +B A B AB AB ) () ( )( )= A B ⋅+ A B ⋅+(A + B A )(+ B )=AB(9)ABCD ABD BCD ABCBD BC + + + +解:ABCD ABD BCD ABCBD BC +++ +=ABC D D ABD BC D C ( + +) + ( + ) =B AC AD C D ( + + + ) =B A C AD ( + + + ) =B A C D ( + + ) =AB BC BD + +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B = +(1)L AB AC =(2) ( ) L DAC = +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3) ( )() L ABCD=+ +解: ( , , , ) L ABCDBCDBCDBCDABD = + + +(1)ABCD ABCD AB AD ABC+ + + +解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D++ ( + )( + +)( + )( + +)( + )=ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + + + + +(6)L A B C D( , , , )=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L= +A D(7)L A B C D( , , , )=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L AD AC AB= + +已知逻辑函数L AB BC CA=+ + ,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC ⋅ ⋅4>由已知函数的与非-与非表达式画出逻辑图2> 由真值表画出卡诺图3> 由卡诺图,得逻辑表达式 LABBCAC = + +第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RE

R1R2 R1 R2

3.97k

vE

vI

vI 10 5.1V 5.1 18

当������������=0时,

vE

10 5.1V 5.118

2.2V

三极管能可靠的截止。

当������������=5v时,

vE

5

5 10 5.1V 5.118

1.69V

第三章 门电路

【题3-4】画出图P3.4所示电路在下列两种情况下的输出电压 波形:(1)忽略所有门电路的传输延迟时间;(2)考虑每 个门都有传输延迟时间������������������ 。输入端A、B的电压波形图如图 所给出。

解:两种情况下的电压波形图如图A3.4所示。

【题3.7】试分析图3.7中各电路图的逻辑功能,写出输出的 逻辑函数式。

I 为 IH (max) 1uA,低电平输入电流最

大值为 IIL(max) 1uA ,试求在VOD 5V 、、、、 并且满足VOH 4.4V ,VOL 0.33V

的情况下,R L 的取值的允许范围。

解:R L 的最大允许值为:

R L(max)

VOD nI OH

VOH mIIH

5 4.4 2 5 106 9 1 106

31.6k

R L 的最小允许值为:

RL(m in)

VOD VOL IOL(max) | m'I IL

|

5 0.33 5.2 10 3 9 10 6

0.9k

故R L 的取值范围应为:

R 0.9k L 31.6k

iB

vE

VBE RE

1.69 3.97

0.7

I BS

Vcc VCE(sat )

(RC RCE(sat) )

【题3.10】图P3.10中的 ������1~������4 是OD输出结构的与非门74HC03, 他们接成线与结构。试写出线与输出Y与输入������1、 ������2、 ������1、 ������2、������1、������2、������1、������2之间的逻辑关系式,并计算外接电阻������������ 取值的允许范围。已知������������������=5V, 74HC03输出高电平时漏电流的

I 最大值为 OH(max) 5A ,低电平输 I 出电流最大值为 OL(max) 5.2mA I 此时输出低电平为 OL(max) 0.33V

负载门每个输入端的高、低电

平输入电流最大值为±1������������。

要求满足������������������ ≥4.4V, ������������������ ≤0.33V。

(a)图P3.7(a)电路可划分为四个反相器电路和一个三输 入端的与非门电路,如图所示。从输入到输出逐级写出输出 的逻辑函数式,

A1 A',B1 B',C1 C', D ( A1B1C1)'

Y D' A1B1C1 A'B'C ' ( A B C)'

(b)图P3.7(b)电路可划分为五个反相器电路和一个或非 门电路,如图所示。从输入到输出逐级写出输出的逻辑函数 式:

V R CE(sat) 0.1V ,饱和导通内阻 CE(sat )

=20 。如果参数配合不当,则在

电源电压和������������ 不变的情况下,应该 如何修改电路参数?

解:利用戴维宁定理可以将电路简

化成图A3.11的形式。其中的������������ 、������������ 分别为:

20k

������������的最小允许值为:

R L(min)

VOD VOL I OL(max) | m 'IIL

|

5 0.33 5.2 103 10 106

0.9k

故������������ 的取值范围应为:

R 0.9k L 20k

【题3.11】在图P3.11的三极管开关电路中,若输入信号������1的 高、低电平分别为������������������=5V,������������������=0V,试计算在图中标注的参 数下能否保证������1=������������������时三极管饱和导通, ������1=������������������时三极管可 靠地截止?三极管的饱和导通压降

Y I ' H (AB)'(CD)' ' (INH ) '

( AB CD)' (INH )'

(d)图P3.7(d)电路可划分为两个反相器电路和两个传输 门电路,如图所示。从输入到输出逐级写出输出的逻辑函数 式:

Y A'B ' AB

【题3.8】 试画出图3-8(a)(b)两个电路的输出电压波形, 输入电压波形如图(c)所示。

输出电压波形 如右图所示:

【题3.9】 在图3-21所示电路中,G1和G2是两个OD输出结构 的与非门74HC03,74HC03输出端MOS

管截止电流为IOH(max) 5uA 导通时允

许的最大负载电流为IOL(max) 5.2mA

这时对应的输出电压VOL(max)=0.33V。 负载门G3-G5是3输入端或非门74HC27, 每个输入端的高电平输入电流最大值

解:在������������取值合理的情况下,Y的逻辑函数式为:

Y (A1A2 B 1B 2 C 1C 2 D 1D 2)'

������������的最大允许值为:

R L(max)

V DD nI OH

VOH mIIH

5 4.4 4 5 106 10 106

Y ( A1 B1 C1)' ( A' B' C' )' ABC

(c)图P3.7(c)电路可划分为三个与非门电路、两个反相 器电路和一个或非门电路,如图所示。从输入到输出逐级写 出输出的逻辑函数式:

E (AB )',F (CD )',G (EF )',H (INH G )'