第3章 用数字电路实现数据的存储和运算

简述数字电路在计算机中的应用

简述数字电路在计算机中的应用

数字电路是一种用于处理数字信号的电子电路,它在计算机中扮演着重要的角色。

以下是数字电路在计算机中的一些主要应用:

1. 处理器:计算机的中央处理器(CPU)是数字电路的核心。

CPU 包含了大量的逻辑门、寄存器和算术逻辑单元(ALU),用于执行指令和进行数据处理。

数字电路的高速性能和精确控制使得 CPU 能够快速地执行计算和逻辑操作。

2. 内存:计算机中的内存使用数字电路来存储数据和程序。

内存芯片由许多存储单元组成,每个单元可以存储一个二进制数。

数字电路用于控制内存的读写操作,以及在内存中进行数据的存储和检索。

3. 输入/输出设备:计算机的输入设备(如键盘、鼠标)和输出设备(如显示器、打印机)也使用数字电路。

数字电路用于将输入的模拟信号转换为数字信号,以及将数字信号转换为模拟信号输出。

4. 数据通信:计算机通过网络进行数据通信时,数字电路用于处理和传输数字信号。

网络接口卡(NIC)、路由器和交换机等设备都包含数字电路,用于实现数据的发送、接收和转发。

5. 时钟和定时器:计算机中的时钟和定时器电路使用数字电路来产生精确的时间信号。

这些电路用于控制系统的时序、定时操作和中断处理。

总之,数字电路在计算机中应用广泛,它是计算机能够处理和存储数字信息的基础。

数字电路的高速、精确和可靠性能使得计算机在各个领域都发挥着重要的作用。

数字逻辑与计算机组成原理:第三章 存储器系统(1)

A3 0

字线

地0 A2 0 址

译

A1

0码 器

A0 0

15

读 / 写选通

… …

…

0,0 … 0,7

16×8矩阵

15,0 … 15,7

0

…

7 位线

读/写控制电路

D0

… D7

(2) 重合法(双译码方式)

0 A4

0,00

…

0 A3

阵

A2

译

0码

31,0

…

A1

器 X 31

0 A0

… …

或低表示存储的是1或0。 T5和T6是两个门控管,读写操作时,两管需导通。

六管存储单元

保持

字驱动线处于低电位时,T5、T6 截止, 切断了两根位线与触发器之间的 联系。

六管存储单元

单译码方式

读出时: 字线接通 1)位线1和位线2上加高电平; 2)若存储元原存0,A点为低电

平,B点为高电平,位线2无电 流,读出0。

3)若存储元原存1,A点为高电 平,B点为低电平,位线2有电

流,读出1。

静态 RAM 基本电路的 读 操作(双译码方式)

位线A1

A T1 ~ T4 B

位线2

T5

行地址选择

T6

行选

T5、T6 开

列选

T7、T8 开

T7

T8

读选择有效

列地址选择 写放大器

写放大器

VA

T6

读放

读放

DOUT

T8 DOUT

DIN

1.主存与CPU的连接

是由总线支持的; 总线包括数据总线、地址总线和控制总线; CPU通过使用MAR(存储器地址寄存器)和MDR(存储

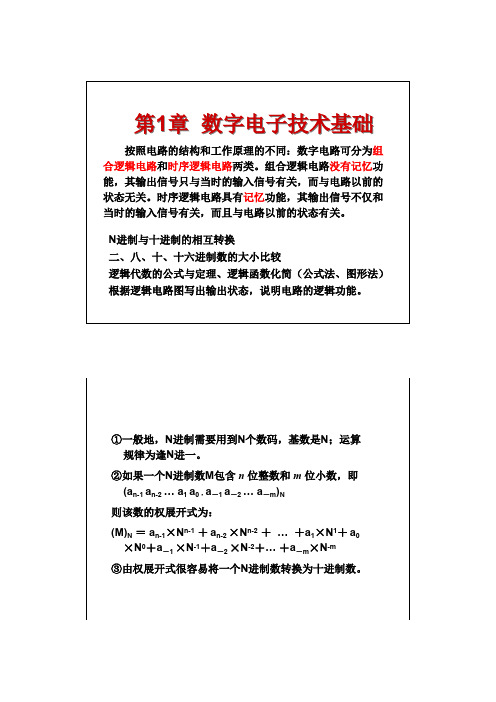

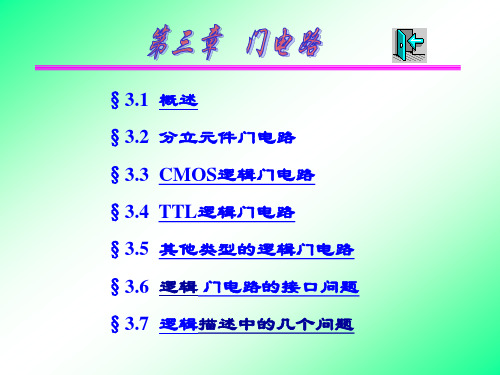

数字电路讲义 第三章

是构成数字电路的基本单元之一

CMOS 集成门电路 用互补对称 MOS 管构成的逻辑门电路。

TTL 集成门电路 输入端和输出端都用 三极管的逻辑门电路。

CMOS Complementary Metal-Oxide-Semiconductor TTL 即即 Transistor-Transistor Logic 按功能特点不同分 普通门 输出 三态门 CMOS (推拉式输出) 开路门 传输门 EXIT

E

B UBE(sat) iB ≥ IB(sat) E C

三极管 截止状态 等效电路

UCE(sat)

三极管 饱和状态 等效电路

EXIT

逻辑门电路

开关工作的条件

截止条件 uBE < Uth 可靠截止条件为 uBE ≤ 0

VCC U CE(sat) RC VCC RC

饱和条件

iB > IB(Sat)

逻辑门电路

[例] 下图中,已知 ROFF 800 ,RON 3 k,试对应 输入波形定性画出TTL与非门的输出波形。

A 3.6 V 0.3 V

逻辑0 (a)

逻辑1

O Ya t

(b)

解:图(a)中,RI = 300 < ROFF 800 相应输入端相当于输入低电平, O 也即相当于输入逻辑 0 。 Yb 不同因此 TTLY 系列, R R 不同。 ON、 OFF UOH 。 a 输出恒为高电平 图(b)中,RI = 5.1 k > RON 3 k 相应输入端相当于输入高电平, O 也即相当于输入逻辑 1 。 Yb A 1 A 因此,可画出波形如图所示。

0. 3 O

t

EXIT

逻辑门电路

二、三极管的动态开关特性

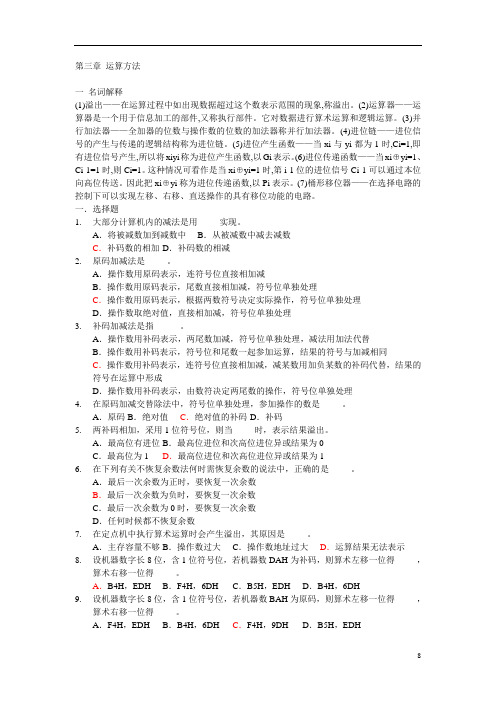

第三章 运算方法

第三章运算方法一名词解释(1)溢出——在运算过程中如出现数据超过这个数表示范围的现象,称溢出。

(2)运算器——运算器是一个用于信息加工的部件,又称执行部件。

它对数据进行算术运算和逻辑运算。

(3)并行加法器——全加器的位数与操作数的位数的加法器称并行加法器。

(4)进位链——进位信号的产生与传递的逻辑结构称为进位链。

(5)进位产生函数——当xi与yi都为1时,Ci=1,即有进位信号产生,所以将xiyi称为进位产生函数,以Gi表示。

(6)进位传递函数——当xi⊕yi=1、Ci-1=1时,则Ci=1。

这种情况可看作是当xi⊕yi=1时,第i-1位的进位信号Ci-1可以通过本位向高位传送。

因此把xi⊕yi称为进位传递函数,以Pi表示。

(7)桶形移位器——在选择电路的控制下可以实现左移、右移、直送操作的具有移位功能的电路。

一.选择题1.大部分计算机内的减法是用_____实现。

A.将被减数加到减数中B.从被减数中减去减数C.补码数的相加 D.补码数的相减2.原码加减法是_____。

A.操作数用原码表示,连符号位直接相加减B.操作数用原码表示,尾数直接相加减,符号位单独处理C.操作数用原码表示,根据两数符号决定实际操作,符号位单独处理D.操作数取绝对值,直接相加减,符号位单独处理3.补码加减法是指______。

A.操作数用补码表示,两尾数加减,符号位单独处理,减法用加法代替B.操作数用补码表示,符号位和尾数一起参加运算,结果的符号与加减相同C.操作数用补码表示,连符号位直接相加减,减某数用加负某数的补码代替,结果的符号在运算中形成D.操作数用补码表示,由数符决定两尾数的操作,符号位单独处理4.在原码加减交替除法中,符号位单独处理,参加操作的数是_____。

A.原码 B.绝对值C.绝对值的补码 D.补码5.两补码相加,采用1位符号位,则当_____时,表示结果溢出。

A.最高位有进位 B.最高位进位和次高位进位异或结果为0C.最高位为1 D.最高位进位和次高位进位异或结果为16.在下列有关不恢复余数法何时需恢复余数的说法中,正确的是_____。

数字电路(复习)

②C=1、C=0,即C端为高电平(+VDD)、C端为低电平(0V) 时,TN和TP都具备了导通条件,输入和输出之间相当于开关接通 一样,uO=uI 。

2.三态门电路的输出有高阻态、高电平和低电平3种状态

• 三态门逻辑符号控制端电平的约定

A

1

Y

EN

EN

(a)控制端低电平有效

控制端加低电平信号时,三 态门处于工作状态,Y=A, 加高电平信号时禁止,Y=Z

加法器

能对两个1位二进制数进行相加而求得和及进位的逻辑电 路称为半加器。 能对两个1位二进制数进行相加并考虑低位来的进位,即 相当于3个1位二进制数的相加,求得和及进位的逻辑电路称 为全加器。 实现多位二进制数相加的电路称为加法器。按照进位方 式的不同,加法器分为串行进位加法器和超前进位加法器两 种。串行进位加法器电路简单、但速度较慢,超前进位加法 器速度较快、但电路复杂。 加法器除用来实现两个二进制数相加外,还可用来设计 代码转换电路、二进制减法器和十进制加法器等。

数据分配器

数据分配器的逻辑功能是将1个输入数据传送到 多个输出端中的1个输出端,具体传送到哪一个输出 端,也是由一组选择控制(地址)信号确定。 数据分配器就是带选通控制端即使能端的二进 制译码器。只要在使用中,把二进制译码器的选通 控制端当作数据输入端,二进制代码输入端当作选 择控制端就可以了。 数据分配器经常和数据选择器一起构成数据传 送系统。其主要特点是可以用很少几根线实现多路 数字信息的分时传送。

八进制数

0 1 2 3 4 5 6 7 10 11 12 13 14 15 16 17

十六进制数

0 1 2 3 4 5 6 7 8 9 A B C D E F

门电路 国标符号 曾用符号 美国符号 表达式

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

数字电子技术基础第三版课后习题解答与第章

【题3-2】 解:),=(A田B) C=A⑥B+C}、=AB+(AB)C=AB+(AB+AB)C=AB+ABC+ABC=AB+BC+AC)=A B CY,=AB+(A B)C=AB+BC+AC两个电路功能相同,均为全加器。

14

(2) CDAB 00 01 11o0[ X0111 1 1 X10 1 1

A₃B₃…A₀B₀ 91A₃B₃…A₀B₀A<B.A>R低位 A=B74LS85Fg FxBF,A>B

A₂B₇…A₄B₄A=B74LS85FAn FxnF

【题3-9】 解:连线图如图3-26所示。

图3 - 26

27

【题3-10】 解:A=A₃A₂A₁A₀ 8421BCD 码 B=B₃B₂B₁B₀ 余3 BCD 码C=C₃C₂C₁C₀ 2421BCD 码 D=D₃D₂D₁D₀ 余 3 循环码(1)卡诺图如图3 - 27所示。B₃=A₃+A₂A₁+A₂A₀=A₂A₂A₁A₂A₀

2

A

B

A

Y'

2

0

0

0

1

0

0

1

1

0

0

1

0

0

0

1

1

1

0

1

)

3-2 解:(1)X=AB;Y=AB+AB=AB+AB;Z=AB。真值表如表3-10所示。表3-10

(2)实现1 位数值比较功能。

3

Y₀=X,④X 。 Y₀=Y₁X₀=X₂X₇X。若令 X₂=B₂ 、X₁=B₁ 、λ₀=B, 则当 K=1 时电路可正确地实现3位二进制码到3位循环码的转换,即有 Y₂=G₂ 、Y,=G₁ 、Y₀=G₀ 。 若 令X₂=G₂ 、X,=G₁、X₀=G₀, 则当 K=0 时,通过比较可明显看出,只要去掉一个反相器便可实现3位循环码到3位二进制码的转换,即有 Y₂=B₂ 、Y₁=B₁ 、Y₀=B₀。

数字电子技术(第四版)(孙津平)章 (4)

图 3.22 例8的连接图

3. 例9

试用八选一数据选择器74LS151产生逻辑函数

解 把逻辑函数变换成最小项表达式:

八选一数据选择器的输出逻辑函数表达式为

若将式中A2、A1、A0用A、B、C来代替, D0=D1=D3= D6=1, D2=D4=D5=D7=0,画出该逻辑函数的逻辑图, 如图 3.23所示。

1. 74LS151是一种典型的集成电路数据选择器。 如图3.21所示 是74LS151的管脚排列图。 它有三个地址端A2A1A0。 可选择

D0~D7八个数据, 具有两个互补输出端W和W。 其功能如表3.12

所示。

图 3.21 74LS151 (a) 符号图; (b) 管脚图

2. 例 8 用两片74LS151连接成一个十六选一的数据选择器。 解 十六选一的数据选择器的地址输入端有四位, 最高

止工作。

图3.18 例7的连接图

3.4 数据选择器和数据分配器

3.4.1 数据选择器

数据选择器按要求从多路输入选择一路输出, 根据输入端 的个数分为四选一、 八选一等等。 其功能相当于如图3.19所示 的单刀多掷开关。

图3.19 数据选择器示意图

如图3.20所示是四选一选择器的逻辑图和符号图。 其

2. 非二进制编码器(以二-十进制编码器为例) 二-十进制编码器是指用四位二进制代码表示一位十进制数 的编码电路, 也称10线-4线编码器。四位二进制代码共有16 种组合状态, 而0~9共10个数字只用其中 10 个状态, 所以二-十进制编码方案很多。 最常见是8421 BCD码编码器,

如图3.7所示。 其中,输入信号I0~I9代表0~9共10个十进制信号, 输出信号Y0~Y3为相应二进制代码。

话铃响用1表示, 铃没响用0表示。 当优先级别高 的信号有效时, 低级别的则不起作用, 这时用×表示; 用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

禁止 禁止 0 0 1 1 0 1

禁止 禁止 置0

置1

Qn

当把两个输入 S 和 R 变为一个 D 的互补输 入后,可以通过控制 信号 E 完成该触发器 的写入操作,在 E =1 时,Q 将随D而变化。

/Q Q

现态 E 0 0 0 0 1 1 D 0 0 1 1 0 0 Qn 0 1 0 1 0 1

次态 Qn+1 禁止 禁止 禁止 禁止 0 0

说明 禁止 禁止 禁止 禁止 置0

D

1 1

E

1 1

0 1

1 1

置1

D 型触发器

前面刚介绍的触发器属于电平触发方式, 输入 R 和 S 不能同时为低电平,而且 R 、 S 和 D 在触发器写入期间应保持不变,否 则产生操作错误。 D 型触发器是由3个基本触发器构成的, 它属于边沿触发方式。输入信号 D 在触发脉 冲(时钟) Clock(clk) 的正跳变沿期间被 写入触发器,其它时间 D 的变化不会影响触 发器的状态。

D 型触发器又被称 为延时触发器,常用于 构建寄存器,移位寄存 器,计数器等部件。 输入信号 /S 和/R 用于触发器的清 0 和置5

与非3

与非4

与非6

/R

D

CLK

/S

/Q /R CLK

Q /S D

One of D trigger stats table

现态 /R /S CLK D 1 1 0 X 1 1 1 0 1 1 1 1 1 0 1 ↑ ↑ X X X 1 0 X X Qn X X X X X X 次态 说明 Qn+1 Qn Qn 1 0 0 1 保持 D 置0 置1

3.1.1 MOS晶体管

• 按物质是否导电,可以分为:

– 导体(双向导电) – 绝缘体(不导电) – 半导体

• 同时具备导体和绝缘体两种特性,其特性取决于在 物体两端所施加电压的方向,当在一个方向上有正 的电压存在时,可以允许电流流过(导体特性); 而在相反的方向上施加一定大小的电压时,该物体 中不会产生电流(绝缘体特性),即该物体只能在 单个方向上导电。

X=A+B

X

A B 0 0 0 1 1 0 1 1

X 1 1 1 0

或门

或非门

真值表和逻辑表达式的对应关系

真值表

A B 0 0 0 1 1 0 1 1

X 0 0 0 1

A B

X = A •B

1. 用与逻辑写出真值表中 每一横行中输出为 1 的逻辑表达式; X 2. 用或逻辑汇总真值表中 全部输出为 1 的逻辑。 3. 不必理睬那些输出为 0 的各行的内容,它们已 经隐含在通过 1、2 两 步写出的表达式中。 X= A * B + A * B + A * B

D_trigger code

//d_trigger.v module d_trigger(rst,clk,d,q,qb); output q,qb; //qb=~q; input rst,clk,d; reg q,qb; initial begin qb=~q; end

always@(negedge rst or posedge clk) begin if(rst==0) q=0; else q=d; qb=~q; end endmodule

D_trigger testbench code

`timescale 1ns/1ns module d_trigger_tb; wire q,qb; reg clk,rst,d; initial begin rst=0; clk=0; #100 rst=1;d=0; #100 d=1; #200 rst=0;d=1; end always #100 clk=~clk; d_trigger m(.rst(rst),.clk(clk),.d(d),.q(q),.qb(qb)); endmodule

断(0) 断(0) 灭(0) 断(0) 合(1) 灭(0) 合(1) 断(0) 灭(0) 合(1) 合(1) 亮(1)

与门:灯亮=K1· K2

或门:灯亮=K1+K2

二输入与非门和或非门

R R U U K1 K2 K1

¤

K2

¤

• 与非门和或非门真值表

输入 K1 K2 输出 灯 输入 K1 K2 断(0) 断(0) 输出 灯 亮(1) 断(0) 断(0) 亮(1)

• 半导体分为

– 二极管 – MOS晶体管(三极管中的一种)

• N沟道MOS晶体管 • P沟道MOS晶体管

• N--MOS晶体管的符号如下

栅极G 栅极G(VG)

源极S

漏极D

源极S(VS)

漏极D(VD)

• 在数字电路中,MOS管工作于开关状态,相 当于一个可控开关。

MOS管状态 导通达到饱和 截止 开关状态 数字电路状态 接通 0(L—低电平) 断开 1(H—高电平)

边沿触发的D触发器

• 数据在计算机存放在下列地方:

– 运算器中的寄存器 – 主存储器(内存) – 外部存储器(外存)

• 这里介绍用Verilog HDL语言描述边沿触发的D触 发器,如下图。 输入

清除 时钟 D 输出Q L X X L H ↑ H H H ↑ L L H L X Q H H X Q

VDD=5V G(VG) S(D)

低电平(L) 典型值 范围 ≈0 <=2 ≈0 <=1.3

PMOS管

• 在数字电路中, MOS管相当于一个 开关,可控信号是 VG。如NMOS管, 当VGS>VH时NMOS 管导通。

3.1.2 逻辑门

C语言中,最基本的逻辑运算有:与运算,或 运算,非运算。 与之对应的是最基本的逻辑电路:与门,或门, 非门。 用它们可以组合出实现任何复杂的逻辑运算功 能的电路。 逻辑关系是可以采用数学公式来表示和运算的, 此数学工具就是布尔代数,又称逻辑代数。 例如,A = B * C + E * /F; A为输出(运算结果)。 B 、C、E、F为输入, * 、+、 / 分别代表与、 或、非运算符。 运算符的优先级(从高到低):非->与->或。

• 稳定状态下不允许工作于导通而又不饱和的状态 (电压不允许处在不高、不低的模糊状态)。 • 高电平或低电平的具体数值与电路结构、材料等有 关,下表为MOS数字电路的高低电平的典型值。

电源电压 (V) VD=5 VD=3.3

D G(VG) S(VS) NMOS管

高电平(H) 典型值 范围 5 >=3 3.3 >=2

断(0) 合(1) 灭(0)

合(1) 断(0) 灭(0) 合(1) 合(1) 灭(0)

或非门:灯亮=K1+K2

断(0) 合(1)

合(1) 断(0) 合(1) 合(1)

亮(1)

亮(1) 灭(0)

与非门:灯亮=K1· K2

与非门电路图

VDD VDD

VDD R

x1 x2

f

x1 x2

CMOS与非门

f x1

总线 /G1 A B /G2 C /G3 例如,当控制信号 /G1 为低电平, /G2 和 /G3 为高电平时,三态门的 输入 A 被送到总线上, 另外两个三态门的输出 处于高阻态。

计算机中常用的逻辑器件

•按是否有时序可分为:

– 组合逻辑电路的输出状态只取决于当前输入 信号的状态,与过去的输入信号的状态无关。

• 例如与门、加法器,译码器,编码器,数据选择 器等电路。

– 时序逻辑电路的输出状态不仅和当前的输入 信号的状态有关,还与以前的输入信号的状 态有关,即时序逻辑电路有记忆功能。

• 最基本的记忆电路是触发器,包括电平触发器和 边沿触发器,由基本触发器可以构成寄存器,计 数器等部件。

• 从器件的集成度和功能区分: • 低集成度的、只提供专用功能的器件。

– – – – 加法器和算术逻辑单元 译码器和编码器 数据选择器 触发器和寄存器、计数器

• 高集成度的、现场可编程的通用功能电路 (阵列逻辑电路)

– – – – 存储器芯片 RAM 和 ROM 通用阵列逻辑 GAL 复杂的可编程逻辑器件 CPLD: MACH器件 现场可编程门阵列 FPGA 器件

一、时序电路 R-S 触发器

与门 X=A•B

A B 0 0 0 1 1 0 1 1

X 1 1 1 0

A B

与非门

X

Using C function code

//logic and function bool and(bool x,bool y) { return x && y; }

//test file include<stdio.h> int main() { int i,x,y; for(i=0;i<4;i++) { x=i%2; y=i/2; printf(―%d && %d=%d\n‖,x,y,and(x,y)); } return 0; }

触发器是典型的时序逻 辑电路,有记忆功能,最 简单的可以由两个交叉耦 合的 “与非”门组成的 R-S 触发器,2 个输出分 别为 Q和 /Q,两路输入分 别为 R 和 S。

/Q Q

现态 S R Qn

次态 Qn+1

说明

S

R

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

非门(NOT)

R

VDD

VDD

非门的主要功能是对 输入信号求反。其布 尔表达式为 f= x

R

f x

NMOS非门

f x

CMOS非门

f

K

非门真值表 输入 x 输出 f L(0) H(1)

U

¤

x

非门符号

H(1)