12位AD转换器与单片机的接口电路设计要点

12位AD转换器与单片机的接口电路设计

12位AD转换器与单片机的接口电路设计AD转换器是具有高度集成化电路的模数转换器。

它将模拟信号转换

为数字信号,这种转换是实现模拟与数字系统的接口,实现模拟信号的采

集与处理的必要前提。

常用的AD转换器有12位AD转换器,它与单片机的接口电路设计包括:

1、驱动电路。

12位AD转换器与单片机之间需要通过电压驱动线在

两个芯片间传送模拟电压信号。

为了节省电源能量损耗,一般采用低功耗、高精度的滤波电路来保证电压平稳、不受外界干扰。

2、AD转换器控制信号。

模数转换器本身需要诸如转换触发、转换完成、复位和读取等一系列控制信号,控制信号的设计通常采用三态逻辑。

3、电压信号转换。

常用的12位AD转换器输出的是2的12次方个电

压信号值,而单片机的数据输入室通常是8位或者16位的二进制码,在

此种情况下,需要将AD转换器输出的电压信号转换为可识别的数字信号,这就需要设计一个称为电压转换器的电路。

4、时钟控制电路。

AD转换

模拟电压输入 1LSB

模拟电压输入 1/2LSB

5

3、偏移误差

偏移误差是指输入信号为零时,输出信号不为零的 值,所以有时又称为零值误差。假定ADC没有非线 性误差,则其转换特性曲线各阶梯中点的连线必定 是直线,这条直线与横轴相交点所对应的输入电压 值就是偏移误差。

积分器输出

VIN

时钟

T1 T T2

t

3

三、A/D转换器的主要技术指标 1、分辨率 ADC的分辨率是指使输出数字量变化一个 相邻数码所需输入模拟电压的变化量。常用 二进制的位数表示。例如12位ADC的分辨率 就是12位,或者说分辨率为满刻度FS的 1/2 1 2 。一个10V满刻度的12位ADC能分辨输 入电压变化最小值是10V×1/ 2 1 2 =2.4mV。

ADC_CONTR寄存器

ADC_RES、 ADC_RESL寄存器

ADC中断控制寄存器

ADC典型应用电路

电压基准源

ADC实现按键输入功能

10VIN 20VIN AG

CE STS

-5V~+5V -10V~+10V

23

采用双极性输入方式,可对±5V或±10V的模拟信号

进行转换。当AD574A与80C31单片机配置时,由于 AD574A输出12位数据,所以当单片机读取转换结果 时,应分两次进行:当A0=0时,读取高8位;当A 0=1时,读取低4位。

需三组电源:+5V、VCC(+12V~+15V)、

VEE(-12V~-15V)。由于转换精度高,所 提供电源必须有良好的稳定性,并进行充分滤波, 以防止高频噪声的干扰。 低功耗:典型功耗为390mW。

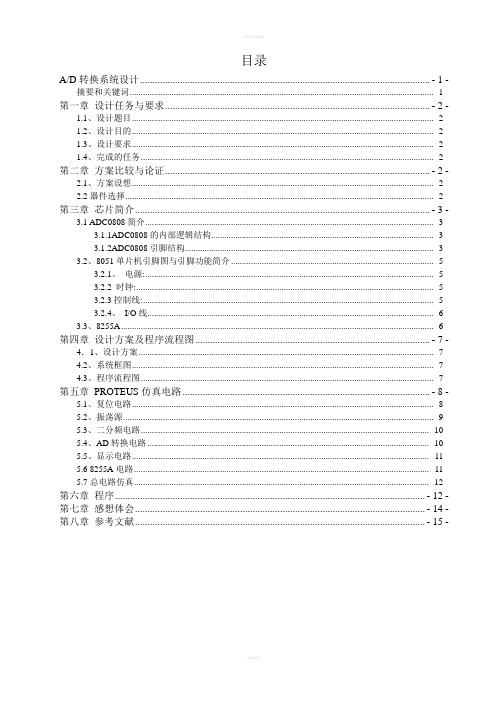

单片机课程设计---AD转换系统设计

目录A/D转换系统设计.................................................................................................................... - 1 -摘要和关键词.......................................................................................................................................... - 1 - 第一章设计任务与要求.......................................................................................................... - 2 -1.1、设计题目......................................................................................................................................... - 2 -1.2、设计目的......................................................................................................................................... - 2 -1.3、设计要求......................................................................................................................................... - 2 -1.4、完成的任务..................................................................................................................................... - 2 - 第二章方案比较与论证.......................................................................................................... - 2 -2.1、方案设想......................................................................................................................................... - 2 -2.2器件选择............................................................................................................................................ - 2 - 第三章芯片简介...................................................................................................................... - 3 -3.1 ADC0808简介................................................................................................................................... - 3 -3.1.1ADC0808的内部逻辑结构..................................................................................................... - 3 -3.1.2ADC0808引脚结构................................................................................................................. - 3 -3.2、8051单片机引脚图与引脚功能简介 ............................................................................................ - 5 -3.2.1、电源: ................................................................................................................................... - 5 -3.2.2 时钟: ....................................................................................................................................... - 5 -3.2.3控制线: .................................................................................................................................... - 5 -3.2.4、I/O线.................................................................................................................................. - 6 -3.3、8255A .............................................................................................................................................. - 6 - 第四章设计方案及程序流程图.............................................................................................. - 7 -4.1、设计方案...................................................................................................................................... - 7 -4.2、系统框图......................................................................................................................................... - 7 -4.3、程序流程图..................................................................................................................................... - 7 - 第五章PROTEUS仿真电路................................................................................................... - 8 -5.1、复位电路......................................................................................................................................... - 8 -5.2、振荡源............................................................................................................................................. - 9 -5.3、二分频电路................................................................................................................................... - 10 -5.4、AD转换电路 ................................................................................................................................ - 10 -5.5、显示电路....................................................................................................................................... - 11 -5.6 8255A电路...................................................................................................................................... - 11 -5.7总电路仿真...................................................................................................................................... - 12 - 第六章程序............................................................................................................................ - 12 -第七章感想体会.................................................................................................................... - 14 -第八章参考文献.................................................................................................................... - 15 -A/D转换系统设计摘要和关键词A/D转换是指将模拟信号转换为数字信号,这在信号处理、信号传输等领域具有重要的意义。

单片机第10章 AD-DA转换与单片机接口技术

10 11 30 29

U4

D0 D1 D2

3 4 7 8 13 14 17 18

D0 D1 D2 D3 D4 D5 D6 D7

第十章 A/D、D/A转换与单片机接口技术

10.0 你知道吗 10.1 A/D转换器及其与单片机的接口 10.2 D/A转换器及与单片机的接口

你知道吗 在自动控制领域中,通常用单片机进行实时控制和数据处理,我们知道,被 测和被控参数常常是一些连续变化的物理量即模拟量,如温度、速度、电压、 电流、压力等,而单片机只能加工和处理数字量,因此在单片机应用系统中处 理模拟量信号时,就需要进行模拟量与数字量之间的转换,即A/D和D/A转换。

二、双积分式A/D转换原理

双积分A/D转换采用间接测量原理,即将被测电压值VX转换成时间常数,通过测量 时间常数得到未知电压值。其原理如下图所示。它由电子开关、积分器、比较 器、计数器、逻辑控制门等部件组成。

积分器

由于双积分的二次积分时间比较长,因此

Vx VR

比较器

A/D转换速度慢,但精度高。

计数器 输出

五、ADC0809与单片机的接口电路

R1

D1

R2

D2

R3

D3

R4

D4

D5

R5

R6

D6

R7

D7

R8

D8

U1

P10 P11

P10 1 P11 2 P12 3 P13 4 P14 5 P15 6 P16 7 P17 8

P10 P11 P12 P13 P14 P15 P16 P17

P12

13 12

INT1 INT0

ADD-A﹑ADD-B﹑ADD-C:3根地址线。ADD-A为低位地址,ADD-C为高位地址, 用于选择8路模拟量,其地址状态与所选模拟量的对应关系见表10.1。 D0~D7:8位数字量输出端。 ALE:地址锁存允许信号,ALE为高电平时,将ADD-A﹑ADD-B﹑ADD-C的地址 状态送入地址锁存器中。

过程输入输出通道详解

3.1.1 数字量输入通道

2.输入调理电路 数字量输入通道的基本功能就是接收外部装 置或生产过程的状态信号。这此状态信号的 形式可能是电压、电流、开关的触点,容易 引起瞬时高压、过电压、接触抖动等现象。 为了将外部数字量信号输入到计算机,必须 将现场输入的状态信号经转换、保护、滤波、 隔离等措施转换成计算机能够接收的逻辑电 平信号,这些过程称为信号调理。下面针对 不同情况分别介绍相应的信号调理技术。

3.1 数字量输入输出通道

3.1.1 数字量输入通道

1.数字量输入通道的结构 数字量输入通道的结构 数字量输入通道将现场开关信号转换成计算机需要的电平号, 数字量输入通道将现场开关信号转换成计算机需要的电平号, 以二进制数字量的形式输入计算机, 以二进制数字量的形式输入计算机,计算机通过三态缓冲器读 取状态信息。数字量输入通道主要由输入调理电路、 取状态信息。数字量输入通道主要由输入调理电路、输入缓冲 器和接口电路组成。如图3-1所示 所示。 器和接口电路组成。如图 所示。 图3-1 数字量输入通道结构

3.2.3采样保持器

2、常用的采样保持器 图3-18 LF398的典型应用 的典型应用

3.2.3采样保持器

3、采样/保持器的主要参数 ●采集时间(捕捉时间):当置于采样方式时,输出跟 踪输入需要的时间。采集时间T是指从采样开始到输出 稳定之间的时间。 ●转换速率:指输出变化的最大速率,以V/s为单位。 V/s ●孔径时间:当采样保持器从采样转入保持时,采样开 关完全断开所需的时间,即进入保持控制后,实际的 保持点会滞后真正要求保持点一段时间,一般是纳秒 级。这个时间由器件的开关动作时间决定。 ●下跌率(衰减率):在进入保持阶段后,由于开关的 漏电流及保持电容泄漏,输出电压会下降,以mV/s表 示。在选择保持电容的容量时要折中地考虑采集时间 和下跌率。

基于STM32处理器的数控电源设计

基于ARM处理器的数控电源设计摘要:电源是现代完成产品设计的最基本工具之一。

在现代科学研究和工业生产中, 制作低纹波、高精度的稳定直源有非常重要的意义。

本文详细论述了基于ARM处理器的数控电源设计的设计过程,详细介绍了每个模块的工作原理。

本设计基于ARMv7-M体系结构STM32F130VCT6单片机作为主控制系统,配合12位AD、DA、EEPOM、RTC时钟、设计相应的模拟数字硬件电路。

关键词:数控电源,ARM,12位AD,12位DADigital power supply design based on ARM processorAbstract: Power is the most basic of modern product design to complete one of the tools. In modern scientific research and industrial production, theproduction of low ripple, high accuracy and stability are very importantdirect source of meaning. This paper describes the ARMprocessor-based design of digital control power supply design, detailthe working principle of each module. The design is based onARMv7-M architecture STM32F130VCT6 MCU as the master controlsystem, with 12-bit AD, DA, EEPOM, RTC clock, the appropriatedesign of analog and digital hardware circuit.Key words:digital prower ,arm , 12bitAD, 12bitDA1前言低纹波、高精度稳定直源就是一种非常重要的特种电源,在现代科学研究和工业生产中得到了越来越广泛的应用,同时对电源控制数字化和智能化, 实时处理大量信息, 实现电压、电流、频率、相位、波形等参数的精确控制和高效率处理来获得高性能的电源是电源设计技术的重要趋势。

12位双路同时转换A_D转换器AD7862及其应用

收稿日期:2003203209 第一作者 曹庆文 男 26岁 硕士研究生12位双路同时转换A/D 转换器AD 7862及其应用曹庆文1 张东海2 李宁1(1.西安交通大学,陕西西安710049;2.晋中供电局,山西晋中030600)摘 要:AD 7862是美国AD 公司推出的一种12位4通道双路同时采样转换高速模数转换器。

文中介绍了它的性能特点,内部结构,工作时序,以及在介损角测量中的应用,并详细给出了其与单片机的接口及C 51语言的应用程序。

关键词:同时采样;模数转换;单片机;C 51语言中图分类号:TN 47 文献标识码:A引言介质损耗角是衡量电力设备绝缘性能的一个重要指标,其可以反映出高压电力设备绝缘一系列缺陷,如绝缘受潮,老化变质绝缘气隙放电等。

因此,监控设备要及时准确的对电力设备的介质损耗角进行检测。

本文研制的电容型设备介损检测仪采用了2路同时采样的AD7862转换器对试品运行电压和流经试品电流进行同时检测,实际运行取得了良好的效果。

1 AD 7862芯片的主要特点及引脚AD 7862是AD 公司推出的12位AD 转换芯片,具有以下主要特点:a )4通道模拟输入,2路同时转换(内置2个可同时工作的12位集成AD 转换器);b )4μs 转换时间,250ksps 采样速率;c )可选择模拟量输入范围:±10V (AD 7862-10),±5V (AD 7862-3),0~2.5V(AD 7862-2)d )高速12位并行总线输出;e )内部提供+2.5V 参考电压或者由外部提供参考电压;f )单一电源+5VAD 7862的引脚封装如图1所示。

2 芯片工作原理AD 7862内部结构框图如图2所示。

AD 7862内部集成两个可以同时工作的12位AD 转换器,两个同步跟踪/保持放大器分别与一个2选1电路连接,因此可以实现AB 两组通道(V A 1、V A 2与V B 1、V B 2)中任何一组的2路模拟输入同时采样。

12位ad转换器max187原理及应用

万方数据

12位A/D转换器MAX187原理及应用

作者: 作者单位: 刊名:

英文刊名: 年,卷(期): 引用次数:

张岳涛, 史翔, ZHANG Yuetao, SHI Xiang 西安科技大学,陕西,西安,710054

现代电子技术 MODERN ELECTRONICS TECHNIQUE 2007,30(10) 0次

;转换结果高4位读取

A,#OFH 21H,A R2,#08H

,21H单元高4位清零

P1.O

P1.0

C。P1.1 A。20H

A 20H.A

R2,REC2

;转换结果低8位读取

DPTR,#OFFFFH

A,#OOH

@DPTR,A ;CS置高电平,转换结束

START

R3.OAH R3,¥

,10弘s延时子程序

图3硬件原理图

万方数据

要特别注意的是,SCLK的最高频率是5 MHz,在编写程 序时需注意与系统时钟的匹配问题。

o—_1厂—]

州1 州

பைடு நூலகம்

几

几几几f1几n几几几几几开几n几几九

f——匿短砸髓残豇萤回回回回回回广_1

—·晴糖,哪—D’'I-+器_器-警-骞l·—I+哦+8卜眇.—I一+_糠一MM啉_—_——+I霉-:l挚I+.一-衄 _m'

6.期刊论文 杜继伟.王庆智.邓志辉.DU Ji-wei.WANG Qing-zhi.DENG Zhi-hui 基于89C2051和MAXl87的变焦镜头控

制器的设计 -航空兵器2008(2)

可变焦一体化CCD摄像机是光电跟踪仪的关键部件之一,担负着图像采集的任务.本文介绍了可变焦一体化CCD摄像机中的一种基于89C2051单片机和 MAXl87 A/D转换器的变焦镜头控制器进行变焦和聚焦控制,以及焦距反馈的原理及实现方法.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书2012/2013 学年第 1 学期学院:电子与计算机科学技术学院专业:学生姓名:学号:课程设计题目:12位A/D转换器与单片机的接口电路设计起迄日期:课程设计地点:指导教师:系主任:下达任务书日期: 2012年 12月 19日课程设计任务书课程设计任务书目录第一章设计任务及功能要求 (5)1.1摘要 (5)1.2设计课题及任务 (5)1.3功能要求及说明 (5)第二章硬件设计 (6)2.1 系统设计元器件功能说明 (7)2.2 硬件电路总体及部分设计 (10)第三章软件设计 (12)3.1 基本原理内容设计 (12)3.2 keil编程调试 (13)3.3 proteus仿真电路图 (19)第三章结果分析及总结 (19)附录 (20)第一章设计任务及功能要求1.1摘要近年来随着科技的飞速发展,单片机的应用正在不断的走向深入,单片机对我们的生活影响越来越大,很多工业领域中都用到单片机,日常生活中我们也离不开单片机的应用。

当今社会是数字化的社会,是数字集成电路广泛应用的社会,随着电子产业数字化程度的不断发展,逐渐形成了以数字系统为主体的格局。

A/D和D/A转换器作为模拟和数字电路的借口,正受到日益广泛的关注。

随着数字技术的飞速发展,人们对A/D和D/A 转换器的要求也越来越高,新型模拟/数字和数字/模拟之间的转换技术不断涌现,正是因为这些,高集成度的逻辑器件应运而生,而且发展迅速,它不断地更新换代以满足程序的要求,并尽可能的提高其利用率。

本课程设计就对其中AD574模数转换器在微机数据采集系统中的应用加以阐述。

关键字:AD574转换器,80c51单片机,LED数码显示,串行输出1.2 设计课题及任务1.掌握电子电路的一般设计方法和设计流程;2.学习简单电路系统设计,掌握Protel99的使用方法;3.掌握8051单片机、12位A/D芯片AD574的应用;4.学习掌握硬件电路设计的全过程。

1.3 功能要求及说明1.学习掌握8051单片机的工作原理及应用;2. 学习掌握12位A/D芯片AD574的工作原理及应用;3. 设计基于AD574的12位模拟信号采集器的工作原理图及PCB版图;4. 整理设计内容,编写设计说明书。

5.Protues仿真。

第二章硬件设计2.1系统设计元器件功能说明12位AD574功能及引脚说明AD574A是美国模拟数字公司(Analog)推出的单片高速12位逐次比较型A/D转换器,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器,其主要功能特性如下:分辨率:12位非线性误差:小于±1/2LBS或±1LBS转换速率:25us模拟电压输入范围:0—10V和0—20V,0—±5V和0—±10V两档四种电源电压:±15V和5V数据输出格式:12位/8位芯片工作模式:全速工作模式和单一工作模式AD574A的引脚说明:[1]. Pin1(+V)——+5V电源输入端。

[2].Pin2()——数据模式选择端,通过此引脚可选择数据纵线是12位或8位输出。

[3]. Pin3()——片选端。

[4]. Pin4(A0)——字节地址短周期控制端。

与端用来控制启动转换的方式和数据输出格式。

须注意的是,端TTL电平不能直接+5V或0V连接。

[5]. Pin5()——读转换数据控制端。

[6]. Pin6(CE)——使能端。

现在我们来讨论AD574A的CE 、、、和A0对其工作状态的控制过程。

在CE=1、=0同时满足时,AD574A才会正常工作,在AD574处于工作状态时,当=0时A/D 转换,当=1是进行数据读出。

和A0端用来控制启动转换的方式和数据输出格式。

A0-0时,启动的是按完整12位数据方式进行的。

当A0=1时,按8位A/D 转换方式进行。

当=1,也即当AD574A处于数据状态时,A0和控制数据输出状态的格式。

当=1时,数据以12位并行输出,当=0时,数据以8位分两次输出。

而当A0=0时,输出转换数据的高8位,A0=1时输出A/D转换数据的低4位,这四位占一个字节的高半字节,低半字节补零。

其控制逻辑真值表见表1。

[7]. Pin7(V+)——正电源输入端,输入+15V电源。

[8]. Pin8(REF OUT)——10V基准电源电压输出端。

[9]. Pin9(AGND)——模拟地端。

[10]. Pin10(REF IN)——基准电源电压输入端。

[11]. Pin(V-)——负电源输入端,输入-15V电源。

[12]. Pin1(V+)——正电源输入端,输入+15V电源。

[13]. Pin13(10V IN)——10V量程模拟电压输入端。

[14]. Pin14(20V IN)——20V量程模拟电压输入端。

[15]. Pin15(DGND)——数字地端。

[16]. Pin16—Pin27(DB0—DB11)——12条数据总线。

通过这12条数据总线向外输出A/D转换数据。

[17]. Pin28(STS)——工作状态指示信号端,当STS=1时,表示转换器正处于转换状态,当STS=0时,声明A/D转换结束,通过此信号可以判别A/D转换器的工作状态,作为单片机的中断或查询信号之用。

AD574A的工作模式:以上我们所述的是AD574A的全控状态,如果需AD574A工作于单一模式,只需将CE 、端接至+5V电源端,和A0接至0V ,仅用端来控制A/D转换的启动和数据输出。

当=0时,启动A/D转换器,经25us后STS=1,表明A/D 转换结束,此时将置1,即可从数据端读取数据。

74LS373八D 锁存器(3S,锁存允许输入有回环特性) 简要说明: 373为三态输出的八 D 透明锁存器,共有54/74S373 和54/74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):373 的输出端O0~O7 可直接与总线相连。

当三态允许控制端OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,O 随数据 D 而变。

当LE 为低电平时,O 被锁存在已建立的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

引出端符号:D0~D7 数据输入端OE 三态允许控制端(低电平有效)LE 锁存允许端O0~O7 输出端外部管腿图:逻辑图:真值表:极限值: 电源电压…………………………………………. 7V 输入电压54/74S373…………………………….…………. 5.5V 54/74LS373……………………………………. 7V 输出高阻态时高电平电压…………………………. 5.5V 工作环境温度54XXX …………………………………. -55~125℃74XXX …………………………………. 0~70℃存储温度…………………………………………. -65~150℃2.2硬件电路总体及部分设计图2.2.1 单片机的内部晶振图2.2.2 数码管显示图2.2.3 74373的接口设计图2.2.4 AD574接口图第三章软件设计3.1 硬件电路总体及部分设计AD574A的接口电路8051单片机与AD574A的接口电路,其中还使用了三态锁存器74LS373和74LS00与非门电路,逻辑控制信号由(、和A0)有8051的数据口P0发出,并由三态锁存器74LS373锁存到输出端Q0、Q1和Q2上,用于控制AD574A的工作过程。

AD转换器的数据输出也通过P0数据总线连至8051,由于我们只使用了8位数据口,12位数据分两次读进8051,所以接地。

当8051的p3.0查询到STS端转换结束信号后,先将转换后的12位A/D数据的高8位读进8051,然后再将低4位读进8051。

这里不管AD574A是处在启动、转换和输出结果,使能端CE都必须为1,因此将8051的写控制线和读控制线通过与非门74LS00与AD574A的使能端CE相连3.2Keil编程#include<reg51.h>#include<intrins.h>#define uint unsigned int#define uchar unsigned char sbit ADout=P1^0;sbit ADin=P1^1;sbit CS=P1^2;sbit CLK=P1^3;sbit EOC=P1^4;sbit LE=P1^6;sbit LE2=P1^7;duan[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x7c };uchar D=0,wei[]={0xfe,0xfd,0xfb,0xf7,0xdf,0xef};float k,z;uint n;//////////延时子函数void delay(uint us){uchar i;for(i=0;i<us;i++)_nop_();}////////数码管显示子函数void display(uint AD){uchar q,b,s,g; //////千位、百位、十位、个位q=AD/1000;b=AD/100%10;s=AD/10%10;g=AD%10;P0=0xff; LE1=1;P0=wei[0]; LE1=0;LE2=1;P0=duan[q]; LE2=0; delay(10);P0=0xff; LE1=1;P0=wei[1]; LE1=0;LE2=1;P0=duan[b]; LE2=0; delay(10);P0=0xff; LE1=1;P0=wei[2];LE1=0;LE2=1;P0=duan[s];LE2=0;delay(10);P0=0xff;LE1=1;P0=wei[3];LE1=0;LE2=1;P0=duan[g];LE2=0;delay(10);}///////TLC2543转换和读取子函数,只转换了三路模拟电压信号。

uint readAD(uchar port){uchar ch,i,j;uint ad;ch=port;for(j=0;j<3;j++){ad=0;ch=port;EOC=1;CS=1;CS=0;CLK=0;for(i=0;i<12;i++){if(ADout) ad|=0x01;ADin=(bit)(ch&0x80);CLK=1;CLK=0;ch<<=1;ad<<=1;}}CS=1; //转换和读取数值while(!EOC);ad>>=1;return(ad);}//主函数void main(){while(1){n=readAD(0x00); //得到通道0的数值k=readAD(0x10); //得到通道1的数值z=readAD(0x20); //得到通道2的数值display(n); //显示一路// display(k);// display(z);}}3.3 proteus仿真Proteus 仿真图及其pcb板见附录。