深亚微米下低功耗设计方法

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

深亚微米下低功耗设计方法

1.低功耗设计研究的背景和意义

自从晶体管的发明以来,集成电路的发展经历了从手工设计阶段、小规模集成电路设计阶段、大规模集成电路设计阶段以及现在的超大规模集成电路的设计阶段。特征尺寸的不断缩小可以使得单个片上系统可以集成更多的晶体管. 特征尺寸的发展经历了0.35um到0.18um的深亚微米阶段以及90nm、65nm、40nm、28nm、的超深亚微米阶段。

如今设计的芯片需要处理的数据量是巨大的,处理速度己达到的GHz水平, 处理器的处理速度和处理数据的能力都得到了很大的提高,单个芯片上集成的晶体管数目已经达到上亿级别。这些晶体管在单个芯片上按照GHz的频率运行时会产生大量功耗,以前设计的芯片只考虑芯片的时序和面积方面,而很少考虑功耗的因素,超深亚微米下,阈值电压也随之降低,导致亚阈值电流也随之增大,如下静态泄漏功耗可以达到动态功耗的水平。因而,功耗已经成为制约芯片朝着高速、高集成度方向发展的重要因素,功耗的大量增加会导致芯片工作状况的下降,影响芯片的质量,低功耗设计技术应运而生,成为集成电路设计工程师所必须掌握的设计技术。

2.低功耗技术的研究情况

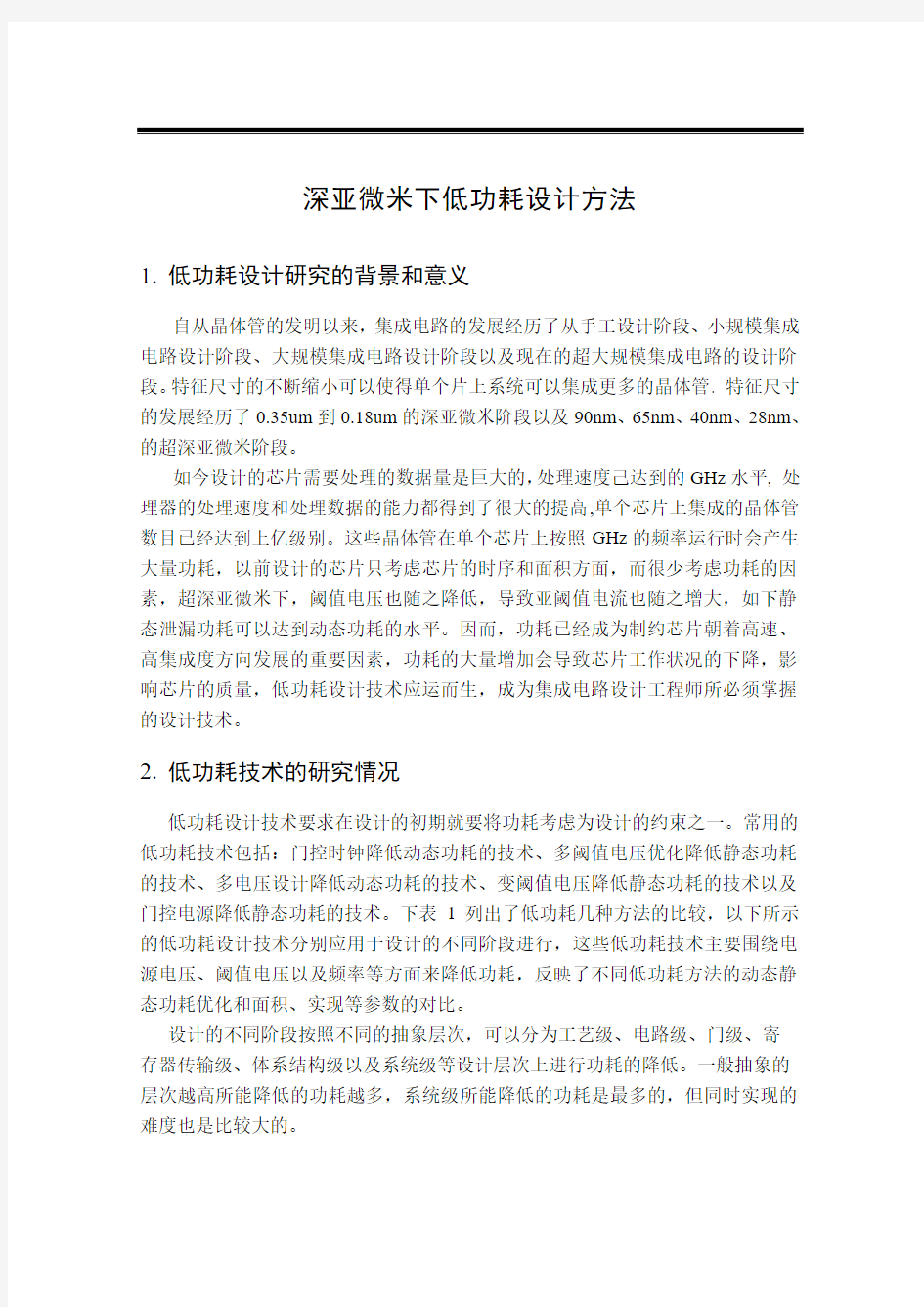

低功耗设计技术要求在设计的初期就要将功耗考虑为设计的约束之一。常用的低功耗技术包括:门控时钟降低动态功耗的技术、多阈值电压优化降低静态功耗的技术、多电压设计降低动态功耗的技术、变阈值电压降低静态功耗的技术以及门控电源降低静态功耗的技术。下表1列出了低功耗几种方法的比较,以下所示的低功耗设计技术分别应用于设计的不同阶段进行,这些低功耗技术主要围绕电源电压、阈值电压以及频率等方面来降低功耗,反映了不同低功耗方法的动态静态功耗优化和面积、实现等参数的对比。

设计的不同阶段按照不同的抽象层次,可以分为工艺级、电路级、门级、寄

存器传输级、体系结构级以及系统级等设计层次上进行功耗的降低。一般抽象的层次越高所能降低的功耗越多,系统级所能降低的功耗是最多的,但同时实现的难度也是比较大的。

表格 1 几种低功耗方法比较影响

低功耗设计

方法静态

功耗

动态功耗

时序

牺牲

面积

牺牲

对实现方法的影响

架构设计验证实现

多阈值优化6倍0 少少无低无低门控时钟0 20% 一些少无低低中等多电源电压

设计

2倍40%-50% 一些少高中等中等高

电源门控10-50

倍

0 一些一些高高高高

动态电压频

率调节技术

2-3倍40%-70% 一些一些高高高高3.深亚微米下电路功耗的来源

3.1.动态功耗

动态功耗主要包括开关功耗和内部功耗。开关功耗为电路结点翻转的时候向各个电路结点电容充电或者放电时所产生的功耗,其为动态功耗的主要來源。对于较大尺寸工艺下,开关功耗被认为是主要功耗来源。内部功耗是指在器件内部消耗的功耗,包括内部短路功耗和内部开关功耗。内部短路功耗为内部功耗的主要部分。内部短路功耗是指管和管由于同时导通而消耗的功耗。

3.2.静态功耗

图 1静态功耗来源

静态功耗是指电路处于等待或不工作状态时泄露电流所产生的功耗。主要包括亚阈值漏电流功耗、反向偏置的二极管泄漏电流、CMOS门栅感应漏极泄漏电流和CMOS管栅极泄漏电流,具体如图1所示。

4.低功耗设计方法分析

4.1.制造工艺级低功耗方法

晶体管尺寸的减少提高了系统的集成度,降低了供电电压,减小了芯片内部的寄生电容,从而有效的减少了芯片的动态功耗。但是为了满足电路的性能,阈值电压随着供电电压的下降而下降,静态功耗反而增加,为了降低静态功耗,开发出了多阈值电压的库,在不影响芯片性能的前提下尽量降低静态功耗。还有

采用变阈值电压工艺,利用CMOS电路的衬底偏置效应动态的改变器件的阈值电压,从而可以节省芯片的静态功耗。近年来,采用铜互连技术和低介质常数减少了互连线的电阻和寄生电容,在栅极方面,采用高介电常数取代二氧化硅和采用金属栅极取代多晶硅栅极,降低了栅极的电阻和寄生电容,降低了栅极的漏电流。另外利用倒装芯片技术等封装连接技术可以大大减小I/O口的静态功耗。

4.2.电路级的低功耗方法

4.2.1.多电源电压技术

对于一个设计可以分为不同的区域,不同的区域提供不同的供电电压,如可以将一个设计划分为存储器模块、嵌入式处理器模块以及其它的逻辑模块。这样不同的模块根据性能的要求不同可以使用不同的供电电压,从而可以有效的降低芯片的动态功耗。需要提供电平转换单元(Level Shifted)用于不同的电压域(Power Domin)之间进行信号的传递,包括从低电压域的信号传递到高电压域的电平转化单元和从高电压域的信号传递到低电压域的电平转化单元。

4.2.2.路径平衡技术

在组合逻辑电路中,对于一个逻辑门来说其多个输入端的信号到达时间由于路径延时的不同而不同,这样会产生所谓的竞争冒险现象,即在逻辑门的输出为稳定的逻辑值之前会有毛刺产生。毛剌为短暂的跳变信号,对于同歩电路来说只要毛刺不出现在时钟电路上并且满足建立和保持时间就不会对同歩电路的逻辑功能造成影响,但是毛刺的出现会增加电路的跳变次数从而增加电路的动态功耗。

通过采用路径平衡的技术使得到达逻辑门的信号之间的延时一致从而减少毛刺的产生,减少了电路的翻转率,从而降低了电路的动态功耗。常见的路径平衡技术如减少路径的延迟级数,使得路径级数相一致,从而使得信号的延时一致。

4.3.门级低功耗技术

4.3.1.门级电路的功耗优化

门级电路的功耗优化主要用在后端布局布线的歩骤中,用于对己经映射过的门级网表所进行的优化。比如改变逻辑门的驱动能力,交换引脚、技术映射、相位分配、插入缓冲器等方法。

4.3.2.多阈值电压功耗技术

随着工艺的减小,电源电压,工艺尺寸等都按照比例缩小,阈值电压的降低会导致漏电流增大,电路的静态功耗增大,所以在深亚微米下工艺厂商提供多阈值电压库的方法减小功耗。低阈值电压的单元库具有高的静态漏电流,但速度快;高阈值电压的単元库具有低的泄漏电流,但速度慢;标准阈值的电压库是泄漏电流和阈值电压的折中。在逻辑综合和后端布局布线的过程中,我们采用多阈值电压的优化方法,在关键路径上采用标准阈值的电压库和低阈值的电压库尽量满足芯片速度的要求,而在非关键路径有时序余量的情况下尽量采用高阈值的电压库。

4.4.寄存器传输级(RTL)的低功耗设计

RTL级的低功耗技术主要用于降低芯片的动态功耗,其主要的贡献为降低电路结点的翻转率,从而降低电路的动态功耗。由于时序电路是基于触发器来实现的,而触发器的运行是通过时钟信号的翻转来控制的。时钟网络的周期性的翻转同时时钟网络庞大的负载导致了时钟网络的功耗占据了芯片动态功耗的大部分。门控时钟的技术可以控制触发器的时钟的关断,即将空闲的寄存器的时钟关断,从而减少时钟网络的翻转以及寄存器的工作。如图为一个插入门控时钟的电路。

图 2 门控时钟低功耗设计方法

4.5.体系结构级的低功耗设计

体系结构级的低功耗技术是在确定电路实现方案的时候需要考虑电路的功耗,设计出的电路在面积、速度方面会有所牺牲,但电路的功耗可以大大的得到降低,常见的结构体系功耗技术主要包括并行结构和流水线结构这两种常见的降低功耗的技术。

4.5.1.并行结构低功耗技术

并行结构是指将原来一条数据通路的工作分解为在两条通路上完成,如将一个功能模块复制为两个模块,这样两个模块同时并行的工作,大大提高了数据的吞