基于IEEE1801(UPF)标准的低功耗设计实现流程

低功耗系统设计(单片机)

休眠模式(内核、外设关闭时钟):适于短时间循环、频繁唤醒、需外设唤醒源、需要ADC/比较器模拟采样

深度休眠(内核、稳压器、外设、RAM掉电):适于长时间休眠、无需外设、最小电流精确计算、极端温度

片上高速振荡器(INTOSC)

可扩展时间看门狗(WDT)

总功耗Ptotal=PddInt+PddExt+PddRtc

电路隔离技术

光耦合:数字信号——LED——光电二极管——数字信号,抗干扰强、允许恒定值传输,速度限制、功耗、LED老化

电感耦合:变压器,高效率,抗干扰差、数据需编码

电容耦合:电场传输,尺寸小、效率高、抗磁场干扰强,无差分信号、噪声容限差

O:引脚数

f:引脚最大频率

Cl:引脚负载电容

U:使用系数(外设运行比例)

外部功耗PddExt=VddExt*IddExt=O*f/2*VddExt^2*Cl*U

实时时钟功耗(PddRtc)

PddRtc=VddRtc*IddRtc

超低功耗唤醒

定时器/辅助振荡器

时钟切换:非关键代码使用内部振荡器(慢),关键代码使用高精度振荡器(快)

功耗预算:不同模式功耗和持续时间

功耗估算:电源电压、内核频率、节点温度

内部பைடு நூலகம்耗(VddInt):动态(指令执行、操作数、速率)+静态(温度、电压)

IddIdle、IddNop、IddTyp(产生IddBaseline)、IddApp(特定应用下)、IddHigh、IddPeak

NOR Flash(程序):低电压、待机(无片选信号)、自动休眠(地址不变)

串行接口(RS232C):关断模式

以太网接口:网卡芯片(连接到总线)、含以太网接口(无网卡,带低功耗模式)

低功率设计中不同功率格式的应用

低功率设计中不同功率格式的应用对于低功率设计,既然存在两种相互竞争的获取功率目的的行业格式——共同功率格式(CPF)和统一功率格式(UPF)——设计组必须理解这两种格式之间的相似点和不同点。

有些设计公司可能会忽视其中的一种格式,但是大部分设计公司将同时使用两种格式。

CPF文件格式的第一个参考文献出现在2006年早期,Cadence宣布了它的Power Forward Initiative。

2006年后期,Cadence和Silicon Integration Initiative公司(Si2)在Si2的资助下创建了低功率联盟(LPC),专注于发展CPF格式。

2007年1月,LPC公布了包含CPF格式定义的第一个公开文件。

该文件可在 网站下载。

Cadence的软件组支持CPF,多个EDA卖主也支持LPC文件中定义的格式。

在DAC 2006年,在德州仪器和诺基亚公司带领下,许多其他公司通过会议创建了由泛EDA公司支持的第二种格式。

这一格式称作统一功率格式,而Accellera组建了一个委员会来敲定所有的细节。

2007年1月,Accellera公布了它的UPF 1.0说明书。

这一文件公布在 网站。

2008年1月Magma,Mentor,以及Synopsys公司联合宣称在他们的软件中支持UPF。

并且再次,许多其他EDA卖家也支持这一格式。

在2007年间,IEEE组建了一个工作组来开发一种行业标准的以功率为目的的格式。

这个标准将叫做IEEE-P1801。

该工作组接受以现有格式的贡献为起点。

Accellera公司贡献了UPF,但是Cadence却没有贡献CPF。

格式的相似点CPF和UPF格式采用完全不同的句法,却有90%相同的概念。

但是在任意一格式中,都有用于低功率设计的功率目的的所有主要特征。

两种格式都基于Tcl——嵌入多数EDA软件的软件控制语言。

因此,我们可以把任意一种格式当作一组Tcl的程序定义,而不是一种新的独特的语言。

验证方法学论文集,面试专用

低功耗验证解决方案August 20, 2010林雪梅linxuemei@王凤海wangfenghai@王欣 wangxin@中星微电子有限公司摘要随着便携性要求的提高,低功耗设计的需求推动了低功耗设计技术在多电压,电压内部管理等技术上的突破。

以MTCMOS/ AVS等一系列技术为代表的设计方案越来越多的应用,让传统的数字电路验证技术受到了越来越大的挑战。

本文通过对现有解决方案的应用,将介绍如何引入业界标准的UPF流程完成多项低功耗设计的验证,以确保电源管理的正确实现。

ABSTRACTAs the requirements of portal devices keep increasing, new design techniques, including multi-voltage, MTCMOS, AVS, etc., are adopted in many low power devices. These design techniques further brings new verification challenges, which are new but critical. This paper, by applying existing solutions, introduces how to apply UPF flow, an industry standard, to verify low power designs. So the management of power supplies can be verified.1.0 简介嵌入式应用是目前SOC芯片最重要的应用之一。

在嵌入式应用,尤其是便携设备的应用中,功耗成为设计者越来越关注的因素。

20世纪80年代,大规模集成电路的发展导致了硬件描述语言(Verilog和VHDL)和综合工具的出现;到了90年代,设计复用以及IP的利用成为了IC设计经常采用的技术。

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

cadence upf 低功耗流程的仿真验证

cadenceupf低功耗流程的仿真验证本文是记录项目过程中遇到的奇巧淫技,如有遗漏或者不足,请大家改正和补充,谢谢。

随着深亚微米技术的普及与发展,leakage功耗在整个功耗中的比重越来越大,比如45nm下,已经占到了60%以上,所以低功耗解决方案应运而生。

目前已经有一套标准的低功耗设计流程,流程有CPF(cadence主导)和UPF(synopsys主导)两种,但技术趋势是UPF会大一统,所以本篇将为那些仍旧使用ncverilog而不是vcs仿真工具的苦逼们提供一些参考。

目前常用的降低低功耗的方法有四种:多电压域、时钟门控、电源关断和动态电压频率调整。

其中的时钟门控对验证影响较小,大家应该都接触过,而剩下的三个对验证工作影响较大,需要用到各个EDA厂商的低功耗解决方案。

闲话就说这么多,那么cadence如何使用upf来实现低功耗流程的仿真验证呢?第一步,先得有UPF文件,根据设计需求,使用TCL建立脚本,建立和管理独立电压源、确定隔离、建立电平漂移等,一般是设计或者后端人员书写,验证工程师当然也可以写,具体内容参考IEEE 1801。

第二步,仿真case中添加电源上电过程,使用$supply_on函数给相应VDD上电。

第三步,将UPF嵌入到仿真命令中,即:irun -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...或者1 ncvlog ...2 ncelab -lps_1801 sim.upf -lps_assign_ft_buf -lps_iso_verbose ...3 ncsim ...相关options解释如下:①-lps_1801 filename: 指定符合IEEE 1801标准的UPF文件;②-lps_assign_ft_buf: 指定assign赋值被当做buffer对待,而非默认的wire,好处是从always-on domain进入和穿过power-down domain的信号被force成x,便于debug;③-lps_const_aon: 对处在power-down domain并且直接和always-on domain相连接的tie-high或者tie-low constant,不使能corruption功能;默认不使用该功能;④-lps_enum_rand_corrupt:对于用户定义的enum类型数据,在电源关断后,随机从枚举列表中选择一个值作为变量值;和该命令相类似的还有-lps_enum_right, -lps_implicit_pso等,因为不常用,就不一一介绍了;⑤-lps_iso_verbose: 使能isolation的log功能,这个一般需要加上;⑥...其它的options请参考cadence的low-power simulation guide。

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

UPF低功耗设计

UPF低功耗设计

现代固态器件已经非常广泛地应用在各种应用领域,由于固态器件有

更小的尺寸、更低的成本和更好的可靠性,因此越来越多的应用和系统开

始使用固态器件来取代传统的继电器和继电器驱动器。

但是传统的继电器

驱动器可以确保完全断开电路,而电容固态器件(UPF)在断开电路时仍

然会消耗一些能量,从而降低电子系统的效率,这就是为什么系统设计者

需要关注UPF低功耗设计的原因。

首先,需要采用最佳工艺和低功耗的UPF元件。

关键是它能够降低系

统漏电流和电压,从而降低系统耗能,因此UPF元件的低功耗特性对系统

耗能的影响是非常重要的。

其次,需要考虑UPF元件在关断电路时消耗的能量,可以通过调整参

数来减少UPF元件断开电路时消耗的能量,包括调整供电电压、降低驱动

电流、调整电容固态的有效关断速度等。

再次,必须设计UPF元件断开电路时所用的时间,有的时候,UPF元

件的断开时间对系统的功耗和可靠性都有很大的影响。

最后,要通过使用主板和驱动器的技术来改善UPF元件的低功耗特性,比如使用高压主板,可以减少漏电流,降低系统能耗;同时使用低驱动电

流的驱动器。

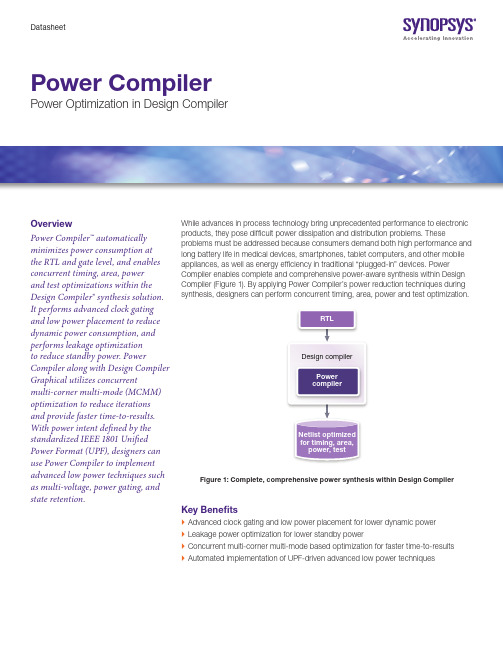

Power Compiler

DatasheetPower CompilerPower Optimization in Design CompilerOverviewPower Compiler™ automaticallyminimizes power consumption atthe RTL and gate level, and enablesconcurrent timing, area, powerand test optimizations within theDesign Compiler® synthesis solution.It performs advanced clock gatingand low power placement to reducedynamic power consumption, andperforms leakage optimizationto reduce standby power. PowerCompiler along with Design CompilerGraphical utilizes concurrentmulti-corner multi-mode (MCMM)optimization to reduce iterationsand provide faster time-to-results.With power intent defined by thestandardized IEEE 1801 UnifiedPower Format (UPF), designers canuse Power Compiler to implementadvanced low power techniques suchas multi-voltage, power gating, andstate retention.While advances in process technology bring unprecedented performance to electronicproducts, they pose difficult power dissipation and distribution problems. Theseproblems must be addressed because consumers demand both high performance andlong battery life in medical devices, smartphones, tablet computers, and other mobileappliances, as well as energy efficiency in traditional “plugged-in” devices. PowerCompiler enables complete and comprehensive power-aware synthesis within DesignCompiler (Figure 1). By applying Power Compiler’s power reduction techniques duringsynthesis, designers can perform concurrent timing, area, power and test optimization.Figure 1: Complete, comprehensive power synthesis within Design CompilerKey Benefits``Advanced clock gating and low power placement for lower dynamic power``Leakage power optimization for lower standby power``Concurrent multi-corner multi-mode based optimization for faster time-to-results``Automated implementation of UPF-driven advanced low power techniquesRTLDesign compilerPowercompilerNetlist optimizedfor timing, area,power, testPower Compiler 2Figure 2: Power Compiler performs automatic clock gating to reducedynamic power consumption.Figure 3: Power-aware placement minimizes capacitance on high activity netsD_IN DEN CLKENCLKD_OUTQStandard non clock-gating ImplementationPower compiler gated-clock ImplementationFFLTalways @ (posedge CLK) if (EN)D_OUT = D_INRegister BankICGAdvanced Clock GatingPower Compiler reduces dynamic power consumption by gating the clocks of synchronous load-enable register banks instead of circulating the outputs back to the inputs when the load-enable conditions are invalid (Figure 2). The operations are performed automatically during the design elaboration phase without requiring any changes to the RTL source, enabling fast and easy trade-off analysis and maintaining technology-independent RTL source. Power Compiler’s clock gating can also be performed at the gate level and can complement manual clock gating. The tool supports several advanced clock gating techniques, including self-gating, multi-stage, latency-driven, activity-driven (using SAIF files) and user-instantiated clock gating.Low Power PlacementIn addition to clock gating, Power Compiler along with Design Compiler Graphical, performs power-aware placement, This capability utilizes the same technology as IC Compiler to minimize net length on signals with high switching activity, in order to minimize dynamic power consumption.Leakage Power OptimizationPower Compiler reduces leakage power using multi-voltage threshold based optimization, or by the designer’s specifying a maximum percentage of low-voltage threshold cells to be used in a design. Power Compiler measures the trade-offs between positive timing slacks, area and power, and delivers the lower power-consuming design that meets the timing constraints.Concurrent Multi-Corner Multi-Mode Based OptimizationConcurrent MCMM optimization isessential for fast turnaround time when implementing designs that can operate in many modes such as test mode, low-power active mode, stand-by mode, etc. One of the primary benefits of MCMM is the ability to achieve optimal leakage results without performing either leakageLow activityHigh activityLow activityHigh activity01/14.AP.CS3874.Synopsys, Inc. • 700 East Middlefield Road • Mountain View, CA 94043 • ©2014 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks is available at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.power optimization on the same corner as timing optimization or successive leakage-timing optimizations (using differentcorners for worst-case timing and worst-case leakage).MCMM optimization in Design Compiler Graphical and Power Compiler takes all of the different process corners into account to provide the best leakage results with minimal impact on performance. The ability to concurrently optimize for multiple modes and corners enables rapid design convergence through fewer design iterations. Used with UPF power intent specification, MCMM serves as the key enabling technology for performing dynamic voltage and frequency scaling (DVFS).Automated Implementationof Advanced Low Power TechniquesEarly definition of power intent in thedesign flow enables downstream tasks in the process to be automated and driven by a consistent power specification. Power intent includes the specification of multiple voltage supplies, power domains, power shutdown modes, isolation, voltage level shifting and state retention behavior. Power intent written in the IEEE 1801 Unified Power Format (UPF) is used systematically throughout the design process to describe thedesign power intent, and is captured as a companion file to the RTL or gate level design. This power intent automates the implementation of the advanced low power capabilities employed.Power Compiler takes UPF input and automatically inserts power management cells such as isolation, level-shifter, retention register, power gating and always-on cells as needed based on the power domain, strategy and state definitions. It also supports a “golden UPF” flow that preserves original power intent across the entire design flow.Netlist Formats and InterfacesPower Compiler is seamlessly integrated with the Synopsys synthesis design flow and shares the same GUI, commands, constraints and libraries as the Design Compiler and IC Compiler ® tools. It supports all popular industry standard formats and platforms.Circuit Netlist:``Verilog, SystemVerilog, VHDL Interfaces: ``SDF, PDEF, SDC Platforms:``IBM AIX (32-/64-bit)``Redhat Linux (32-/64-bit) ``Sun Solaris (32-/64-bit)SummaryPower Compiler delivers complete and comprehensive power synthesis within Design Compiler, including advanced clock gating for dynamic power savings, leakage power optimization for lower standby power and concurrent MCMM of leakage and timing corners. Power Compiler also supports automated implementation of low power methodologies using UPF.For more information on Synopsys’ Advanced Low Power Solution, visit /lowpower.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/inform ation/snug/2009/low-power-impleme ntation-flow-based-ieee1801-upf基于IEEE1801(UPF)标准的低功耗设计实现流程Low-power Implementation Flow BasedIEEE1801 (UPF)郭军, 廖水清, 张剑景华为通信技术有限公司**************************************************************AbstractPower consumption is becoming an increasingly important aspect of ASIC design. There are several different approaches that can be used to reduce power. However, it is important to use these low-power technology more effectively in IC design implementation and verification flow. In our latest low-power chip, we completed full implementation and verification flow from RTL to GDSII successfully and effectively by adopting IEEE1801 Unified Power Format (UPF). This paper will focus on UPF application in design implementation with Synopsys low power solution. It will highlight that how to describe our low-power intent using UPF and how to complete the design flow. This paper first illustrates current low-power methodology and UPF’s concept. Then, it discussed UPF application in detail. Finally, it gives our conclusion.Key words: IEEE1801, UPF, Low-Power, Shut-Down, Power Gating, Isolation, IC-Compiler摘要目前除了时序和面积,功耗已经成为集成电路设计中日益关注的因素。

当前有很多种降低功耗的方法,为了在设计实现流程中更加有效的利用各种低功耗的设计方法,我们在最近一款芯片的设计实现以及验证流程中,使用了基于IEEE1801标准Unified Power Format(UPF)的完整技术,成功的完成了从RTL到GDSII的全部过程,并且芯片制造回来成功的完成了测试。

本文就其中的设计实现部分进行了详细探讨,重点介绍如何用UPF把我们的低功耗意图描述出来以及如何用Synopsys工具实现整个流程,希望给大家以启发。

本文先介绍目前常用的低功耗设计的一些方法特别是用power-gating的方法来控制静态功耗以及UPF的实现方法,然后阐述UPF在我们设计流程中的应用,并在介绍中引入了一些我们的设计经验,最后给出我们的结论。

关键字:IEEE1801, UPF,低功耗, 电源关断,Power-Gating, Isolation, IC-Compiler1. 简介1.1 深亚微米设计面临的挑战随着工艺特征尺寸的缩小以及复杂度的提高,IC设计面临了很多挑战:速度越来越高,面积不断增大,噪声现象更加严重等。

其中,功耗问题尤为突出,工艺进入130nm以下节点后,单位面积上的功耗密度急剧上升,已经达到封装、散热、以及底层设备所能支持的极限。

随着工艺进一步达到90nm以下,漏电流呈指数级增加(如图1所示),在某些65nm设计中,漏电流已经和动态电流一样大,曾经可以忽略的静态功耗成为功耗的主要部分。

功耗已成为继传统二维要素(速度、面积)之后的第三维要素。

图1: 静态功耗与工艺特征尺寸的关系另外,目前飞速发展的手持电子设备市场,为了增强自身产品的竞争力,也对低功耗提出了越来越高的要求;其次散热问题、可靠性问题也要求IC的功耗越小越好;最后全球都在倡导绿色环保科技理念,保护环境,节约能源。

这些都要求IC设计时必须采用低功耗技术,以有效应对这些挑战。

1.2 目前低功耗设计常用的方法如图2所示,影响功耗的因素有电压、漏电流、工作频率、有效电容等。

可以通过降低工作电压、减少翻转负载以及降低电路翻转率等来降低动态功耗;通过减少工作电压以及减少漏图2: 影响功耗的因素电流来降低静态功耗。

当前,业界采用了各种方法来降低芯片的动态功耗和静态功耗。

如图3所示,传统的低功耗技术有时钟关断(Clock-Gating),多域值电压库(Multi-threshold libraries)等;较新的技术有多电压(Multi-Voltage),电源关断(MTCMOS Power Gating),带状态保持功能的电源关断(Power Gating with State Retention),动态电压频率调整(Dynamic Voltage and Frequency Scaling),低电压待机(Low-Vdd Standby)等。

图3: 低功耗技术示例1.3 控制静态漏电的方法1.3.1 电路优化(Gate-level Optimization)在设计实现过程中,自动化的综合和布局布线工具可以根据电路的时序特征,来综合优化每条路径中用到的所有标准单元的时序,面积以及功耗。

根据负载将非关键路径中的标准单元切换到具有较小驱动能力的单元,由于输出电容减小,可以减小动态功耗;同时,由于标准单元MOS管和电容变小,静态漏电流也同时减小。

除了变化驱动能力之外,还可以通过优化电路中的逻辑单元、移动单元物理位置等方法来达到降低功耗的目的。

1.3.2 多域值电压库(Multi-Threshold)如图4所示,高域值电压的标准单元漏电流小但速度慢,低域值电压的标准单元则速度快但漏电流大。

所以采用多域值电压库作为设计实现的目标库,在设计中尽可能多地用高域值电压的标准单元,仅在关键路径上为了满足时序要求采用低域值电压的标准单元,这样就可以最大限度地减小标准单元的漏电流,从而降低静态功耗。

图4: 漏电流、单元速度与阈值电压三者之间的关系1.3.3 电源关断(Power-Gating)芯片中某些模块在不工作时,可以关断其电源,在需要工作时,再将其电源导通,这就是电源关断技术。

它可以使电源关断区域的漏电流降至接近零,极大的减小芯片的静态功耗。

现在电源关断的技术也很多,有片内关断、片外关断。

顾名思义,片外关断就是在芯片外部通过切断电源来关断芯片内部的某些模块。

片内关断又分为精细关断(fine-grain)和粗糙关断(coarse-grain),精细关断需要特别库的支持,可以实现每个标准单元的精细关断;而粗糙关断只需要一些门控单元就可以实现对某些模块的电源或地的控制,如图5所示,用pmos来控制电源,用nmos来控制地。

图5: 电源关断(Power-Gating)的原理图2. UPF的设计实现流程IEEE1801标准Unified Power Format(UPF)是一个真正意义统一的,被广泛采用的低功耗实现标准。

它用一些标准的语句描述用户的低功耗设计意图(Power Intent)。

如图6所示,图6: UPF的应用流程有了这样一个统一的UPF文件,逻辑综合、物理实现、仿真验证、等效性检查以及最后的sign-off流程就可以按照UPF中对低功耗设计意图的描述来完成整个IC设计实现验证流程。

这样贯穿于整个流程的低功耗意图来源于同一个文件,这种一致性可以大大降低低功耗设计的风险性。

并且UPF对低功耗设计提供了开放的,多厂商工具支持的流程和解决方案。

众多支持UPF标准的EDA供应商的产品证明了它是一个互操作性强的标准。

2.1 Synopsys基于UPF的低功耗设计流程Synopsys公司提供了完整的基于UPF的低功耗综合、物理实现和验证流程,如图7所示。

该流程始于寄存器传输级(RTL)描述的逻辑设计,加上一个独立的描述低功耗设计意图的UPF文件。

RTL和UPF描述分别放在独立的文件中,使他们可以单独维护和修改。

在这个示例中,最初的UPF文件标志为UPF。

图7: UPF Flow With Synopsys ToolsDesign Compiler读入RTL和初始UPF描述文件,基于它们综合出门级网表并产生一个更新了的UPF文件,这个Design Compiler输出的UPF文件在示例图中标志为UPF’。

UPF’文件中包含了原始UPF文件的内容,并添加了综合时加入的对某些特殊cell(比如isolation cells、level shifters)的电源和地的连接关系。

综合输出的门级网表已经被工具根据UPF的相应描述插入了一些低功耗所需的特殊电路单元,比如Level-Shifter,Isolation cells,Retention Register等。

IC Compiler读入综合输出的门级网表和UPF’描述文件,基于它们进行物理实现,包括:布局和布线以及电源关断特殊单元(Power-Gating cell)的插入、摆放和控制信号线的连接等步骤。

输出一个新的门级网表,一个包括所有cell的电源和地连接关系的网表(俗称pg网表),以及一个更新了的UPF文件,标志为UPF’’。

UPF’’文件包含了UPF’的内容,并添加了在物理实现阶段对低功耗电路结构的改变,比如添加了Power Switches(俗称MTCMOS)的连接关系。

这个flow中产生的数据可以用于做功能仿真(利用MVSIM、VCS),插入的低功耗单元的正确性检查(利用MVRC),形式验证(利用Formality),以及时序功耗检查(利用Prime Time-PX)和电压降(IR-Drop)(利用Prime Rail)的验证。

VCS仿真器和MVSIM多电压仿真工具可以在几个阶段用来做多电压的功能仿真:RTL级,综合后加入了低功耗相关器件(比如Isolation cell)的门级,以及PR之后加入了Power Switches的门级。