基于FPGA的数字滤波器的设计与实现

基于FPGA的IIR数字滤波器的设计与实现

关 键 词 : 阶 节 ,R 数 字 滤波 器 ,P 二 I I F GA

Ab ta t s rc

Ths ap nr du s eho sig as a i p erito ce a m t d ofu n c c ded s o der oc s ec nd or bl k whch i ba e on PGA o m pl s F t i emen h pr c— tte i i n

张书召 ( 桐柏 鑫 泓银 制 品有限 责任公 司 , 南 西峡 4 4 5 ) 河 7 7 0

彭 杰 ( 广东工业大学 自动化学院, 广东 广州 5 0 9 ) 10 0

摘 要

介 绍一 种 使 用 二 阶 节级 联 方 法在 F GA 上 实现 任 意 阶 数 的 I ( 限 脉 冲 响 应 ) 数 字 滤 波 器 的 原 理 和 方 法 。 首 先 在 P I 无 R

pe a d meh d o n r e u e I ( f i mp le rs o s ) dgtlf e i th i ri a c r a c t e ur— i n to fa y od rn mb rf R i it i us e p n e nn e ii i r r , e ft n c od n e wi rq i a l Fst t l e h e

1 I I R数 字 滤 波器 的 原 理 和 设计

_

al

丫

bl

. a I 2

丫

b 2

数 字滤 波 器 从 实 现 的 网络 结 构 或 者 从 单位 脉 冲响 应 的 长 度

图 1 直 接 n型 结 构

不 同 ,可 以 分 为 无 限 脉 冲响 应 (R)滤 波 器 和 有 限 脉 冲 响 应 I I

基于FPGA的数字滤波器的设计与实现

基于FPGA的数字滤波器的设计与实现数字滤波器是一种非常重要的数字信号处理技术,用于消除输入信号中的噪声,并提高信号品质和可靠性。

FPGA(Field Programmable Gate Array)是一种用于构建数字电路的可编程逻辑器件,因其高度的可定制性、可重构性和高性能而被广泛应用于数字信号处理中。

本文将介绍基于FPGA的数字滤波器的设计和实现,包括滤波器原理、数字滤波器设计方法、FPGA实现技术以及实验结果分析等内容。

一、数字滤波器原理数字滤波器是滤波器的一种,其实现基于数字信号处理技术。

数字滤波器的输入信号是离散时间信号,输出信号也是离散时间信号。

数字滤波器通过在离散时间域上对输入信号进行滤波,实现对输入信号中某些频率成分的滤除或保留。

数字滤波器通常分为FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器两类。

FIR滤波器是一种线性相位滤波器,其系统函数是一个有限长度的冲激响应权重系数序列。

FIR滤波器通过对输入信号的每个样本与权重系数的乘积进行累加,输出得到滤波后的信号。

FIR滤波器具有零相位失真、线性相应特性、易于设计、易于实现等优点。

IIR滤波器是一种具有无限脉冲响应的滤波器,其系统函数是一个有理多项式。

与FIR滤波器相比,IIR滤波器具有更高的滤波效率、更低的计算复杂度和更好的逼近性,但也存在稳定性差、相位失真大等问题。

二、数字滤波器设计方法数字滤波器的设计方法主要包括滤波器性能要求的确定、滤波器类型的选择、滤波器设计的数学模型的建立、滤波器参数的计算、滤波器实现等几个方面。

在确定滤波器性能要求方面,需要考虑滤波器的通频带、阻带、通带和阻带带宽、滤波器响应曲线、阶数等方面的参数。

在滤波器类型的选择方面,需要根据滤波器的性能要求、实现难易度、计算复杂度和开销等方面的因素进行综合考虑。

在滤波器设计的数学模型的建立方面,需要根据选定的滤波器类型建立其对应的数学模型。

在滤波器参数的计算方面,需要根据滤波器的数学模型进行参数的计算和优化。

基于FPGA的IIR数字滤波器设计

摘要数字信号处理在科学和工程技术等许多领域中得到了广泛的应用,其中数字滤波器是现代数字信号处理系统的重要组成部分。

无限长单位冲激响应(IIR)数字滤波器是非常重要的一类滤波器,与有限长单位冲激响应(FIR)数字滤波器相比,IIR能够以较低的阶次获得较高的频率选择特性从而得到了广泛的应用。

本课题采用一种基于现场可编程门阵列(FPGA)的IIR数字滤波器的设计方案。

首先基于IIR数字滤波器的相关理论知识,研究了IIR数字滤波器的常用设计方法,并分析了各种IIR数字滤波器的实现结构等基本理论,由分析结果确定了所要设计的IIR数字滤波器的实现结构。

然后基于FPGA的结构特点,研究了IIR数字滤波器的FPGA设计与实现,并通过Quartus Ⅱ设计平台,采用自顶向下的模块化设计思想,将整个IIR数字滤波器分为:时序控制、延时、补码乘加和累加四个功能模块。

分别对各模块进行VHDL语言描述,并进行了仿真和综合。

仿真结果表明,本设计的IIR数字滤波器运算速度较快,系数改变灵活,有较好的参考价值。

关键词:数字滤波器;无限长单位冲激响应;现场可编程门阵列;VHDL硬件描述语言ABSTRACTDigital signal processing is widely used in lots of fields, such as in science and project technique, Digital filter is one of the important contents of digital signal process. Infiinite impulse response units (IIR) digital filter is a very important type of filters. With its good characteristic of frequency selection in lower order in comparison with finite impulse response (FIR), IIR digital filter is widely applied in modern signal processing systems. This subject is a IIR digital filter design based on the using of field programmable gate array (FPGA). Firstly, based on the analysis of IIR basic realization architectures and the related theoretic analysis, the design methods of IIR sigital filter has been discussed and the structures of a variety of IIR digital filter which can be realized has been analysised. For the results of the theoretical analysis, the final architecture and realization of IIR digital has been decided, Based on the structural characteristics of FPGA, the FPGA design and realization of IIR digital filter has been researched. By used the design plant of Quartus Ⅱ, we adopt blocking method named “Top-down ” and divide the entire IIR digital filter into four blocks, which are Clock control, Time delay, Multiply-addition and Progression. After described with VHDL,we do emulate and synthesis to each block. The result shows that, the introduced IIR digital filter runs fast, and the coefficient changes agility. It has high worth for consulting.Key Words: Digital filter; infinite impulse response units; field programmable gate array; VHDL hardware description language目录1器件简介 (1)2 IIR数字滤波器的相关理论 (4)2.1 IIR滤波器的基本理论 (4)2.1.1 IIR数字滤波器的幅频特性 (5)2.1.2 IIR数字滤波器的相频特性 (7)2.2 IIR数字滤波器的实现结构 (7)2.2.1 直接型结构 (7)2.2.2 级联型结构 (8)2.2.3并联型结构 (10)2.3 数字滤波器的有限字长效应理论 (10)2.3.1 数字表示 (11)2.3.2 输入量化 (12)2.3.3 系数量化 (13)2.3.4 乘积量化 (17)2.3.5 极限环 (19)3 IIR数字滤波器的分析设计 (21)3.1 IIR数字滤波器的模拟转换设计法 (21)3.2 IIR数字滤波器的S-Z变换设计 (21)3.2.1标准Z变换 (22)3.2.2双线性Z变换 (24)3.3 IIR数字滤波器的零极点累试法 (25)3.4 优化设计法 (25)3.5 IIR数字滤波器的硬件实现方案 (25)4 EDA技术和可编程逻辑器件 (30)4.1 电子设计自动化EDA技术 (30)4.2 可编程逻辑器件 (30)4.2.1 FPGA概要 (31)4.2.2 FPGA设计语言 (31)4.2.3 FPGA开发环境 (32)5 IIR数字滤波器的设计与仿真结果分析 (33)5.1 各模块的设计与仿真结果分析 (33)5.1.1 时序控制模块的设计与仿真结果分析 (33)5.1.2 延时模块的设计与仿真结果分析 (34)5.1.3 补码乘加模块的设计与仿真结果分析 (35)5.1.4 累加模块的设计与仿真结果分析 (36)5.1.5 顶层模块设计 (36)5.2 IIR数字滤波器的仿真与结果分析 (37)5.2.1 IIR数字滤波器的系统设计 (37)5.2.2 IIR数字滤波器的系统仿真与结果分析 (38)5.2.3 高阶IIR数字滤波器的实现 (39)6 IIR数字滤波器的硬件实现 (40)6.1 IIR数字滤波器的硬件实现平台 (40)6.1.1 硬件结构 (40)6.1.2器件介绍 (41)6.1.3 JTAG链简介 (43)6.1.4 FPGA的配置 (44)6.2 IIR数字滤波器的VHDL设计 (45)6.2.1 接口定义 (45)6.2.2 综合与仿真 (45)6.3 数字滤波器的实现 (45)结束语 (46)参考文献 (47)致谢 (48)附录1 各模块VHDL程序 (49)1器件简介数字滤波器是具有一定传输选择特性的数字信号处理装置,其输入、输出均为数字信号,实质上是一个由有限精度算法实现的线性时不变离散系统。

基于FPGA的高速FIR数字滤波器设计的开题报告

基于FPGA的高速FIR数字滤波器设计的开题报告一、选题意义数字信号处理是一种关键技术,广泛应用于通信、雷达、音视频处理等领域。

而数字滤波器是数字信号处理的重要组成部分之一,用于移除信号中的噪声、加强特定频率成分等。

FIR数字滤波器是一种广泛应用的数字滤波器,它具有运算速度快、实现简单等特点。

FPGA作为一种可编程逻辑器件,具有可重构性、高速度、低功耗、高可靠性等优点,在数字信号处理领域得到了广泛应用。

本课题旨在利用FPGA高性能特点,设计开发一种基于FPGA的高速FIR数字滤波器,满足在特定应用场景下对信号的快速处理需求,具有重要的理论意义和实际应用价值。

二、主要内容1. 对FIR数字滤波器的算法原理进行分析和设计,包括常见的窗函数设计、有限脉冲响应设计等,选择比较优的算法。

2. FPGA数字滤波器的硬件设计,包括数据的输入输出接口、滤波算法实现和时序控制器设计。

3. FPGA数字滤波器的仿真设计,包括基于MATLAB的算法仿真和基于ModelSim的硬件仿真等。

4. FPGA数字滤波器的实现与验证,包括采用相应工具对FPGA数字滤波器进行编译下载,将实验结果与仿真结果进行比较与分析。

5. 对设计的FPGA数字滤波器进行性能测试,包括运算速度、滤波效果等方面的测试,将其结果与已有的数字滤波器进行对比分析。

三、技术路线1. 确定常见的FIR数字滤波器设计算法,并选择较优的算法设计数字滤波器。

2. 设计FPGA数字滤波器的硬件结构,包括输入输出模块、滤波模块和时序控制模块等;并根据所选算法设计硬件逻辑。

3. 采用MATLAB进行设计算法的理论分析,从理论上验证算法的优越性。

4. 采用ModelSim进行硬件电路仿真,进行设计参数调整和错误修正,保证硬件逻辑的正确性和同步性。

5. 采用Quartus II进行编译下载,将设计的FPGA数字滤波器实现于FPGA芯片中,测试其性能。

四、研究难点1. 在设计算法时,需要充分了解各种滤波器设计算法的优缺点,并选择适合特定场景的算法。

基于FPGA的FIR数字滤波器的设计与实现

基于FPGA的FIR数字滤波器的设计与实现作者:杨国庆来源:《现代电子技术》2008年第19期摘要:介绍了基于FPGA的FIR数字滤波器的设计与实现,该设计利用Matlab工具箱设计窗函数计算FIR滤波器系数,并通过VHDL层次化设计方法,同时FPGA与单片机有机结合,采用C51及VHDL语言模块化的设计思想及进行优化编程,有效实现了键盘可设置参数及LCD显示。

结果表明此实现结构能进一步完善数据的快速处理和有效控制,提高了设计的灵活性、可靠性和功能的可扩展性。

关键词:FPGA;滤波器;VHDL;窗函数;模块化;可扩展性中图分类号:TN713文献标识码:B文章编号:1004373X(2008)1918403Design and Realization of FIR Digital Filter Based on FPGAYANG Guoqing(Tianjin Institute of Urban Construction,Tianjin,300384,China)Abstract:This paper introduces a design and realization of FIR digital filter based on FPGA.The design uses window function of Matlab toolbox to calculate FIR filter coefficient.Through VHDL level of design,FPGA and MCU organic integration,C51 and VHDL used modular design and optimize programming,the effective realization of the keyboard can also set the parameters and LCD display,the results show that this structure can be further improved to achieve the rapid data processing and effective control,the design flexibility,reliability and extendibility function are improved as well.Keywords:FPGA; filter;VHDL;window function;modulization;extendibility1 引言数字滤波是通信、语音与图像处理、模式识别和谱分析等应用中的一种基本的处理部件,它可以满足滤波器对幅度和相位特性的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。

基于FPGA的数字匹配滤波器的设计

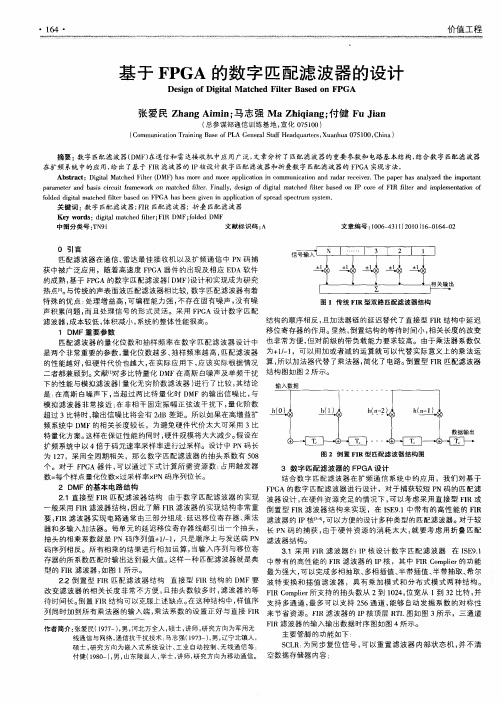

摘 要 : 字 匹配滤 波 器( MF在 通信 和 雷达接 收机 中应用 广 泛, 数 D ) 文章 分析 了 匹配 滤 波器 的重要 参数 和 电路基 本 结构 , 结合 数字 匹配滤 波器

在扩 频 系统 中的应 用 , 出 了基 于 F R滤波 器的 I 核 设计 数 字 匹配滤波 器和折 叠数 字 匹配滤 波器 的 F G 实现 方 法。 给 I P PA

文章 编 号 :0 6 4 I( 00)6 06 — 2 10 — 3 12 1 1— 14 0

O 引言

匹 配 滤 波器 在通 信 、 达 最 佳 接 收机 以 及 扩 频 通 信 中 P 雷 N码 捕 获 中 被 广 泛 应 用 , 随着 高 速度 F G P A器 件 的 出现 及相 应 E A软 件 D 的成 熟 , 于 F G 的数 字 匹配 滤 波 器 ( F) 计和 实 现成 为研 究 基 PA DM 设 热 点 l 与传 统 的声 表 面 波 匹配 滤 波 器 相 比较 , l l 。 数字 匹配 滤 波 器 有着 特 殊 的优 点 : 理 增 益 高 , 编 程 能 力 强 , 存 在 固 有 噪 声 , 有 噪 处 可 不 没 图 1 传 统 FR 型 双 路 匹 配滤 波 器 结 构 I 声 积 累 问 题 , 且 处 理 信 号 的形 式 灵 活 。 采 用 F G 设计 数 字 匹 配 而 PA 结 构 的 顺 序相 反 , 加法 器 链 的 延 迟 替 代 了直接 型 FR结 构 中延 迟 且 I 滤 波 器 , 本 较低 , 积减 小 , 统 的 整体 性 能 很 高 。 成 体 系 移 位 寄 存 器 的作 用 。 然 , 置 结 构 的 等 待 时 间小 , 关长 度 的 改 变 显 倒 相 1 MF重 要 参数 D 但 匹配滤波器 的量化位数和抽样 频率在数 字匹配滤波器设计 中 也 非常 方 便 , 对 前 级 的带 负载 能 力 要 求 较 高 。 由于 乘法 器 系数 仅 1 ,可 以用 加 或 者 减 的 运 算 就 可 以代 替 实 际 意 义上 的乘 法运 一 是 两 个 非 常 重 要 的参 数 , 化 位 数 越 多 、 量 抽样 频 率 越 高 , 配 滤 波器 为+ /1 匹 所 简 倒 I 的性 能 越 好 , 硬 件代 价 也 越 大 , 实 际 应 用 下 , 该 实 际 根 据 情 况 算 , 以加 法 器 代 替 了乘 法器 , 化 了 电路 。 置 型 FR 匹配 滤 波器 但 在 应 二者 都 兼 顾 到 。 献川 多 比特 量 化 D 文 对 MF在 高 斯 白噪声 及 单 频 干扰 结 构 图 如 图 2所 示。 下 的性 能 与 模 拟 滤波 器 ( 化 无 穷 阶 数 滤 波 器 ) 行 了 比较 , 结论 量 进 其 是 : 高 斯 白 噪声 下 , 在 当超 过 两 比特 量 化 时 D MF的输 出信 噪 比 , 与 模 拟 滤 波 器 非 常 接 近 非 相 干 固 定 振 幅 正 弦 波 干扰 下 , 化 阶 数 在 量 超过 3比特时 , 输出信 噪比将会有 2 B差距。所以如果在高增益扩 d 频 系统 中 D MF的 相 关 长 度 较 长 ,为避 免 硬 件 代 价 太 大 可 采 用 3比 特量 化 方 案 。 样 在 保 证性 能 的 同时 , 件 规 模将 大 大减 少 。 设 在 这 硬 假 扩频 系统 中以 4信于码元速率采样率进行过采样。设计 中 P N码长 为 17 2 ,采用全周期相关 ,那么数字匹配滤波器的抽头系数有 5 8 0 个。对于 F G P A器 件 , 可以通过下式计算所需资 源数 : 占用触 发器 数: 每个 样 点 量 化 位 数× 采 样 率 x N码 序 列 位 长 。 过 P

基于 FPGA 的数字滤波器设计与实现

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

基于fpga的数字相敏检波算法实现

基于fpga的数字相敏检波算法实现fpga(Field Programmable Gate Array)是一种非易失可配置逻辑器件,成为当今技术发展的关键产品之一。

近年来,由于其高速处理能力、低功耗、低成本等特点,fpga在数字信号处理领域得到了越来越多的应用。

一种常见的应用就是基于fpga的数字相敏检波算法实现。

在基于fpga的数字相敏检波算法中,首先要实现的是数字滤波器的设计。

这里的滤波器必须能够满足信号处理的时序要求,保证信号有较低的噪声水平。

基于此,一般采用离散傅立叶变换(DFT)进行信号滤波,使用折线拟合技术对滤波系数进行优化,从而获得高质量的滤波结果。

接下来,应该实现的是数字相敏检波的算法。

首先,通过数字滤波器进行数据采样,并将数据转换为频域数据。

然后,为了解决检波问题,把信号进行振幅处理,使噪声的振幅大小小于某一特定阈值,以判断其检波结果。

最后,以系统仿真结果为准,基于fpga实现数字相敏检波算法。

数字相敏检波算法是fpga应用中常用的一种有效方法,它可以将信号进行调制和解调,从而控制信号的振幅。

此外,基于fpga的数字相敏检波算法具有较强的容错性和可靠性,可以提供调制解调以及精确测量等功能,在许多领域得到了广泛的应用。

综上所述,基于fpga的数字相敏检波算法是一种有效的信号处理技术,由于其低功耗、低成本特点,被广泛应用于许多领域。

它可以利用数字滤波器进行数据采样和频域数据转换;利用折线拟合技术优化系统性能;利用振幅处理和判断阈值实现信号检波;利用fpga实现算法,最终达到调制解调以及精确测量等功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

分积 p1( n) 和 p2( n) 可分别先垂直相加后再水平相加, 最后的结果是一致的, 得 1010。后一种对部分积先进 行水平相加的方法就是查找表法。由于 FIR 滤波器的 h( n) 均为常数, x( n) 的最低位为 1001, 则 p1( n) 的值为 h( 0) +h( 3) , 其高位为 1010, 则 p2( n) 的值为 h( 1) +h( 3) 。 因此可利用 FLEX10K系列的查找表结构, 先将 h( n) 的 各种组合存入查找表, 这样卷积运算可用加法来代替。 将 p2( n) 左移一位与 p1( n) 相加即可。对于笔者所要实 现的 16 阶线性相位 FIR 滤波器来说, 需要 2 个查找表 来实现, 这是由 FLEX10K 系列器件的四输入查找表结 构来决定的。

LU Yu- peng, QIU Hong- an, TIAN Duo- hua, SHAO Li- qun

( College of Marine, Northwest Polytechnical University, Xi′an 710072, China)

【Abstr act】The design scheme of FIR linearity phasic digital filter based on FPGA is introduced. The FPGA four

笔者设计的低通滤波器截止频率为 100 Hz, 采用 窗函数设计法得到 h( n) , 利用 MATLAB 强大的计算功

能 先 求 得 理 想 脉 冲 响 应 hd( n) , 然 后 在 MATLAB 中 调 用窗函数 w( n) , 从而计算出 h( n) 的具体数值。

4 FIR 滤波器的 VHDL 描述及仿真

0110

h( 1) +h( 2)

h( 5) +h( 6)

0111 1000 1001

h( 0) +h( 1) +h( 2) h( 3)

h( 0) +h( 3)

h( 4) +h( 5) +h( 6) h( 7)

h( 4) +h( 7)

1010 1011 1100

h( 1) +h( 3) h( 2) +h( 3) h( 0) +h( 1) +h( 3)

电声器件与电路

T E le c t r o a c o u s t ic P a r t s a n d Cir c u i

文章编号: 1002- 8684( 2008) 05- 0023- 03

基于 FPGA 的数字滤波器的设计与实现 ·实用设计·

陆宇鹏, 邱宏安, 田多华, 邵立群 ( 西北工业大学 航海学院, 陕西 西安 710072)

该文设计的 16 阶 FIR 滤波器 由 上 述 模 块 逻 辑 组 成, 其原理如图 2 所示。设计系统工作过程为: 由于累 加器频率和采样频率不同, 故用一个计数器作为分频 器。每 8 个“clk”时钟产生 1 个有效的时钟周期。即每 一 个 clk 时 钟 使 “cout10”加 1, “cout10”由 “0000”到 “1000”, 从而输出 1 个时钟周期。此时, 一组 8 bit 二进 制数并行输入, 在第 1 个有效时钟周期的上跳沿, 8 bit 二 进 制 数 的 最 低 位 xin18 经 时 延 器 Y7[3…0]输 出 , 由 “sel8”的 输 出 “sel8[3… 0]”决 定 存 储 器 中 对 应 的 事 先 算 好存入的数值, 此数值经“nomout[13…0]”输出, 并进入 累加器中; 在第 2 个有效时钟周期的上跳沿, 8 bit 二进 制 数 的 第 2 位 xin17 经 时 延 器 Y6[3… 0]输 出 , 同 样 由 “sel8”的 输 出 “sel8[3…0]”决 定 的 乘 积 值 , 送 入 累 加 器 中……直到第 8 个有效时钟 周期的上跳沿后, 8 bit 二

2 系数的量化

Matlab 模拟得到的脉冲成形滤波器的系数都是浮 点数, 转换成定点系数需要进行量化。理论上使量化误 差最小的定点系数在数轴上是均匀分布的, 而 CSD 编 码的系数在数轴上是非均匀分布的。存在空隙, 即使无 限增加字长也不能减小这个空隙, 要减小这个空隙只 有增加非零位个数。而非零位个数 L 非常重要, 直接关 系到硬件规模, L 每加 1, 每个抽头就需要增加一个加

( 2) 存储器模块通过编程实现, 利用 VHDL 硬 件 描述语言将事先算好的各模块系数存于逻辑单元中, 以供选择器选择输出送到累加器中进行加法运算。

( 3) 累加器模块采用文本编辑实现, 利用计数器 的输出状态控制选择加数, 与前一次和的输出反馈值 相加, 共加 8 次, 第 9 个时钟周期送出结果并使输出保 持不变, 第 10 个时钟周期累加器清零。这一模块集中 了前四阶的 8 位信号的全部系数, 每采样一次就会有 8 个数据( 每位信号一个数据) 在时钟控制下输出到累 加器中进行累加。

于查找表的 FIR 滤波器具有速度快、占用资源少的特点。采用流水线技术对加法运算进行处理, 速度进一步提高。

【关键词】FPGA; FIR 滤波器; VHDL; 四输入查找表

【中 图 分 类 号 】 T N713

【文 献 标 识 码 】 A

Design of FIR Filter Based on FPGA

h( 5) +h( 7) h( 4) +h( 5) +h( 7)

h( 6) +h( 7)

1101

h( 0) +h( 2) +h( 3)

h( 4) +h( 6) +h( 7)

1110 1111

h( 1) +h( 2) +h( 3) h( 0) +h( 1) +h( 2) +h( 3)

h( 5) +h( 6) +h( 7) h( 4) +h( 5) +h( 6) +h( 7)

import LUT configuration is used to make up of vector multiplication, and the VHDL source program and

simulating results are given. The design error cause and improving measure are discussed. Compared with common

被乘数 h( n)

01 11 10 11

乘数 s( n)

× 11 00 10 01

部分乘积 p1( n)

01 00 00 11 = 100

部分乘积 p2( n)

+ 01 00 10 00 = 011

011 000 100 011 = 1010 图 1 无符号并行矢量乘法器的实现

其中, h( n) 为 FIR 滤波器的冲击响应, s( n) 为 FIR 滤波器对称的输入项之和。对应乘数低位和高位的部

【Key wor ds】FPGA; FIR filter; VHDL; LUT

1 指标的确定和滤波器系数的提取

根据工程实际需要, 选定 FIR 的性能指标如下: 采 样频率 fs=1 000 Hz; 截止频率 fc=100 Hz; 类型: 低通; 阶 数: 16 阶; 8 bit 输入和输出数据宽度。

FIR 滤 波 器 的 系 数 可 用 窗 函 数 的 方 法 来 获 得 , 窗 函数法的基本思想是使其具有最窄主瓣宽度和尽可能 小的旁瓣[1]。笔者选择利用矩形窗进行设计, 因为在编 制 LUT 表的过程中运算量较小。若不选择矩形窗而选 择其他窗函数进行设计也是可行的, 因为 ROM 的容量 很大, 在编制查找表时, 常常只用到它的一小部分空 间, 只是在编制查找表时计算量会变得很大。

该文的 16 阶线性相位的查找表如表 1 所示。

表 1 16 阶线性相位的查找表

s( n) 0000 0001 0010

LUT1 0

h( 0) h( 1)

LUT2 0

h( 4) h( 5)

0011

h( 0) +h( 1)

h( 4) +h( 5)

0100 0101

h( 2) h( 0) +h( 2)

h( 6) h( 4) +h( 6)

【摘 要 】 提 出 了 一 种 基 于 FPGA 的 FIR 线 性 相 位 滤 波 器 设 计 方 案 , 充 分 利 用 FPGA 四 输 入 查 找 表 LUT 结 构 构 成

向量乘法器, 给出了对应的 VHDL 源 程序 及 仿 真结 果 , 并 讨论 了 设 计误 差 原 因及 改 进 措施 。与 普 通滤 波 器 相比 , 基

法运算。 h( n) 是通过窗函数求得的, 在实际编写查找表时,

由于数据全部采用二进制的补码形式, 因此若不改变 表中 h( n) 的形式直接编制, 则得到的结果会因为个别 数据产生溢出而发生错误, 如当有 2 个同符号数相加 时就可能产生溢出, 溢出现象是由于得到运算结果超 出了 8 bit 补码所能表示的数据范围。

filter, the filter based LUT has the advantages of quick speed and less resource. The production line technology is

employed to carry out treatment on addition arithmetic, and to improve speed.

( 4) 控制器模块的作用是产生控制信号对延迟、 数据存储以及累加器模块进行控制, 以使它们按一 定 的 形 式 组 合 在 一 起 实 现 滤 波 器 的 功 能 。控 制 器 模 块 在 接 收 到 A/D 转 换 结 束 信 号 后 , 依 此 产 生 延 迟 控 制 信 号 、存 储 控 制 信 号 、累 加 控 制 信 号 和 滤 波 结 果 输 出 信号等各种控制信号, 使上述模块按照一定的时序 进行操作。

进制数与 h( 0) , h( 1) , h( 2) , h( 3) 的 各 种 可 能 乘 积, 而 第 2 个存储器中存储的是 h( 4) , h( 5) , h( 6) , h( 7) 分别 与每个 8 bit 二进制数所有可能的乘积。将 2 个存储器 的输出进行移位相加, 其输出即为最后数值。