基于FPGA的数字滤波器的设计与实现总结

基于FPGA的FIR数字滤波器设计

1、F PGA技术简介现场可编程门阵列FPGA是80年代末开始使用的大规模可编程数字IC器件,它充分利用EDA技术进行器件的开发与应用。

用户借助于计算机不仅能自行设计自己的专用集成电路芯片,还可在计算机上进行功能仿真和时序仿真,及时发现问题,调整电路,改进设计方案。

这样,设计者不必动手搭接电路、调试验证,只需短时间内在计算机上操作即可设计出与实际系统相差无几的理想电路。

而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此成为科研产品开发及其小型化的首选器件,其应用极为广泛。

3.1 FPGA工作原理FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。

FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

3.2 FIR滤波器特点1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

基于FPGA的FIR数字滤波器设计与实现

基于FPGA的FIR数字滤波器设计与实现佚名【期刊名称】《现代电子技术》【年(卷),期】2013(000)014【摘要】简要介绍了FIR数字滤波器的结构特点和基本原理,提出基于FPGA和DSP Builder的FIR数字滤波器的基本设计流程和实现方案。

在Matlab/Simulink 环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。

通过SignalCompiler把模型转换成VHDL语言加入到FPGA的硬件设计中,从QuartusⅡ软件中的虚拟逻辑分析工具SignalTapⅡ中得到数字滤波器实时的结果波形图,结果符合预期。

%The structure feature and the basic principle of FIR digital filter is introduced briefly. The basic design process and implementation scheme of the FIR digital filter based on FPGA and DSP Builder is proposed in this paper. FIR model is structured with DSP Builder module in the Matlab/Simulink environment. The FIR digital filter is designed according to the FDA⁃Tool. The system level simulation and ModelSim function simulation were completed. The simulation results show that the filter has excellent effect. The model is converted to VHDL language through SingalCompiler and added to FPGA hardware design. The real⁃time waveform graph of the FIR digital filter was received by the virtual logic analysis tool SignalTapⅡ in QuartusⅡ. The results conform to the expected requirement.【总页数】4页(P123-126)【正文语种】中文【中图分类】TN911-34【相关文献】1.基于FPGA的FIR数字滤波器的设计与实现 [J], 蒋小燕;孙晓薇;胡恒阳;钱显毅2.基于FPGA的FIR数字滤波器的设计与实现 [J], 熊洁;黄蕾3.基于FPGA的FIR数字滤波器的设计与实现 [J], 杨国庆4.基于FPGA的FIR数字滤波器的设计与实现 [J], 陈昭明5.基于FPGA的抗混叠FIR数字滤波器的设计与实现 [J], 金燕; 王明; 葛远香因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的音频信号数字滤波器设计与实现

基于FPGA的音频信号数字滤波器设计与实现音频信号数字滤波器是一种常见的数字信号处理技术,它可以对音频信号进行滤波处理,提取出用户感兴趣的频率成分,去除不需要的噪声等。

近年来,随着现代科技的发展,基于现场可编程门阵列(FPGA)的音频信号数字滤波器的设计与实现越来越受到人们的关注。

本文将介绍基于FPGA的音频信号数字滤波器的设计原理和实现方法。

FPGA是一种可编程逻辑器件,具有高度的灵活性和可编程性,可以根据用户的需求进行定制化的设计。

在音频信号处理中,FPGA可以被用来实现数字滤波器,通过对音频信号进行采样和滤波处理,改善音频信号的质量。

1. 设计原理基于FPGA的音频信号数字滤波器的设计原理主要包括以下几个方面:1.1 数字滤波器的选择在设计过程中,首先需要选择适合音频信号处理的数字滤波器。

常见的数字滤波器包括有限脉冲响应(FIR)滤波器和无限脉冲响应(IIR)滤波器。

FIR滤波器具有线性相位和稳定性等优点,常用于音频信号处理中。

1.2 滤波器的特性和参数根据音频信号处理的要求,可以确定滤波器的通带、阻带、截止频率等参数。

通过对滤波器的特性进行设置,可以实现对音频信号的不同频段进行滤波处理。

1.3 整体系统设计在确定滤波器的参数后,需要进行整体系统的设计。

这包括对FPGA的硬件资源进行评估,选择适合的FPGA器件以及其他所需外设的选择。

同时,还需要设计滤波器的时钟、采样率等系统参数,并进行时序分析和综合等步骤。

2. 实现方法基于FPGA的音频信号数字滤波器的实现方法主要涉及以下几个方面:2.1 开发环境的选择在进行设计之前,需要选择适合的开发环境。

常见的FPGA开发工具包括Xilinx的Vivado和Altera的Quartus II等。

这些工具提供了实现FPGA的硬件描述语言(如Verilog或VHDL)以及综合、布局布线等功能。

2.2 硬件描述语言的编写根据滤波器的设计原理和参数,可以使用硬件描述语言编写滤波器的逻辑电路。

基于FPGA的高速FIR数字滤波器的设计

基于FPGA的高速FIR数字滤波器的设计目前FIR的实现办法主要有3种:利用单片通用数字滤波器、器件和可编程规律器件实现。

单片通用数字滤波器用法便利,但因为字长和阶数的规格较少,不能彻低满足实际需要。

用法DSP器件实现虽然容易,但因为程序挨次执行,执行速度必定不快。

有着规整的内部规律阵列和丰盛的连线资源,特殊适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。

但长久以来,FPGA向来被用于系统规律或时序控制上,很少有信号处理方面的应用,其缘由主要是由于在FPGA中缺乏实现乘法运算的有效结构。

本文利用FPGA乘累加的迅速算法,可以设计出高速的FIR数字滤波器,使FPGA在数字信号处理方面有了长足的进展。

2 Matlab设计滤波器参数

利用Matlab为设计FIR滤波器提供的工具箱,挑选滤波器类型为低通FIR,设计办法为窗口法,阶数为16,窗口类型为Hamming,Beta为0.5,Fs为8.6 kHz,FC为3.4 kHz,导出的滤波器系数如下:

3 迅速FIR滤波器算法的基本原理

(1) 分布式算法

分布式算法在完成乘加功能时是通过将各输入数据每一对应位产生的部分积预先相加形成相应的部分积,然后再对各部分积举行累加得到终于结果。

对于一个N(N为偶数)阶线性相位FIR数字滤波器,输出可由式(1)表示:

(2) 乘法器设计

高性能乘法器是实现高性能的FIR运算的关键,分析乘法器的运算过

第1页共6页。

基于FPGA的IIR数字滤波器的设计与实现

关 键 词 : 阶 节 ,R 数 字 滤波 器 ,P 二 I I F GA

Ab ta t s rc

Ths ap nr du s eho sig as a i p erito ce a m t d ofu n c c ded s o der oc s ec nd or bl k whch i ba e on PGA o m pl s F t i emen h pr c— tte i i n

张书召 ( 桐柏 鑫 泓银 制 品有限 责任公 司 , 南 西峡 4 4 5 ) 河 7 7 0

彭 杰 ( 广东工业大学 自动化学院, 广东 广州 5 0 9 ) 10 0

摘 要

介 绍一 种 使 用 二 阶 节级 联 方 法在 F GA 上 实现 任 意 阶 数 的 I ( 限 脉 冲 响 应 ) 数 字 滤 波 器 的 原 理 和 方 法 。 首 先 在 P I 无 R

pe a d meh d o n r e u e I ( f i mp le rs o s ) dgtlf e i th i ri a c r a c t e ur— i n to fa y od rn mb rf R i it i us e p n e nn e ii i r r , e ft n c od n e wi rq i a l Fst t l e h e

1 I I R数 字 滤 波器 的 原 理 和 设计

_

al

丫

bl

. a I 2

丫

b 2

数 字滤 波 器 从 实 现 的 网络 结 构 或 者 从 单位 脉 冲响 应 的 长 度

图 1 直 接 n型 结 构

不 同 ,可 以 分 为 无 限 脉 冲响 应 (R)滤 波 器 和 有 限 脉 冲 响 应 I I

基于FPGA的带通数字滤波器设计与实现

毕业设计说明书基于FPGA的带通数字滤波器设计与实现学生姓名专业名称电子信息工程指导教师电子与信息工程系基于FPGA的带通数字滤波器设计与实现FPGA-Based Band-Pass Digital Filter Design andImplementation摘要随着高速DSP技术的广泛应用,实时而又快速可靠地进行数字信号的处理越来越成为用户追求的目标。

本文分析了国内外数字滤波技术的应用现状与发展趋势,介绍了数字滤波器的基本结构,介绍了数字滤波器的理论及常见的实现方法。

FPGA是常用的可编程逻辑器件,它所具有的查找表结构非常的适用于实现实时而又快速可靠的数字滤波器上,加上Verilog语言灵活的描述方式以及与硬件无关的这种特点,使得使基于Verilog语言的FPGA芯片实现数字滤波器成为研究的方向。

本文正是围绕着硬件描述语言在数字硬件系统设计中的应用展开来的。

首先从比较传统的数字硬件系统的设计方法与采用硬件描述语言的数字硬件系统设计方法的特点出发,介绍了EDA技术发展的过程以及VHDL语言的特点。

介绍了分布式算法,基于ALTERA 公司四输入查找表结构的FPGA器件的带通数字滤波器设计技术和结合先进的Quartus II 软件、Matlab软件进行高效设计的方法和途径,给出了设计仿真结果。

该设计能够满足要求,设计效率高,对于FPGA硬件资源高效合理的利用。

关键词:FPGA;Verilog;查找表;分布式算法ABSTRACTWith the extensive application of high-speed DSP technology, the users pursuit the target that it is real time high-speed and reliable to process digital signal. This paper analyzes the situation of application and development of digital filter technology home and abroad, introduced the basic structure of the digital filter, introduce the theory of digital filter and common method of its implementation. FPGA is ones of usual PLD, and its architecture of LUT is be applicable to implement real-time, high-speed and reliable digital filter, in addition, Verilog HDL can be quickly learned and mastered , and has nothing to do with hardware, which make it to be a research problem that using Verilog achieves digital filters based on FPGA.This paper is arranged around the apply of Verilog in digital system design. We analyze the way of digital system design traditional and using Verilog ,and introduced the development of EDA, the characteristic of Verilog. Introduced the distributed algorithm, the design technology of the band-pass digital filter in digital algorithm design and implementation is described based on4-input look-up table in FPGA' s, the way and method of high-speed design using excellent Quartus II software,Matlab software. The design can meet the quest and be high-speed, proper in using FPGA’ hardware.Keywords: FPGA; Verilog; LUT(Look-Up-Table); Distributed Algorithm目录第1章绪论 (1)1.1 数字滤波器研究的背景与意义 (1)1.2 数字滤波器的研究基础 (1)1.2.1 电子设计EDA自动化技术 (1)1.2.2可编程逻辑器件 (2)1.2.3硬件描述语言Verilog及数字系统设计方法 (3)1.3 数字滤波器实现方法的现状分析 (4)1.4 本文的研究内容 (5)第2章数字滤波器原理及设计方法 (7)2.1 数字滤波器的基本原理................................ 错误!未定义书签。

基于FPGA的数字滤波器设计与实现

基于FPGA的数字滤波器设计与实现数字滤波器是一种非常重要的信号处理器件,用于从信号中分离出特定频率下的成分。

它可以应用于音频、无线通讯、图像处理等领域,并且随着数字信号处理技术的发展,数字滤波器的性能和功能也日益提高。

本文将介绍基于FPGA的数字滤波器的设计与实现,以及其在实际应用中的一些注意事项。

一、数字滤波器的工作原理数字滤波器是通过模拟信号转换成数字信号后,在数字域中进行信号处理的器件。

其工作原理与模拟滤波器类似,其主要作用是从信号的频谱中分离出所需要的成分。

数字滤波器通常由数字滤波器器件和数字信号处理器构成。

数字滤波器可以分为时域滤波器和频域滤波器。

时域滤波器是根据信号的时间域特性进行滤波,滤波算法通常采用卷积或差分运算。

频域滤波器是将信号变换到频域后通过频率响应特性进行滤波,其通常采用离散傅里叶变换(DFT)或快速傅里叶变换(FFT)等算法。

二、FPGA实现数字滤波器的方式FPGA是一种基于可编程逻辑单元的可重构芯片,具有灵活性、高速性和可重构性等特点,非常适合用于数字信号处理的应用。

FPGA实现数字滤波器的方式主要有两种:直接实现数字滤波器和通过CPU控制实现数字滤波器。

直接实现数字滤波器是指将数字滤波器的算法逻辑直接实现在FPGA芯片内部,其优点是响应速度快、功耗低、实现简单。

缺点是难以对算法进行改进和优化。

而通过CPU控制实现数字滤波器则是将数字滤波器的算法逻辑实现在CPU中,通过FPGA模块将需要滤波的信号通过DMA方式传输给CPU进行处理。

该方式的优点是灵活性高、可扩展性强,缺点是响应速度慢。

三、数字滤波器设计的基本步骤数字滤波器的设计需要进行三个主要的步骤:滤波器的规格化、系统函数的设计和离散化。

滤波器的规格化是指根据滤波需求,对滤波器进行不同的设计。

主要包括滤波器类型的选择、通带、阻带和过渡带的确定等。

系统函数的设计是指根据滤波器的规格化要求,设计出数字滤波器的系统函数。

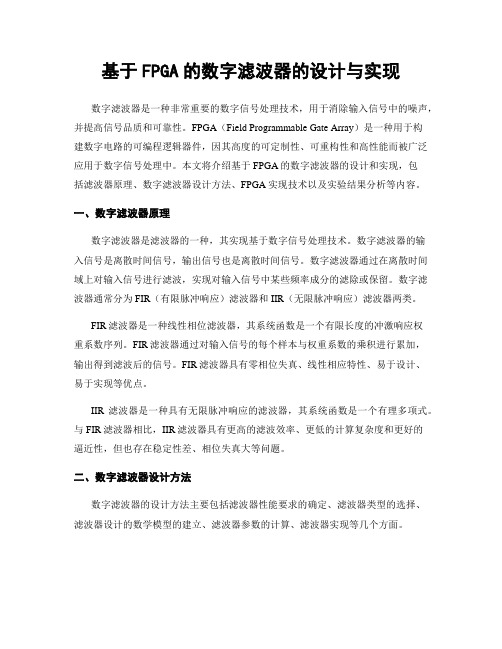

基于FPGA的数字滤波器的设计与实现

基于FPGA的数字滤波器的设计与实现数字滤波器是一种非常重要的数字信号处理技术,用于消除输入信号中的噪声,并提高信号品质和可靠性。

FPGA(Field Programmable Gate Array)是一种用于构建数字电路的可编程逻辑器件,因其高度的可定制性、可重构性和高性能而被广泛应用于数字信号处理中。

本文将介绍基于FPGA的数字滤波器的设计和实现,包括滤波器原理、数字滤波器设计方法、FPGA实现技术以及实验结果分析等内容。

一、数字滤波器原理数字滤波器是滤波器的一种,其实现基于数字信号处理技术。

数字滤波器的输入信号是离散时间信号,输出信号也是离散时间信号。

数字滤波器通过在离散时间域上对输入信号进行滤波,实现对输入信号中某些频率成分的滤除或保留。

数字滤波器通常分为FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器两类。

FIR滤波器是一种线性相位滤波器,其系统函数是一个有限长度的冲激响应权重系数序列。

FIR滤波器通过对输入信号的每个样本与权重系数的乘积进行累加,输出得到滤波后的信号。

FIR滤波器具有零相位失真、线性相应特性、易于设计、易于实现等优点。

IIR滤波器是一种具有无限脉冲响应的滤波器,其系统函数是一个有理多项式。

与FIR滤波器相比,IIR滤波器具有更高的滤波效率、更低的计算复杂度和更好的逼近性,但也存在稳定性差、相位失真大等问题。

二、数字滤波器设计方法数字滤波器的设计方法主要包括滤波器性能要求的确定、滤波器类型的选择、滤波器设计的数学模型的建立、滤波器参数的计算、滤波器实现等几个方面。

在确定滤波器性能要求方面,需要考虑滤波器的通频带、阻带、通带和阻带带宽、滤波器响应曲线、阶数等方面的参数。

在滤波器类型的选择方面,需要根据滤波器的性能要求、实现难易度、计算复杂度和开销等方面的因素进行综合考虑。

在滤波器设计的数学模型的建立方面,需要根据选定的滤波器类型建立其对应的数学模型。

在滤波器参数的计算方面,需要根据滤波器的数学模型进行参数的计算和优化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

filter, the filter based LUT has the advantages of quick speed and less resource. The production line technology is

employed to carry out treatment on addition arithmetic, and to improve speed.

! " # 电声技术 2008年 第 32 卷 第 5 期

电声器件与电路

Ele c t r o a c o u s t ic P a r t s a n d Cir c u it

h( 0) =01, h( 1) =11, h( 2) =10, h( 3) =11,

s( 0) =11, s( 1) =00, s( 2) =10, s( 3) =01

笔者可采用 VHDL 语言进行 FIR 滤波器的描述和 设计, 并结合原理图的设计方法进行设计[3]。该文的基 本思想是底层设计采用 VHDL 语言来描述, 顶层设计 采用原理图的方式[4]。

( 1) 时延环节模块使 A/D 转换后的数据通过不同 的触发器, 从而产生不同的延迟。选择器实质就是计数 器, 输出作为选择变量, 用以选择加数送到累加器。

该文的 16 阶线性相位的查找表如表 1 所示。

表 1 16 阶线性相位的查找表

s( n) 0000 0001 0010

LUT1 0

h( 0) h( 1)

LUT2 0

h( 4) h( 5)

0011

h( 0) +h( 1)

h( 4) +h( 5)

0100 0101

h( 2) h( 0) +h( 2)

h( 6) h( 4) +h( 6)

该文设计的 16 阶 FIR 滤波器 由 上 述 模 块 逻 辑 组 成, 其原理如图 2 所示。设计系统工作过程为: 由于累 加器频率和采样频率不同, 故用一个计数器作为分频 器。每 8 个“clk”时钟产生 1 个有效的时钟周期。即每 一 个 clk 时 钟 使 “cout10”加 1, “cout10”由 “0000”到 “1000”, 从而输出 1 个时钟周期。此时, 一组 8 bit 二进 制数并行输入, 在第 1 个有效时钟周期的上跳沿, 8 bit 二 进 制 数 的 最 低 位 xin18 经 时 延 器 Y7[3…0]输 出 , 由 “sel8”的 输 出 “sel8[3… 0]”决 定 存 储 器 中 对 应 的 事 先 算 好存入的数值, 此数值经“nomout[13…0]”输出, 并进入 累加器中; 在第 2 个有效时钟周期的上跳沿, 8 bit 二进 制 数 的 第 2 位 xin17 经 时 延 器 Y6[3… 0]输 出 , 同 样 由 “sel8”的 输 出 “sel8[3…0]”决 定 的 乘 积 值 , 送 入 累 加 器 中……直到第 8 个有效时钟 周期的上跳沿后, 8 bit 二

h( 5) +h( 7) h( 4) +h( 5) +h( 7)

h( 6) +h( 7)

1101

h( 0) +h( 2) +h( 3)

h( 4) +h( 6) +h( 7)

1110 1111

h( 1) +h( 2) +h( 3) h( 0) +h( 1) +h( 2) +h( 3)

h( 5) +h( 6) +h( 7) h( 4) +h( 5) +h( 6) +h( 7)

FIR 滤 波 器 的 系 数 可 用 窗 函 数 的 方 法 来 获 得 , 窗 函数法的基本思想是使其具有最窄主瓣宽度和尽可能 小的旁瓣[1]。笔者选择利用矩形窗进行设计, 因为在编 制 LUT 表的过程中运算量较小。若不选择矩形窗而选 择其他窗函数进行设计也是可行的, 因为 ROM 的容量 很大, 在编制查找表时, 常常只用到它的一小部分空 间, 只是在编制查找表时计算量会变得很大。

【Key wor ds】FPGA; FIR filter; VHDL; LUT

1 指标的确定和滤波器系数的提取

根据工程实际需要, 选定 FIR 的性能指标如下: 采 样频率 fs=1 000 Hz; 截止频率 fc=100 Hz; 类型: 低通; 阶 数: 16 阶; 8 bit 输入和输出数据宽度。

电声器件与电路

T E le c t r o a c o u s t ic P a r t s a n1002- 8684( 2008) 05- 0023- 03

基于 FPGA 的数字滤波器的设计与实现 ·实用设计·

陆宇鹏, 邱宏安, 田多华, 邵立群 ( 西北工业大学 航海学院, 陕西 西安 710072)

( 2) 存储器模块通过编程实现, 利用 VHDL 硬 件 描述语言将事先算好的各模块系数存于逻辑单元中, 以供选择器选择输出送到累加器中进行加法运算。

( 3) 累加器模块采用文本编辑实现, 利用计数器 的输出状态控制选择加数, 与前一次和的输出反馈值 相加, 共加 8 次, 第 9 个时钟周期送出结果并使输出保 持不变, 第 10 个时钟周期累加器清零。这一模块集中 了前四阶的 8 位信号的全部系数, 每采样一次就会有 8 个数据( 每位信号一个数据) 在时钟控制下输出到累 加器中进行累加。

( 4) 控制器模块的作用是产生控制信号对延迟、 数据存储以及累加器模块进行控制, 以使它们按一 定 的 形 式 组 合 在 一 起 实 现 滤 波 器 的 功 能 。控 制 器 模 块 在 接 收 到 A/D 转 换 结 束 信 号 后 , 依 此 产 生 延 迟 控 制 信 号 、存 储 控 制 信 号 、累 加 控 制 信 号 和 滤 波 结 果 输 出 信号等各种控制信号, 使上述模块按照一定的时序 进行操作。

笔者设计的低通滤波器截止频率为 100 Hz, 采用 窗函数设计法得到 h( n) , 利用 MATLAB 强大的计算功

能 先 求 得 理 想 脉 冲 响 应 hd( n) , 然 后 在 MATLAB 中 调 用窗函数 w( n) , 从而计算出 h( n) 的具体数值。

4 FIR 滤波器的 VHDL 描述及仿真

import LUT configuration is used to make up of vector multiplication, and the VHDL source program and

simulating results are given. The design error cause and improving measure are discussed. Compared with common

于查找表的 FIR 滤波器具有速度快、占用资源少的特点。采用流水线技术对加法运算进行处理, 速度进一步提高。

【关键词】FPGA; FIR 滤波器; VHDL; 四输入查找表

【中 图 分 类 号 】 T N713

【文 献 标 识 码 】 A

Design of FIR Filter Based on FPGA

被乘数 h( n)

01 11 10 11

乘数 s( n)

× 11 00 10 01

部分乘积 p1( n)

01 00 00 11 = 100

部分乘积 p2( n)

+ 01 00 10 00 = 011

011 000 100 011 = 1010 图 1 无符号并行矢量乘法器的实现

其中, h( n) 为 FIR 滤波器的冲击响应, s( n) 为 FIR 滤波器对称的输入项之和。对应乘数低位和高位的部

进制数与 h( 0) , h( 1) , h( 2) , h( 3) 的 各 种 可 能 乘 积, 而 第 2 个存储器中存储的是 h( 4) , h( 5) , h( 6) , h( 7) 分别 与每个 8 bit 二进制数所有可能的乘积。将 2 个存储器 的输出进行移位相加, 其输出即为最后数值。

0110

h( 1) +h( 2)

h( 5) +h( 6)

0111 1000 1001

h( 0) +h( 1) +h( 2) h( 3)

h( 0) +h( 3)

h( 4) +h( 5) +h( 6) h( 7)

h( 4) +h( 7)

1010 1011 1100

h( 1) +h( 3) h( 2) +h( 3) h( 0) +h( 1) +h( 3)

分积 p1( n) 和 p2( n) 可分别先垂直相加后再水平相加, 最后的结果是一致的, 得 1010。后一种对部分积先进 行水平相加的方法就是查找表法。由于 FIR 滤波器的 h( n) 均为常数, x( n) 的最低位为 1001, 则 p1( n) 的值为 h( 0) +h( 3) , 其高位为 1010, 则 p2( n) 的值为 h( 1) +h( 3) 。 因此可利用 FLEX10K系列的查找表结构, 先将 h( n) 的 各种组合存入查找表, 这样卷积运算可用加法来代替。 将 p2( n) 左移一位与 p1( n) 相加即可。对于笔者所要实 现的 16 阶线性相位 FIR 滤波器来说, 需要 2 个查找表 来实现, 这是由 FLEX10K 系列器件的四输入查找表结 构来决定的。

【摘 要 】 提 出 了 一 种 基 于 FPGA 的 FIR 线 性 相 位 滤 波 器 设 计 方 案 , 充 分 利 用 FPGA 四 输 入 查 找 表 LUT 结 构 构 成

向量乘法器, 给出了对应的 VHDL 源 程序 及 仿 真结 果 , 并 讨论 了 设 计误 差 原 因及 改 进 措施 。与 普 通滤 波 器 相比 , 基

LU Yu- peng, QIU Hong- an, TIAN Duo- hua, SHAO Li- qun

( College of Marine, Northwest Polytechnical University, Xi′an 710072, China)