(优选)南京邮电大学微电子导论期末复习Ppt

微电子学概论 ppt课件

自1968年开始,硅技术为代表的信息技术领域的学术 论文超过了以钢铁技术为代表的机械领域的学术论文

PPT课件

PPT课件

PPT课件

11个国家集成电路人才 培养基地

一. 微电子技术与半导体集成电路

微电子学- 信息科学的基础 研究在固体(半导体)材料上构成的微小型化电路、子系统及系统 的电子学分支,研究芯片级微电路系统的科学。研究电子或离子在 固体材料中的运动规律及其应用,并实现信号处理。

PPT课件

课程内容及学时安排 2学分 32学时

第一章 概论 (多媒体)

3 学时

第二章 集成器件物理基础(部分多媒体)

12学时

第三章 集成电路制造工艺 (多媒体)

7 学时

第四章 集成电路设计(多媒体)

4 学时

第五章 微电子系统设计 (多媒体)

2 学时

第六章 集成电路C A D技术(计算机辅助设计) 4 学时

PPT课件

除了自身对国民经济的巨大贡献之外

PPT课件

采用交流传动改造后,电力机车可节电20%-30% 内燃机车可节油12%-14%

全国一半以上中等城市的自来水公司,在管网自动 检测和生产调度中使用计算机控制,可使自来水流 失率降低50%

PPT课件

PPT课件

PPT课件

人类社会的材料(主要) 宽禁带半导体材料(GaAs)

微电子学概论

PPT课件

教学目的

了解微电子学发展历史及在科学技术、国民经济、国家安全

的重要战略作用。

对微电子技术发展过程中的一些基本规律、发展前景的展望

和进行预测;对充分反映微电子技术领域的最新成果、体现前 沿性和时代性等进行了解。

在半导体物理基础上,对半导体器件基础、大规模集成电路

南邮通达微机期末复习共29页

南邮通达微机期末复习

51、没有哪个社会可以制订一部永远 适用的 宪法, 甚至一 条永远 适用的 法律。 ——杰 斐逊 52、法律源于人的自卫本能。——英 格索尔

53、人们通常会发现,法律就是这样 一种的 网,触 犯法律 的人, 小的可 以穿网 而过, 大的可 以破网 而出, 只有中 等的才 会坠入 网中。 ——申 斯通 54、法律就是法律它是一座雄伟的大 夏,庇 护着我 们大家 ;它的 每一块 砖石都 垒在另 一块砖 石上。 ——高 尔斯华 绥 55、今天的法律未必明天仍是法律。 ——罗·伯顿

南邮模电c期末复习第三章

0.02m

ICQ IBQ 100 0.02 2m

UCEQ UCC ICQ RC 12 2 3 6V

2. 静态工作点的图解分析法

直流图解分析是在晶体管特性曲线上,用作图的方法确 定出直流工作点,并求出IBQ、UBEQ和ICQ、UCEQ。

以左图为例,说明如何通过图解分 析法确定放大电路的静态工作点。

地收集载流子。

c

c

2. 外部条件

b

b

NPN

PNP

发射结(eb结)正偏 集电结(cb结)反偏

e

e

UC > UB> UE UC < UB < UE

共射输出特性曲线可分为4个区域(饱和区、放大区、截

止区、击穿区)。

iC/mA uCE=uBE

饱4

和 区3

放

击

大

2

区

1

穿 区

0

5

10 15 截止区

iB=-ICBO uCE/V

RC=RL=2kΩ, RE=1kΩ, UCC=12V, β=80, rbb′=100Ω, Rs=0.6kΩ, 试求直流工作点ICQ, UCEQ及Au, Ri, Ro和Aus 等项指标。

直流通路

解: 画出直流通路,用估算法计算静态工作点Q:

UB

RB 2 RB1 RB2

U CC

25 12 75 25

c 集电极 collector

NPN

b

c

N

集电区

base

集电结

e

b

P

基极

基区

N+

发射区

发射结

发射极箭头方向是指发 射结正偏时的电流方向

PNP

微电子学概论PPT课件

的特点

集成电路的分类

导论

晶体管的 发明

集成电路 发展历史

集成电路 的分类

微电子学 的特点

集成电路的分类

器件结构类型 集成电路规模 使用的基片材料 电路形式 应用领域

器件结构类型分类

导论

晶体管的 发明

集成电路 发展历史

集成电路 的分类

微电子学 的特点

集成电路(IC)产值的增长率(RIC)高于电子 工业产值的增长率(REI)

电子工业产值的增长率又高于GDP的增长率 (RGDP)

一般有一个近似的关系

RIC≈1.5~2REI REI≈3RGDP

微电子学发展情况

导论

晶体管的 发明

集成电路 发展历史

集成电路 的分类

微电子学 的特点

世界GDP和一些主要产业的发展情况

晶体管的 发明

集成电路 发展历史

集成电路 的分类

微电子学 的特点

1947年12月13日 晶体管发明 1958年 的一块集成电路 1962年 CMOS技术 1967年 非挥发存储器 1968年 单晶体管DRAM 1971年 Intel公司微处理器

摩尔定律

导论 晶体管的

发明 集成电路

发展历史 集成电路

高集成度、低功耗、高性能、高可靠性是微电 子学发展的方向

微电子学的渗透性极强

它可以是与其他学科结合而诞生出一系列新的 交叉学科,例如微机电系统(MEMS)、生物芯 片等

作业

微电子学?

导论 晶体管的

微电子学核心?

发明 微电子学主要研究领域?

集成电路 发展历史

微电子学特点?

集成电路 集成电路?

的分类

例如数模(D/A)转换器和模数(A/D)转换器等

南京邮电大学交换技术期末总结幻灯片

7

3

D

VPI=3,VCi=3,4

Banyan 的内部竞争例如

B-B网络

ATM交换构造的内部的选路

• 选路的分类 按照确定路由的时间的不同,可以分为面向连接选路和 无连接选路

• 按照路由信息存放位置的不同可以分为自选路由和表格控制。

b

468

通路选择(内部空闲时隙的确定

31 00

11

5

……

…… …… 1

0 01

…….

110000…………0100000

150 16 110000…………0100000

110000…………0100000

31 010000…………0100000

NW32

NW3 1

31

5

0

0 110000…………0100000

ATM 中VPI 的应用

VPI in /VPI out

VPI=7,VCI=1,2,3

7

5

A

9

7

ATM交

换机

VPI=5,VCI=1,

2,3

B

VPI=9,VCI=3,4

VPI=7,VCI=3,4

VPI=7,VCI=1,2,3

ATM交换

C

机

VPI in /VPI out

5

7

ATM交换 机

VPI in / VPI out

………..

15 110100…………0100001

16 010100…………0100000

……

27

…… 1 …… ……

31 110000…………0100000

27=11+16

NW 1

A B 内部时隙

(NW32忙闲表第WC行)∧(NW1忙闲表第WC行+16行)所 得的结果中“1”所对应的那个时隙

[最终版]微电子复习

![[最终版]微电子复习](https://img.taocdn.com/s3/m/48a53600ddccda38376bafe3.png)

[最终版]微电子复习五哥祝你考试成功!微电子复习-晶体管的发明:1947年12月23日,Bell实验室发明,由肖克莱、巴丁和布拉顿发明。

1950年,肖克莱、帕克斯、迪尔发明NPN。

肖克莱、巴丁和布拉顿于1956年获得诺贝尔物理学奖。

-集成电路:1952年5月,英国皇家研究所的达默提出集成电路的设想。

1958年,德州仪器的基尔比制出第一块集成电路。

按结构形式分为:单片集成电路、混合集成电路。

-摩尔定律:书:集成电路的集成度每3年增长4倍,特征尺寸每3年缩小√2倍。

Wiki:(集成电路(IC)上可容纳的晶体管数目,约每隔24个月(1975年摩尔将24个月更改为18个月)便会增加一倍,性能也将提升一倍,当价格不变时;或者说,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。

这一定律揭示了信息技术进步的速度。

)瓶颈主要由封装技术来突破。

(3V、TSV技术等为重点)-单质半导体:有硅和锗,锗是一开始使用的。

-PN结的击穿分为:雪崩击穿和隧道击穿(齐纳击穿)。

雪崩击穿:增强的反向偏压使得大能量的电子空穴将满带电子激发到导带,而形成电隧道击穿:偏压足够高时,能带的弯曲使得一部分价带电子在能量上达到甚至超过导子-空穴对,“碰撞电离”新载流子又形成更多的电离载流子,雪崩倍增。

带的能力,而且禁带宽度随陡度增大而减小,隧穿电流从价带进入导带的几率大大增加。

-电子的微观运动:变。

-武哥祝你考试成功1.量子态:电子作稳恒运动,具有完全确定的能量。

同一量子态上只能有一个电子。

2.量子跃迁:在一定条件下,电子可以发生从一个量子态转移到另一个量子态的突能带论:-电子共有化:半导体由大量原子构成。

原子之间很近,一个原子的外层电子不仅受本原子作用,还受到相邻原子的作用;这样,他就与相邻原子的电子的量子态形成一定的交叠。

通过交替,电子可以从一个原子转移到相邻原子上。

当原子组成晶体后,电子不再固定在个别原子上运动,而是穿行于整个晶体的运动。

微电子课件

电阻率

影响迁移率的因素: 有效质量 平均弛豫时间(散射〕

体现在:温度和 掺杂浓度

q

m

半导体中载流子的散射机制: 晶格散射( 热 运 动 引 起) 电离杂质散射

散射机理 晶格散射

杂质散射

+ +

迁移率与掺杂浓度的关系

迁移率与温度的关系

总复习第2章

pn结部分 (1)什么叫pn结,如何形成的

gm

iDቤተ መጻሕፍቲ ባይዱuGS

|uDS 常数

结型场效应管

栅源电压对沟道的控制作用

在栅源间加负电压uGS ,令uDS =0 ①当uGS=0时,为平衡PN结,导电沟道最宽。 ②当│uGS│↑时,PN结反偏,形成耗尽层,导电沟道变窄,沟

道电阻增大。 ③当│uGS│增加到一定值Up时 ,沟道会完全合拢。

结型场效应管

半导体的能带结构

导带

Eg

价带

价带:被电子填充的能量最高的能带 导带: 未被电子填充的能量最低的能带 禁带:导带底与价带顶之间能带 带隙:导带底与价带顶之间的能量差

金属导体Eg=0

绝缘体Eg很大 10eV以上

半导体Eg适中 在0.1-5eV

典型半导体禁带宽度

Si

1.1

Ge 0.67

GaAs 1.43

集成电路按器件结构可分为什么类型,各有什么特 点?

总复习第2章半导体物理

回答以下概念 (1)能带结构:导带、价带、禁带,多数载流子、 少数载流子, (2)本征、n型、p型半导体(费米能级位置) (3)施主杂质、受主杂质、施主能级、受主能级 (4)费米能级 (6)迁移率、晶格散射、杂质散射

什么叫迁移率,迁移率与温度以及掺杂浓度有什么 变化关系,并说明原因?

《微电子器件原理》复习题课件

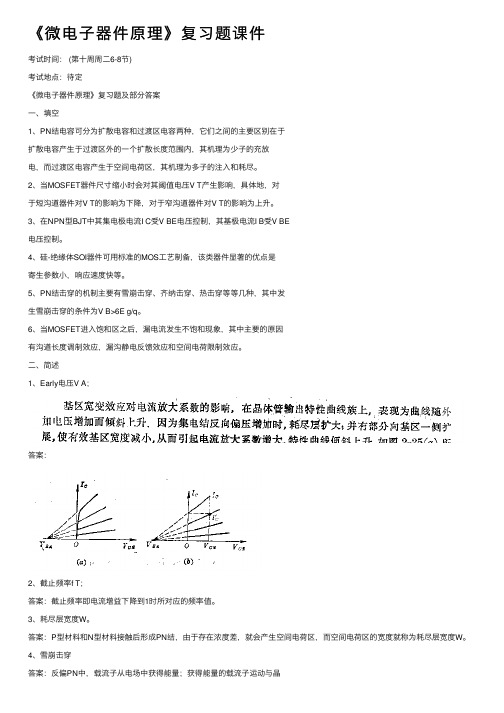

《微电⼦器件原理》复习题课件考试时间: (第⼗周周⼆6-8节)考试地点:待定《微电⼦器件原理》复习题及部分答案⼀、填空1、PN结电容可分为扩散电容和过渡区电容两种,它们之间的主要区别在于扩散电容产⽣于过渡区外的⼀个扩散长度范围内,其机理为少⼦的充放电,⽽过渡区电容产⽣于空间电荷区,其机理为多⼦的注⼊和耗尽。

2、当MOSFET器件尺⼨缩⼩时会对其阈值电压V T产⽣影响,具体地,对于短沟道器件对V T的影响为下降,对于窄沟道器件对V T的影响为上升。

3、在NPN型BJT中其集电极电流I C受V BE电压控制,其基极电流I B受V BE电压控制。

4、硅-绝缘体SOI器件可⽤标准的MOS⼯艺制备,该类器件显著的优点是寄⽣参数⼩,响应速度快等。

5、PN结击穿的机制主要有雪崩击穿、齐纳击穿、热击穿等等⼏种,其中发⽣雪崩击穿的条件为V B>6E g/q。

6、当MOSFET进⼊饱和区之后,漏电流发⽣不饱和现象,其中主要的原因有沟道长度调制效应,漏沟静电反馈效应和空间电荷限制效应。

⼆、简述1、Early电压V A;答案:2、截⽌频率f T;答案:截⽌频率即电流增益下降到1时所对应的频率值。

3、耗尽层宽度W。

答案:P型材料和N型材料接触后形成PN结,由于存在浓度差,就会产⽣空间电荷区,⽽空间电荷区的宽度就称为耗尽层宽度W。

4、雪崩击穿答案:反偏PN中,载流⼦从电场中获得能量;获得能量的载流⼦运动与晶格相碰,使满带电⼦激出到导带,通过碰撞电离由电离产⽣的载流⼦(电⼦空⽳对)及原来的载流⼦⼜能通过再碰撞电离,造成载流⼦倍增效应,当倍增效应⾜够强的时候,将发⽣“雪崩”——从⽽出现⼤电流,造成PN结击穿,此称为“雪崩击穿”。

5、简述正偏PN结的电流中少⼦与多⼦的转换过程。

答案:N型区中的电⼦,在外加电压的作⽤下,向边界Xn漂移,越过空间电荷区,在边界Xp形成⾮平衡少⼦分布,注⼊到P区的少⼦,然后向体内扩散形成电⼦扩散电流,在扩散过程中电⼦与对⾯漂移过来的空⽳不断复合,结果电⼦扩散电流不断转为空⽳漂移电流.空⽳从P区向N区运动也类同.6、太阳电池和光电⼆极管的主要异同点有哪些?答案:相同点:都是应⽤光⽣伏打效应⼯作的器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

沟道长度:越长,K越小; 沟道宽度:越宽,K越大; 沟道浓度:影响不大。

第四章重点与难点小结

•图形转换:

–光刻:接触光刻、接近光刻、投影光刻 –刻蚀:干法刻蚀、湿法刻蚀

•掺杂:

–扩散:固态源、液态源、气态源 –离子注入

NA(y1)=ND0,代入数值,解得y1=0.0003cm=3um

NA(xjN)=ND(xjN)+ND0,代入数值,解得y2=0.0001cm=1um

因为在推结过程中横向扩展是纵向结深的0.8倍。故

△x=0.8(y1-y2)=1.6um

ND0=3 y

4-5

4-5

4-6

(1)预氧

(2)淀积Si3N4

3-1

ND xN N AxP

xM xP xN 1.44m

xN

N A xP ND

n

ni2

/

NA

0.54m

ND

N

xP' xN' 1.6m 51015 xN' 31015 xP'

xN' 0.6m xP' 1.0m

XN

XP X

NA

3-2

• 3-2一个硅PN结二极管,室温(300K)下饱 和电流为1.48×10-13A,正向电流已知为 0.442A,求此时的正向电压。

电子科学与工程学院 郭宇锋

第三章重点与难点小结

• PN结形成的微观过程、空间电荷区、PN结 的能带、PN结的正向偏置与反向偏置、雪 崩击穿的物理过程、PN结的IV特性和应用

• 双极晶体管的结构、共发射极接法、电流 增益和电流传输率、晶体管特性曲线及其 分区。双极晶体管的应用和特点。

• MOS场效应晶体管的基本结构和分类、阈 值电压的概念和影响因素、N MOSFET工作 机理、I-V特性曲线及其分区、 MOSFET的应 用和特点。

解:第一次掺杂:半导体为P型

多子为空穴:

p N A 31015 cm3

少子为电子:

n ni2 / N A 7.5104 cm3

第二次掺杂:半导体由P型变为N型。

多子为电子: 少子为空穴:

n ND N A 1.51015 cm3

n ni2 /(ND N A ) 1.5105 cm3

P-MOSFET 与N-MOSFET

ID

线 性 区

VGS50>VGS>VVGTS1

VDS

截止区

饱和区VGLeabharlann 4VGS2VGS3

VGS3

线 性

饱和区

区

VGS2

VGS4

截止区

VGS1

VGS<VT VDS

NMOS I-V特性曲线

VGS5

ID PMOS I-V特性曲线

思考题

•思考题:设ID K (VGS VT 0.5VDS )VDs

(优选)南京邮电大学微电子 导论期末复习

10/9/2020

第一章 重点与难点小结

• 微电子学的概念和特点、集成电路的概念和作用、半导 体、微电子和集成电路的关系。

• 微电子技术的战略地位、发展动力和对传统产业的渗透 与带动作用。

• 微电子技术的历史:摩尔定律、第一台通用电子计算机、 第一个晶体管、第一块集成电路、第一台微处理器、我 国第一款商品化通用高性能CPU。

(VGS VT )VDs 0.5VD2S (VGS VT )VDs

3-6

源极

V栅T <极VGS<0

VDS<0 漏极

VDS

IDS

P+

P+

N

(1)VT<VGS<0,VDS<0:漏结耗尽区扩展,使得栅极下方耗尽区宽 ID 度从源到漏逐渐增加,晶体管截止,IDS=0。

3-6

源极 P+

V栅T <极VGS<0

(3)光刻Si3N4(M1)

(4)刻蚀SiO2

(5)高压氧化

(6)刻蚀Si3N4

(7)刻蚀SiO2

(8)生长栅氧

(9)淀积多晶硅

(10)光刻多晶(M2)

(11)注入P

Vsat < 漏极

VDS<0

VDS

IDS

P+

N

(2)VGS<VT<0, Vsat<VDS<0:栅极下方耗尽区宽度从源到漏逐渐增加ID , 而反型层宽度从源到漏逐渐减小,ID随VDS减小而线性增加。

3-6

源极

V栅T <极VGS<0

VDS=Vsat<0 漏极

VDS

IDS

P+

P+

N

Vsat=VGS-VT Isat

质半导体、施主、受主、杂质能级 • 电子和空穴、本征载流子浓度及其影响因素、 • 多子和少子、电中性条件 • 半导体中的载流子浓度计算、载流子的输运机制:

扩散运动和漂移运动、影响扩散电流的因素、影 响漂移电流的因素。迁移率的概念和影响因素 • 载流子的复合

2-1,2-2

2-3

微电子器件基础

• 2-3在室温下的单晶硅进行硼掺杂,硼的浓度为 3×1015cm-3。试求半导体中多子和少子的浓度。若 再掺入浓度为4.5×1015cm-3的磷,试确定此时硅的导 电类型,并求出此时的多子和少子浓度。

解:由

qV

得:

I Is (e kT 1)

V

kT q

ln I

/

Is

1

0.74V

3-3

1

Ic / Ie Ic Ic Ic / Ie

Ib Ie Ic 1 Ic / Ie 1

3-4

Ie

Ib

Ic

Ib

Ib

1

1

I

b

Ib

1

5mA

3-5

ID (VGS VT )VDs ID (VGS VT 0.5VDS )VDs

• 微电子技术的现状与挑战:微电子产业链及其特点、微 电子产业面临的挑战。

• 我国的微电子产业:历史、产业化基地、产业分布、紧 缺人才。

第二章重点与难点小结

• 半导体材料的分类、硅的晶体结构 • 能带理论的三个假设、能带、满带、空带、价带、

导带、禁带、带隙(禁带宽度)等的概念 • 电子的跃迁、固体的导电模型、本征半导体与杂

(3)VGS<VT<0, VDS=Vsat<0:漏结边缘反型层宽度减小到零,ID达ID 到最大值。

上一专题习题答案

源极 P+

V栅GS<极VT<0

VDS<Vsat<0 漏极

VDS

IDS

P+

N

Vsat=VGS-VT Isat

(4)VGS<VT<0, VDS<Vsat<0 :沟道被夹断,随着VDS的减小有效沟道长度减小,ID饱和。 ID

•制膜:

–氧化:干氧氧化、湿氧氧化等 –CVD:APCVD、LPCVD、PECVD –PVD:蒸发、溅射

•N+埋层双极工艺流程 •N阱CMOS工艺流程

4-1

4-2,4-3

4-4

N(×1016cm-3)

△x

x

y2 y1

y

ND=30-20y NA=18-5y

在结的边界上净杂质含量为零。故

y2 y1