基于FPGA的多功能信号发生器

基于FPGA技术的多功能DDS信号发生器设计

·16·仪表技术2007年第8期基于FPGA技术的多功能DDS信号发生器设计蔡丽1,翟小东1,高云红2(1.中国矿业大学信电学院,江苏徐州221008;2.沈阳航空工业学院自动控制系,辽宁沈阳110034)摘要:介绍DDS的基本理论及新型FPGA器件(EPlKl0)的特点,并结合EPIKIO对DDS信号发生器的设计过程及优化方案进行论述。

最终实现频率、相位、复合渡形皆可调节的直接数字合成的信号发生器。

关键词:直接数字合成器;单片机;FPGA;复合波形中图分类号:TM930文献标识码:B文章编号:1006—2394(2007)08—0016—02ADesignofMulti-purposeDDSSignalGeneratorBasedonFPGATechnologyCAILil.ZHAIXiao.don91,GAOYun.hon92(1.CollegeofInformationandElectricalEngineeringofCUMT,Xuzhou221008,China;2.DepartmentofAutomaticControl,ShenyangInstituteofAeronauticalEngineering,Shenyang110034,China)Abstract:ThebasictheoryofDigitalDirectSynthesizerandmainpointofnewFPGAdeviceEPlK10,andhowtoimplementtheDDSsignalgeneratordesignwithinEPlK10introducedinthispaper.TheDDSsignalgeneratorwhichcanadjustsignalphase,signalfrequencyandcomplexwaveisdesigned.Keywords:directdigitalsynthesizer;singlechipmicrocomputer;FPGA;complexwave1多功能直接数字频率合成DDS原理假设正弦信号的表达式为如下:Y=Asin(p+妒o)(1)Y=Asin(2rrfi+够o)=Asin2-rr(fi+90/2曩-)(2)式(1)中9为正弦函数的相位,妒。

基于FPGA的DDS信号发生器的研究--毕业论文

第1章绪论1.1 课题背景频率检测是电子测量领域的最基本也是最重要的测量之一,频率信号抗干扰强,易于传输,可以获得较高的测量精度,所以频率方法的研究越来越受到重视[1]。

在频率合成领域中,直接数字合成(Direct Digital Synthesizer,简称:DDS)是近年来新的技术, 它从相位的角度出发直接合成所需波形。

它是由美国人J.Tierncy首先提出来的,是一种以数字信号处理理论为基础,从相位概念出发直接合成所需波形的一种新的全数字技术的频率合成方法[2]。

其主要优点有:频率改变速度快、频率分辨率高、输出相位连续、可编程、全数字化便于集成等,目前使用最广泛的一种DDS频率合成方式是利用高速存储器将正弦波的M个样品存在其中,然后以查找的方式按均匀的速率把这些样品输入到高速数模转换器,变成所设定频率的正弦波信号[3]。

近30年来,随着超大规模集成、现场可编程门阵列(Field Programmable Gate Array,简称:FPGA)、复杂可编程器件(Complex programmable Logic Device,简称:CPLD)等技术的出现以及对DDS理论上的进一步探讨,使得DDS技术得到了飞速的发展。

它已广泛应用于通讯、雷达、遥控测试、电子对抗、以及现代化的仪器仪表工业等许多领域。

DDS的数字部分,即相位累加器和查表,被称为数控振荡器(NCO)[4]。

波形发生器即通常所说的信号发生器是一种常用的信号源,和示波器、电压表、频率计等仪器一样是最普遍、最基本也是应用最广泛的的电子仪器之一,几乎所有电参量的测量都要用到波形发生器。

不论是在生产还是在科研与教学上,波形发生器都是电子工程师信号仿真试验的最佳工具。

随着现代电子技术的飞速发展,现代电子测量工作对波形发生器的性能提出了更高的要求,不仅要求能产生正弦波、方波等标准波形,还能根据需要产生任意波形,且操作方便,输出波形质量好,输出频率范围宽,输出频率稳定度、准确度及分辨率高,频率转换速度快且频率转换时输出波形相位连续等。

基于FPGA的实用多功能信号发生器的设计与制作

基于FPGA的实用多功能信号发生器的设计与制作基于FPGA的实用多功能信号发生器的设计与制作摘要多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数信号发生器的研究背景和DDS的理论。

然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。

文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。

文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。

包括由LCD显示和按键输入构成的人机界面和多种信号的发生。

数字模拟转换器是BURR-BROWN 公司生产的DAC902。

该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。

关键词:信号发生器;DDS;FPGA;DE2Practical FPGA-based multi function signal generatordesign and productionAbstractMulti function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs.Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results.This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN.This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed.Key Words: Signal generator; DDS; FPGA; DE2目录论文总页数:34页1 引言 (1)1.1课题背景 (1)1.2国内外波形发生器的发展现状 (1)1.3本文研究的主要内容 (2)2 信号发生器原理 (2)2.1直接数字频率合成技术的基本原理 (2)2.2相位偏移控制 (3)2.3多种信号的发生 (3)2.3.1方波的发生 (3)2.3.2三角波发生 (4)2.2.3锯齿波发生 (4)2.3.4 PWM信号发生 (4)2.3.5 SPWM信号发生 (5)2.3.6 AM信号发生 (5)2.3.7 FM信号发生 (6)2.4DDS的特点 (7)2.4.1 DDS 的优点 (7)2.4.2 DDS 系统的缺点 (7)3 系统整体设计 (8)3.1硬件部分 (8)3.1.1 DE2实验板 (8)3.1.2 LCD模块 (9)3.1.2 DAC902 (11)3.2基于VERILOG的FPGA设计 (12)3.3软件工具 (12)3.3.1 Modelsim (12)3.3.2 Quartus (12)3.4系统设计 (13)3.4.1 系统初始化模块 (13)3.4.2按键模块和LCD模块 (13)3.4.3 RAM模块 (14)3.4.4数据转换模块 (15)3.4.5 DAC驱动模块 (15)3.4.6系统的运行 (15)4 VERILOG HDL代码实现与仿真 (15)4.1信号发生器模块 (15)4.1.1频率控制字和相位累加器 (15)4.1.2 相位偏移控制 (16)4.1.3正弦波发生模块 (17)4.1.4 方波发生模块 (17)4.1.5 三角波发生模块 (18)4.1.6 锯齿波发生模块 (18)4.1.7 PWM信号发生模块 (19)4.1.8 SPWM信号发生模块 (19)4.1.9 AM信号发生模块 (20)4.1.10 FM信号发生模块 (21)4.2按键输入模块 (22)4.3LCD显示模块 (23)4.4RAM模块 (24)4.5数据转换模块 (25)5 系统测试 (26)5.1控制及显示部分测试 (27)5.2输出频率测试 (27)5.3信号发生测试 (28)5.3.1 正弦波、方波、三角波、锯齿波测试 (28)5.3.2 PWM信号测试 (29)5.3.3 SPWM信号测试 (29)5.3.4 AM信号测试 (29)5.3.5 FM信号测试 (30)结论 (31)参考文献 (32)致谢...................................................... 错误!未定义书签。

基于FPGA的多功能信号发生器的设计

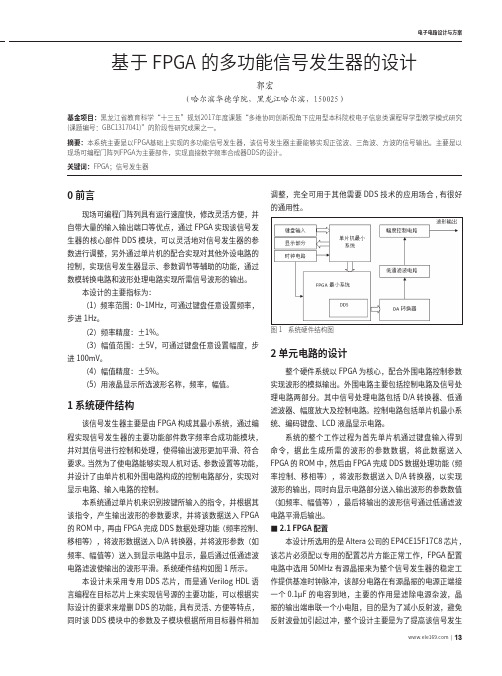

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

基于DDS和FPGA的多功能信号发生器设计

基于DDS和FPGA的多功能信号发生器设计王新辉【摘要】根据直接数字频率合成技术,以FPGA为核心,设计了一种便携式多功能信号发生器,可产生正弦波、方波、三角波、锯齿波等信号。

通过仿真及硬件实验表明,该信号发生器具有信号频率误差小、分辨率高、体积小、质量轻等优点。

%According to direct digital synthesis(DDS),a portable multi-functional signal generator was designed based on FPGA,which could output sinusoidal wave,square wave,triangle wave and sawtoothwave.Simulation and hardware experiment show that the portable multi-functional signal generator has some advantages,such as high accuracy and high resolution with small size.【期刊名称】《湖南人文科技学院学报》【年(卷),期】2011(000)002【总页数】4页(P91-94)【关键词】DDS;FPGA;D/A转换器;信号发生器【作者】王新辉【作者单位】湖南人文科技学院计算机科学技术系,湖南娄底417001【正文语种】中文【中图分类】TP346近年来,随着微电子技术的迅速发展,模拟信号发生器在带宽,精确度,可控制性等方面体现出严重缺限;而直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)在相对带宽、频率转换时间、高分辨力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能,输出频率相对带宽较宽的信号;输出波形的灵活性,只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实现调频、调相和调幅功能,产生FSK、PSK、ASK和MSK等信号。

基于FPGA的多功能信号发生器设计与实现

基于FPGA的多功能信号发生器设计与实现刘艳昌;左现刚;李国厚【摘要】针对传统采用单片机和DDS芯片设计信号发生器的方法具有可移植性差、硬件结构和编写DDS源程序复杂等问题,提出了基于FPGA的多功能信号发生器设计方法。

采用MATLAB/Simulink和DSP Builder对DDS系统模型进行建模和仿真,并用Signal Compiler工具对模型进行编译,产生Quartus I能够识别的VHDL源程序,并在Quartus I环境中生成硬件符号,最终将顶层文件编译、综合后下载到FPGA器件中,可产生频率、幅度相位均可调的基本波、AM调制波和数字调制波。

测试结果表明,该系统具有设计灵活、实现简单、参数易调整、可移植性好、输出波形性能稳定和精度高等优点。

【期刊名称】《制造业自动化》【年(卷),期】2014(000)020【总页数】6页(P100-104,108)【关键词】FPGA;多功能信号发生器;DDS;MATLAB/DSP Builder【作者】刘艳昌;左现刚;李国厚【作者单位】河南科技学院信息工程学院,新乡453003;河南科技学院信息工程学院,新乡453003;河南科技学院信息工程学院,新乡453003【正文语种】中文【中图分类】TN91;TP3350 引言信号发生器在工业、科技、教学等领域中已得到广泛应用,通常情况下使用较多的设计方案是利用FPGA、单片机等处理器芯片来控制专用信号发生芯片,这种设计方案与传统采用模拟分立器件来设计信号发生器的方法相比,具有信号频率更稳定、精度更高、信号参数易调节等优点,但存在电路设计复杂,成本较高等问题。

随着电子技术和EDA技术的快速发展和深入研究,DDS技术得到飞速发展[1],使得信号发生器的设计和实现更加容易和灵活。

DDS即直接频率合成器,与传统频率合成技术相比,具有频率分辨率高、频率切换速度快、频率改变时相位连续性保持不变和频率稳定度高等优点,因此极易实现信号的频率、相位和幅度控制。

基于FPGA的多功能信号发生器

基于FPGA的多功能信号发生器一.实验目的:1.了解GW48-CK综合实验箱结构2.熟悉VHDL语言3.了解FPGA芯片<EP1K30TC144-3)结构及引脚4.了解D/A芯片<DAC0832)结构[5.熟悉FPGA设计软件quartus ii 9.0的使用6.掌握产生三角波,锯齿波,梯形波的原理7.学会用FPGA设计多功能信号发生器二.实验仪器及设备:1.pc机2.GW48-CK型FPGA综合实验箱3.FPGA芯片:EP1K30TC144-34.D/A芯片:DAC08325.示波器6.quartus ii 9.0仿真软件三.实验要求:.设计基于FPGA的多功能信号发生器,此信号发生器可产生的波形有:正弦波,方波,三角波,斜升锯齿波,斜降锯齿波,梯形波,阶梯波,双阶梯波中的六种。

F1NgHcUqUBb5E2RGbCAP设计软件要求用quartus ii,先用该软件仿真,再接上FPGA实验箱,编译,运行并下载到实验箱,用示波器观察期指定输出端波形。

F1NgHcUqUBp1EanqFDPw四.实验原理:1.基于QUASTUS II 9.0平台,利用DDS<直接数字信号合成)技术,采用VHDL语言,设计一波形信号发生器。

首先根据对各波形的幅度进行采样,获得各波形的波形数据表,然后FPGA根据输入的时钟<频率可根据要求可变)作为地址信号,从FPGA数据线上输出相应的波形数据,再送入GW48-CK实验板上的D/A转换芯片进行转换为模拟信号,最后送入滤波电路滤波后输出。

F1NgHcUqUBDXDiTa9E3d2.实验整体框图如下:由方波模块<niushengli_fb)、阶梯波模块<niushengli_jtb)、正弦波模块<niushengli_sin)、三角波模块<niushengli_sjb)、斜升锯齿波模块<niushengli_xsjcb)、斜降锯齿波模块<niushengli_xjjcb)、6选1选择器<niushengli_mux61)以及反向器<not)组成。

基于FPGA的多用途信号发生器的设计

基于FPGA的多用途信号发生器的设计黎燕兵;万生鹏;胡元华;曾少航【摘要】To obtain different modulating and driving signals suiting for optical fiber sensing and optical fiber communication system,a design scheme of the multipurpose signal generator based on FPGA is proposed. In the scheme,the FPGA device is taken as the hardware platform,and the frequency division technology and DDS technology are used to generate the arbitrary low and medium frequency signal,and output a pulse signal,a DDS signal and DC signal at the same time. Both pulse width and repetition frequency of the pulse signal can be regulated by control keys. The minimum pulse width of pulse signal can reach up to 8 ns,the minimun pulse width deviation is less than 0.5 ns,and the repetition frequency is adjusted from 0.05 Hz to 100 MHz. The output frequency range of the DDS signal is 0.058 2 Hz~100 kHz,and the minimum frequency can reach up to 0.058 2 Hz. The experimental results show that all signals generated by the signal generator have good stability and high preci⁃sion,and the generator is suitable for various fields.%为了获得适用于光纤传感及光纤通信系统的各种调制及驱动信号,提出了一种基于FPGA的多用途信号发生器的设计方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的多功能信号发生器一.实验目的:1.了解GW48-CK综合实验箱结构2.熟悉VHDL语言3.了解FPGA芯片<EP1K30TC144-3)结构及引脚4.了解D/A芯片<DAC0832)结构[5.熟悉FPGA设计软件quartus ii 9.0的使用6.掌握产生三角波,锯齿波,梯形波的原理7.学会用FPGA设计多功能信号发生器二.实验仪器及设备:1.pc机2.GW48-CK型FPGA综合实验箱3.FPGA芯片:EP1K30TC144-34.D/A芯片:DAC08325.示波器6.quartus ii 9.0仿真软件三.实验要求:.设计基于FPGA的多功能信号发生器,此信号发生器可产生的波形有:正弦波,方波,三角波,斜升锯齿波,斜降锯齿波,梯形波,阶梯波,双阶梯波中的六种。

F1NgHcUqUBb5E2RGbCAP设计软件要求用quartus ii,先用该软件仿真,再接上FPGA实验箱,编译,运行并下载到实验箱,用示波器观察期指定输出端波形。

F1NgHcUqUBp1EanqFDPw四.实验原理:1.基于QUASTUS II 9.0平台,利用DDS<直接数字信号合成)技术,采用VHDL语言,设计一波形信号发生器。

首先根据对各波形的幅度进行采样,获得各波形的波形数据表,然后FPGA根据输入的时钟<频率可根据要求可变)作为地址信号,从FPGA数据线上输出相应的波形数据,再送入GW48-CK实验板上的D/A转换芯片进行转换为模拟信号,最后送入滤波电路滤波后输出。

F1NgHcUqUBDXDiTa9E3d2.实验整体框图如下:由方波模块<niushengli_fb)、阶梯波模块<niushengli_jtb)、正弦波模块<niushengli_sin)、三角波模块<niushengli_sjb)、斜升锯齿波模块<niushengli_xsjcb)、斜降锯齿波模块<niushengli_xjjcb)、6选1选择器<niushengli_mux61)以及反向器<not)组成。

F1NgHcUqUBRTCrpUDGiT五.实验步骤:在桌面上双击quartus ii 9.0图标<或在开始中→程序→Alera→quartus ii 9.0)启动设计软件。

F1NgHcUqUB5PCzVD7HxA新建工程命名(niushengli_xhfsq>,在新建VHDL文本文件,分别输入正弦波、方波、三角波、斜升锯齿波,梯形波,斜降锯齿波以及6选1选择器程序。

F1NgHcUqUBjLBHrnAILg点击保存并命名<注意:命名应与程序实体名相同,后缀为:.vhd),编译,若有错误,则调试程序直至编译成功F1NgHcUqUBxHAQX74J0X新建模块/原理图输入方式文件,用编译后生成的各信号模块编写原理图文件并设置为顶层文件<命名为niushengli_xhfsq.bdf)保存F1NgHcUqUBLDAYtRyKfE新建一个仿真波形文件,添加输入/输出信号节点,编辑信号节点波形并保存<命名为:niushengli_xhfsq.vwf)F1NgHcUqUBZzz6ZB2Ltk点击Assignments菜单,选择目标芯片<EP1K30TC144-3)并进行管脚配置<详情见附录3)F1NgHcUqUBdvzfvkwMI1点击编译器processing/Start Compilation,再点击Start Simulation命令启动仿真器,查看仿真波形并记录F1NgHcUqUBrqyn14ZNXI连接好pc机和GW48-CK实验箱,下载编译好的程序到实验箱,用示波器观察输出端波形,检验设计的信号发生器功能并记录F1NgHcUqUBEmxvxOtOco六.实验结果:a)当键3、键2、键1组合为000时,输出方波仿真图形记录如下:b)当键3、键2、键1组合为001时,输出阶梯波仿真图形记录如下:c)当键3、键2、键1组合为010时,输出正弦波仿真图形记录如下:d)当键3、键2、键1组合为011时,输出三角波仿真图形记录如下:e)当键3、键2、键1组合为100时,输出斜降锯齿波仿真图形记录如下:f)当键3、键2、键1组合为101时,输出斜升锯齿波仿真图形记录如下:七.实验心的体会:通过俩周的设计,我的设计较好地完成了既定目标,能够产生正弦波、方波、三角波、锯齿波等6种波形,并能改变波形发生的频率。

通过三个按键组合,可在6种波形中任意切换,使所设计系统容易使用。

成功的实现了系统的功能。

F1NgHcUqUBSixE2yXPq5在实验中也有失败,如当经过几天的努力把各个信号模块做好后进行了整体的运作后,波形怎么也不出现。

后来才知道原来我们设计的电路只有在特定的实验箱特定的参数设置后才能实验成功,多亏老师的指导让我们少走很多弯路。

也从中发现自己还有很多知识不懂,最终把波形弄出来了!在这次设计中,我更进一步地了解了开发工程该如何组织进行,对正弦波信号发生器、方波信号发生器、三角波信号发生器、锯齿波信号发生器的实现有了更好的理解。

同时也提高了查阅文档解决问题的能力,对EDA技术的运用有了深一层的认识,对VHDL程序语言设计有了更深的理解,并熟练掌握了杭州康芯硬件结构动态可配置型EDA+SOPC实验箱、北京达盛公司全开方式EDA+SOPC实验箱的用法。

F1NgHcUqUB6ewMyirQFL通过本实验设计更增加了我对电子技术的热爱,对专业知识有了更透彻的认识!有因掌握了这一技术而更加自信。

相信通过今后的学习会更成为一个科技含量高的技术人才!在实验过程中,充分体会到团队精神的重要,我们很默契很团结,才最终把实验做成功。

通过实验也给自己一个成就感,让平时所学的知识有了实用的机会,达到了理论与实际相结合的目的,不仅学到了不少知识,而且锻炼了自己的能力,让我以后更有信心,无论遇到什么困难都要勇于克服,遇到问题要善于思考并虚心请教。

F1NgHcUqUBkavU42VRUs附录:<1).多功能信号发生器FPGA芯片配置说明:本次多功能信号发生器设计采用VHDL语言设计并通过QUARTUS II软件编译、仿真完成后,需将生成的配置文件下载到EDA实验箱中测试输出波形。

有关配制情况说明如下:F1NgHcUqUBy6v3ALoS891.实验平台:GW48系列EDA/SOC实验开发系统2.FPGA芯片型号:Altera EP1K30TC144-33.芯片管脚分配:<实验模式设置:5)(二>.程序:1. --锯齿波<斜升)LIBRARY IEEE。

USE IEEE. STD_LOGIC_1164.ALL。

USE IEEE.STD_LOGIC_UNSIGNED.ALL。

ENTITY niushengli_xsjcb IS -- 牛胜利<40604030109) PORT (clk,reset: IN STD_LOGIC。

q:OUT STD_LOGIC_VECTOR (7 DOWNTO 0>>。

END niushengli_xsjcb。

ARCHITECTURE behave OF niushengli_xsjcb ISBEGINPROCESS (clk,reset>VARIABLE tmp: STD_LOGIC_VECTOR (7 DOWNTO 0>。

BEGINIF reset='0'THEN tmp:="00000000"。

ELSIF clk'EVENT AND clk='1'THENIF tmp="11111111"THENtmp:="00000000"。

ELSE tmp:=tmp+1。

END IF。

END IF。

q<=tmp。

END PROCESS。

END behave。

2. --方波LIBRARY IEEE。

USE IEEE. STD_LOGIC_1164.ALL。

ENTITY niushengli_fb IS--牛胜利<40604030109) PORT (clk,reset: IN STD_LOGIC。

q:OUT INTEGER RANGE 0 TO 255>。

END niushengli_fb。

ARCHITECTURE behave OF niushengli_fb ISSIGNAL a: BIT。

BEGIN PROCESS (clk,reset>VARIABLE cnt: INTEGER。

BEGINIF reset='0'THENA<='0'。

ELSIF clk'EVENT AND clk='1'THEN IF cnt<63 THENCnt:=cnt+1。

ELSE cnt:=0。

a<=NOT a。

END IF。

END IF。

END PROCESS。

Process (clk,a>BEGINIF clk'EVENT AND clk='1'THEN IF a='1'THENQ<=255。

ELSEQ<=0。

END IF。

END IF。

END PROCESS。

END behave。

3. --双阶梯波library ieee。

use ieee.std_logic_1164.all。

use ieee.std_logic_unsigned.all。

entity niushengli_jtb isport(clk,reset:in std_logic。

q:out std_logic_vector(7 downto 0>>。

end niushengli_jtb。

architecture a of niushengli_jtb isbeginprocess(clk,reset>variable tmp:std_logic_vector(7 downto 0>。

beginif reset='0' thentmp:="00000000"。

else if clk'event and clk='1' thenif tmp="11111111" thentmp:="00000000"。

elsetmp:=tmp+16。

end if。

end if。

end if。

q<=tmp。

end process。