运放的减法电路

集成运放组成的基本运算电路

K2

C 1μF

R2 1M

K1 +15V

vS

-

R1 100K

A

vO

+

R′ 100K

-15V

vo

1 R1

t

0 vsdt

积分运算电路

4. 积分运算电路

将实验数据及波形填入下述表格中:

vs波形

vs幅度值

vo波形

vo频率

vo幅度值

5. 用积分电路转换方波为三角波

电路如下图所示。图中电阻R2的接入是为了抑制由 IIO、VIO所造成的积分漂移,从而稳定运放的输出零 点。

A

vO

υS

+

R′ 10K

-15V

v0

(1

RF R1

)vs

同相比例运算电路

2. 实现同相比例运算

将实验数据及波形填入下述表格中:

输入信号vs1 (V)

有效值

波形

输入信号vs2 (V)

有效值

波形

有效值

输出电压vo (V)

峰值

波形

注:上表针对正弦波输入,若是其他信号输入表作相应改变。

3. 减法器(差分放大电路)

减法器(差分放大电路)运算仿真电路

3. 减法器(差分放大电路)

减法器(差分放大电路)运算仿真电路

3. 减法器(差分放大电路)

将实验数据及波形填入下述表格中:

输入信号vs1 (V)

有效值

波形

输入信号vs2 (V)

ቤተ መጻሕፍቲ ባይዱ

有效值

波形

有效值

输出电压vo (V)

峰值

波形

注:上表针对正弦波输入,若是其他信号输入表作相应改变。

vs波形

运放加减电路

运放加减电路(模电实验与设计之二)学院:计算机与电子信息学院专业:00000000000 班级:000班 学号:000000000 姓名:0000一、实验目的:1、掌握集成运算放大器在线性工作条件下的使用特点;2、掌握深度负反馈条件下的虚短、虚断现象;3、掌握加法器和减法器的电路构成和特点。

二、实验主要设备和元件:万用表,双路直流稳压电源。

运算放大器:OP07 2片 电位器: RW1 10k RW2 10k RW3 10k 电阻:1K 510 3K三、实验主要任务:1、根据电路原理图,制作一个运放加减电路。

制作时,注意留出测试端口或端子,注意电位器的摆放要便于调试。

可以考虑用IC 插座,以防止不过关的焊接技术对集成运放的损害。

OP07集成运放的5脚无用,1脚和8脚在本实验中不用接。

在制作电路时,这三个脚悬空即可。

2、本实验所用的直流电源电压在9V ±到15V ±的范围内皆可,根据情况自行选择。

3、分别调节三个电位器,让133i V u V -≤≤,233i V u V -≤≤,333i V u V -≤≤。

取5个不同的、有代表性的输入组合,测量出该组合下的1o u 、2o u (o u )输出值,编制一个表格将测量结果记录下来。

同时,记录两个运放的两输入端的电位(对地电压)P u 和N u 的测量值,观察“虚短”、“虚地”现象。

在调节输入信号大小时,应该先确定1i u 和 2i u 的大小,最后确定3i u 的大小。

4、在调节电位器选择输入信号大小时,要防止1o u 和2o u 的输出值太接近电源电压。

为什么?思考得出结论后写在实验报告中。

四、实验原理:运放加减电路图第一级运算电路完成加法运算。

该电路由一个反相比例运算放大电路组成,经理论推导,可得输入、输出信号的运算关系为13121211o i i u R u u R R ⎛⎫=-+ ⎪⎝⎭,代入1231R R R k ===Ω的值,可得()112o i i u u u =-+。

模电实验模拟运算放大电路(一)

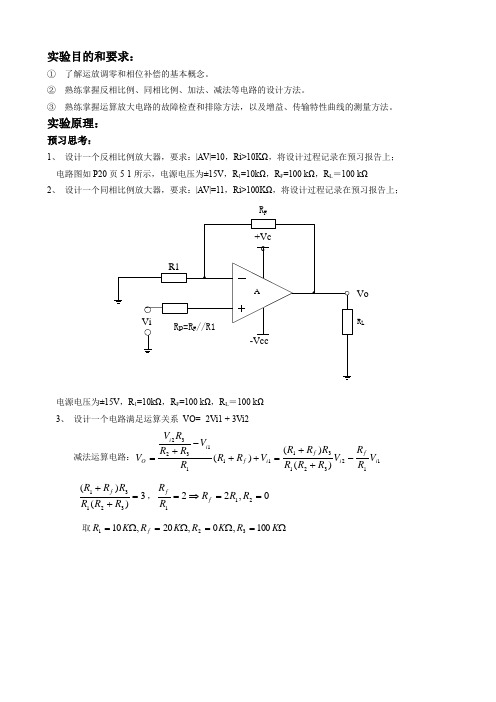

实验目的和要求:① 了解运放调零和相位补偿的基本概念。

② 熟练掌握反相比例、同相比例、加法、减法等电路的设计方法。

③ 熟练掌握运算放大电路的故障检查和排除方法,以及增益、传输特性曲线的测量方法。

实验原理:预习思考:1、 设计一个反相比例放大器,要求:|A V|=10,Ri>10KΩ,将设计过程记录在预习报告上; 电路图如P20页5-1所示,电源电压为±15V ,R 1=10kΩ,R F =100 kΩ,R L =100 kΩ2、 设计一个同相比例放大器,要求:|A V|=11,Ri>100KΩ,将设计过程记录在预习报告上;R F R LVo电源电压为±15V ,R 1=10kΩ,R F =100 kΩ,R L =100 kΩ 3、 设计一个电路满足运算关系 VO= -2Vi1 + 3Vi2减法运算电路:1123213111113232)()()(i f i f i f i i O V R R V R R R R R R V R R R V R R R V V -++=++-+=3)()(32131=++R R R R R R f ,0,22211==⇒=R R R R R f f取Ω=Ω=Ω=Ω=K R K R K R K R f 100,0,20,10321实验电路如实验内容:1、反相输入比例运算电路(I ) 按图连接电路,其中电源电压为±15V ,R 1=10 kΩ, R F =100 kΩ, R L =100 kΩ, R P =10 kΩ//100 kΩAR1R F Rp=R F //R1R LVoVi+Vcc-Vcc输入端接地,用万用表测量并记录输出端电压值,此时测出失调电压0.016 V 分析:失调电压是直流电压,将会直接影响直流放大器的放大精度。

直流信号测量:Vi/V V O /V Avf测量值 理论值 -2 14.25 -7.125 -10 -0.5 4.98 -9.96 -10 0.5 -5.02 -10.04 -10 2-12.87-6.435-10实验结果分析:运算放大器的输出电压摆幅受器件特性的限制,当输入直流信号较大时,经过运放放大后的输出电压如果超过V OM ,则只能输出V OM 的值。

运放的减法电路

PDF pdfFactory

R+ = R2 // R3Βιβλιοθήκη QU − = U +

(可推广的例子)

当两输入端外电路平衡时, R− = R+ ,则 当

Uo =

Rf R2

Ui2 −

Rf R1

Ui2

R1 = R2 = R f

时, 则

U o = U i 2 − U i1

3、加减混合运算电路 特点: 加量从同相端加入 减量从反相端加入 依据:

U− = U+

减法运算电路

在满足

R1 = R2 Uo = Rf R1

[U i 2 − U i1 ]

R3 = R f

方法一:依据法则列出

I1 = I f

分别求出 U − = ?

根据 U − = U +

I 2 = I3

方法二:由迭加原理求出 U − 和 U +

U + = ? 得 出 U o 与输入量的关系

U− = U+ =

特点: 由两级运放组成 第一级的输出为第二级的一个输入信号

PDF pdfFactory

R R U o1 = − f 1 U i1 + f 1 U i 2 = U i 4 R2 R1 R R R R R R U o = − f 2 U i 3 + f 2 U i 4 = − f 2 U i 3 + f 2 f 1 U i1 + f 2 U i 2 R4 R3 R4 R1 R2 R3

Rf R1 + R f

U i1 +

U R1 U U o = R − i1 + o R1 + R f R1 R f

减法电路在运放恒流源电路中的应用

图1 恒流源电路图

2.硬件电路设计与软件设计 2.1 恒流源电路设计

恒流源电路图如图1所示: 在此电路中为了能够精准控制输出 电流,使用运算放大器作为反馈,接三 极管TIP142,输出电流为:

(1) GY,DY外接负载。加运放的恒流源电 路,具备精度高,可调节性,并且原件普 遍易与搭建和调试,因此带运放的恒流源

时,输出端电压:

(4) 2.3 其他电路

除减法电路外,恒流源电路还包括通信电路,A/D转换

电路,D/A转换电路等。D/A转换电路用于控制恒流源的电流

输出,由图3所示,恒流源电路为压控恒流源电路。

恒流源的精度因此由D/A电路决定,D/A芯片的准确级决

定了恒流源的步进。

3.软件设计 软件部分包括通信模块,显示模块,控制模块,运算模块。其中,

代入式(3)和(4),最终通过迭代输出复原图像。

4 实验结果与分析 对比实验结果图3中(h)、(i)和(e)、(f),采用基于暗通道去模糊

复原的图像相较于采用基于贝叶斯去模糊复原的图像,能被检测出 更多显著的边缘细节,且更能抑制振铃效应对边缘检测产生的负面 影响,并在抑制噪声中取得更好的效果。

5 结论 本文研究了图像复原去模糊技术在边缘检测中应用的难点,采

0.2997

0.1

0.8

0.998

0.7984

0.7992

0.1

1.0

0.998

0.998

0.999

0.1

3.0

0.501

1.503

1.501

-0.1

8.0

0.501

4.008

4.012

0.1

10

0.103

1.03

1.033

运放组成的加减乘除等运算电路PPT58页

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——在明眼的跛子肩上。——叔本华

谢谢!

58

运放组成的加减乘除等运算电路

56、死去何所道,托体同山阿。 57、春秋多佳日,登高赋新诗。 58、种豆南山下,草盛豆苗稀。晨兴 理荒秽 ,带月 荷锄归 。道狭 草木长 ,夕露 沾我衣 。衣沾 不足惜 ,但使 愿无违 。 59、相见无杂言,但道桑麻长。 60、迢迢新秋夕,亭亭月将圆。

▪

常用运算放大器16个基本运算电路

5. 微分运算电路

微分运算电路如图 5 所示,

XFG1

R2 15kΩ

C2

22nF

V3

R1

C1

4

12 V

2

1kΩ

22nF

U1A

1

3

T L082CD

8

V2 12 V

XSC1

A +_

B +_

Ext Trig +

_

图5

电路的输出电压为 uo 为:

uo = −R2C1 dui dt

式中, R2C1 为微分电路的时间常数。若选用集成运放的最大输出电压为UOM ,

式中,Auf = 1+ RF / R1 为同相比例放大电路的电压增益。同样要求 Auf 必须小于 3, 电路才能稳定工作,当 f = fo 时,带通滤波器具有最大电压增益 Auo ,其值为:

Auo = Auf / (3 − Auf )

10. 二阶带阻滤波电路

二阶带阻滤波电路如图 10 所示,

C1

1nF R1

_

图 15 全波整流电路是一种对交流整流的电路,能够把交流转换成单一方向电 流,最少由两个整流器合并而成,一个负责正方向,一个负责负方向,最典 型的全波整流电路是由四个二极管组成的整流桥,一般用于电源的整流。 全波整流输出电压的直流成分(较半波)增大,脉动程度减小,但变压器需 要中心抽头、制造麻烦,整流二极管需承受的反向电压高,故一般适用于要 求输出电压不太高的场合。

R1 10kΩ

4 2

12 V

U1A 1

3

8 TL082CD

R3 9kΩ

V2 12 V

D2 1N4148

XSC1

A +_

运算放大器信号运算电路+加法器+减法器等

运算放大器信号运算电路加法器减法器等

在分析运算放大器信号运算电路时,必须掌握运算放大器工作于线性区的特点,运算放大器的开环放大倍数是很高的,一般运放的开环差模增益都大于80dB(即放大倍数以上),所以要使运放工作于线性区必须引入深反馈,以减小两个输入端的净输入电压,也就是说运放工作于线性区时同相输入端于反相输入端的电压接近于零,即,运放工作于线性区的这一特点简称“虚短”,即不是真正短路+ U ≈ − U。

又因运放的输入电阻很高104MΩ ,场效应管作出的运放大于106 MΩ,所以运放两个输入端的电流可视为零,即-I=0,+I=0,这是运放工作于线性区的第二个特点,称为“虚断”。

掌握了运放的这两个特点,分析运算放大器信号运算电路就十分简便。

1、反相比例运算电路:

式中负号表示输出电压于输入电压相位相反。

反相比例运算放大器是电压并联负反馈电路,所以其输出电阻很小,带负载能力强,

图6-6 积分电路输入方波时的输入输出波形

由上式可以看出输出三角波幅值与输入信号的幅值以及周期T 成正比,与时间常数成反比。

积分电路的误差主要是由电容的运放不够理想引起的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

减法运算电路

在满足 21R R = []121i i f o U U R R U -=

f

R R =3 方法一:依据法则列出 f I I =1 分别求出 ?=-U 根据+-=U U 32I I = ?=+U 得 出 o U 与输入量的关系 方法二:由迭加原理求出-U 和+U

⎥⎥⎦⎤⎢⎢⎣⎡+-=+++=-f o i o f i f f

R U R U R U R R R U R R R U 111111 f R R R //1=- 22

2323R U R U R R R U i i ⋅=+=++ 32//R R R =+ +-=U U Θ

11

22R U R R U R R R U i f i f o ⋅-⋅⋅=∴-+ (可推广的例子) 当两输入端外电路平衡时,+-=R R ,则

2122i f i f o U R R U R R U -= 当f R R R ==21时, 则12i i o U U U -=

3、加减混合运算电路

特点: 加量从同相端加入

减量从反相端加入

依据:0==+-i I U U

方法一:依据法则列出方程

f I I I =+21 然后求解??==+-U U 543I I I =+ 寻找出o U 与输入量的关系 方法二:利用迭加原理分别得到+-U U .或直接由推广式得出: ⎥⎦⎤⎢⎣⎡+-⎥⎦⎤⎢⎣⎡+⋅=-+2211443

3R U R U R R U R U R R R U i i f i i f o 特点: 由两级运放组成

第一级的输出为第二级的一个输入信号

42211111i i f i f o U U R R U R R U =⎥⎦⎤⎢⎣⎡+-=

⎥⎦⎤⎢⎣⎡++-=⎥⎦

⎤⎢⎣⎡+-=22211142332442332i f i f f i f i f i f o U R R U R R R R U R R U R R U R R U 可见,加减混合运算亦可由两级反相求和电路来完成。