拉扎维模拟cmos集成电路课件Lecture_17

拉扎维模拟集成电路精讲ppt第一讲mos器件特性分析.

gmb = gm

γ 2 2ΦF +VSB

= ηgm

MOSFET的沟道调制效应

L

L’

L = L - L

1 1 = (1 + VDS ), L L

ID

1 1 L = (1 + ) L L L

VDS

L = L

μnCox W = (VGS - VTH ) 2 (1 + λVDS ) 2L

MOS管深线性区时: CGD=CGS=C1/2+CovW, CGB=0, 沟道屏蔽 MOS管饱和时: CGS= 2C1/3+CovW ,和CGD=CovW, CGB=0, 沟道屏蔽

栅极电阻

MOS 低频小信号模型

VDS 1 1 1 ro = = = = ID ID/ VDS μnCox W (VGS - VTH)2 λ λID 2 L

Ron = 1 W nCox (VGS - VTH ) L

等效为一个 压控电阻

I/V特性的推导(3)

W 1 2 I D = nCox [(VGS - VTH )VDS - VDS ] L 2

三极管区(线性区) 每条曲线在VDS=VGS-VTH时取 最大值,且大小为:

nCox W ID = (VGS - VTH )2 2 L

I D gm = VGS

MOSFET的跨导gm

VDS=const

W = μnCox (VGS - VTH ) L

W g m = 2μቤተ መጻሕፍቲ ባይዱCox ID L 2I D = VGS - VTH

2.3 二级效应

• 体效应 • 沟道长度调制

• 亚阈值导电性

• 电压限制

MOS管的开启电压VT及体效应

《CMOS集成电路基础》课件

智能传感器和可 穿戴设备的普及

随着智能传感器和可穿戴设 备的普及,CMOS集成电路 将在这些领域发挥重要作用 ,实现更高效、更低功耗的 数据采集和处理。

神经网络和类脑 计算的发展

CMOS集成电路将在神经网 络和类脑计算领域发挥重要 作用,推动人工智能技术的 进一步发展。

系统级芯片的广 泛应用

随着系统级芯片的广泛应用 ,CMOS集成电路将与不同 芯片和模块进行集成,实现 更高效、更低功耗的系

晶圆制备

将高纯度硅材料加工成晶圆, 作为集成电路的基底。

薄膜沉积

在晶圆表面沉积所需厚度的薄 膜,形成各种有源和无源器件

。

光刻与刻蚀

通过光刻技术将设计好的电路 版图转移到晶圆表面,然后进

行刻蚀,形成电路图形。

掺杂与退火

通过掺杂工艺在晶圆中引入不 同元素,形成PN结和导电通

道,并进行退火处理。

03

每个逻辑门电路由NMOS和PMOS晶体管组成,形成反相器或与门、或门等基 本逻辑门。

工作原理

01

CMOS集成电路的工作原理基于 NMOS和PMOS晶体管的开关特 性。当输入信号发生变化时, NMOS和PMOS晶体管会交替导

02 通和截止,从而实现逻辑功能。

CMOS电路的电压摆幅较小,因 此功耗较低。此外,CMOS电路 还具有噪声容限高、抗干扰能力 强等优点。

我们应该如何学习和掌握CMOS集成电路技术

理论与实践结合

在学习过程中,应注重理论与实践相结合 ,通过实验和项目实践加深对理论知识的

理解。

持续学习与更新知识

随着技术的不断进步,应保持持续学习的 态度,关注新技术、新工艺的发展,不断 更新自己的知识储备。

培养问题解决能力

模拟CMOS集成电路设计课件

PPT学习交流

6

5

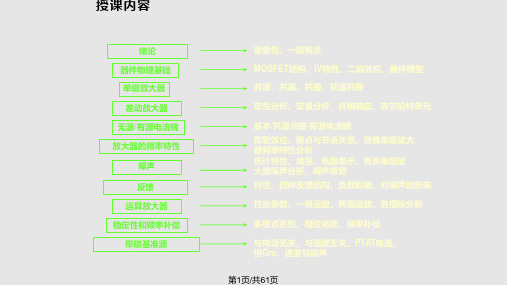

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

模拟cmos集成电路设计拉扎维第1章绪论

总结词

拉扎维模拟方法在CMOS比较器设计中 具有重要作用,可以预测比较器的性能 和行为。

VS

详细描述

CMOS比较器是模拟集成电路中的关键元 件,用于信号的阈值检测和整形。拉扎维 模拟方法可以准确地模拟CMOS比较器的 静态和动态特性,包括响应时间、失调电 压、比较精度等参数,有助于设计者优化 比较器的性能,提高整个电路的稳定性。

应用实例二:模拟CMOS滤波器设计

总结词

利用拉扎维模拟方法,可以高效地设计和优化CMOS滤波器的性能。

详细描述

CMOS滤波器在通信、音频处理等领域有广泛应用。通过拉扎维模拟方法,可以快速设计和优化 CMOS滤波器的性能,包括频率响应、群延迟、线性相位等参数,从而缩短设计周期并提高滤波器的 性能。

应用实例三:模拟CMOS比较器设计

拉扎维模拟方法的优缺点

优点

拉扎维模拟方法基于物理模型,能够精确模拟CMOS集成电路的性能,对于复杂电路和新型器件具有较高的预测 精度。此外,该方法还支持多物理效应和多尺度模拟,能够模拟电路在不同工艺、温度和电压条件下的性能。

缺点

由于拉扎维模拟方法基于物理模型,因此需要较长的计算时间和较大的计算资源,对于大规模电路的模拟可能会 面临性能瓶颈。此外,该方法需要手动设定电路元件的参数,对于不同工艺和不同设计需求需要进行相应的调整 和优化。

04

拉扎维模拟方法的应用实例

应用实例一:模拟CMOS放大器设计

总结词

通过拉扎维模拟方法,可以有效地模拟CMOS放大器的性能,包括增益、带宽、 噪声等参数。

详细描述

CMOS放大器是模拟集成电路中的基本元件,其性能对于整个电路的性能至关 重要。拉扎维模拟方法可以准确地模拟CMOS放大器的直流和交流特性,包括 增益、带宽、噪声等参数,为设计者提供可靠的参考依据。

南邮拉扎维模拟cmos前两章课件

其中, 2qsi Nsub / COX ,称为体效应系数

沟道长度调制效应

描述: 当栅漏之间的电压差增大时,实际的反型沟道长度逐渐减小。

由式

ID

1 2

nCOX

W L

(VGS

VTHΒιβλιοθήκη )2可知,L是

VDS

的函数

,即上述的沟道长度调制效应

若定义 L L L(L 较小)且L / L 和VDS 之间的关系是线性的,则

ID

1 2

nCOX

W L

(VGS

VTH

)2 (1 VDS )

是沟道长度调制系数,表示给定的 VDS 增量所引起的沟道长度的相对变化量

COX W (VGS VTH )

(b) VDS 0

时,源漏存在电压差,因此,

沿沟道x点处的电荷密度为

Qd (x) COX W (VGS VTH V (x))

I D WC OX [VGS VTH V (x)]

ID

WCOX [VGS

VTH

V (x)]n

dV (x) dx

对应的边界条件为 V (0) 0,V (L) VDS ,两边积分得

• 模拟电路对噪声、串扰和其他干扰比数字电路要敏感的多。

• 器件的二级效应对模拟电路的影响比数字电路要严重的多。

• 高性能模拟电路的设计很少能自动完成,而许多数字电路都 是自动综合和布局的。

• 模拟电路的许多效应的建模和仿真仍然存在问题,模拟设计 需要设计者利用经验和直觉来分析仿真结果。

模拟cmos集成电路设计(拉扎维)第2章MOS器件物理基础PPT课件

Q d ( x ) W o ( V x G C V S ( x ) V T )H

西电微电子学院-董刚-模拟集成电路设计

16

I/V特性—推导I(VDS,VGS)

I D W o [ V G x C V S ( x ) V T ] v H

Givv E ea nn E (x d ) d(x V ) dx d(x V )

数字电路设计师一般不需要进入器件内 部,只把它当开关用即可

AIC设计师必须进入器件内部,具备器 件物理知识

❖MOS管是AIC的基本元件 ❖MOS管的电特性与器件内部的物理机制密

切相关,设计时需将两者结合起来考虑

器件级与电路级联系的桥梁?

❖器件的电路模型

西电微电子学院-董刚-模拟集成电路设计

5

本讲

基本概念

I D n C o W L ( x V G V T S ) V D H , V D S 2 S ( V G V T S )

等效为一个线性电阻

RONnCoxW L(V 1GSVTH)

在AIC设计中会用到

西电微电子学院-董刚-模拟集成电路设计

深三极管区

19

I/V特性—当VDS>VGS-VTH时?

与电源无关、与温度无关、PTAT电流、 恒Gm、速度与噪声

西电微电子学院-董刚-模拟集成电路设计

2

上一讲

研究模拟电路的重要性 模拟电路设计的难点 研究AIC的重要性 研究CMOS AIC的重要性 电路设计一般概念

❖抽象级别 ❖健壮性设计 ❖符号

西电微电子学院-董刚-模拟集成电路设计

3

上一讲

数字电路无法完全取代模拟电路,模拟 电路是现代电路系统中必不可少的一部 分

提供载流子的端口为源,收集载流子的端口为漏

CMOS 模拟集成电路课件完整

• SPICE仿真器:

– HSPICE;SPECTRE;PSPICE;ELDO – WinSPICE;Spice OPUS

2020/5/9

23

2.5 SPICE仿真

2020/5/9

24

– 例子: 采用SPICE仿真MOSFET的I/V特性

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

– MOS器件的寄生电容

• CBD和CBS是漏区/源区与衬底之间的PN结耗尽区电 • C2是栅与沟道之间的氧化层电容 • C4是沟道与衬底之间的耗尽层电容,其会随偏压的变化而变化 • C1、C3和C5是多晶硅栅与源区或漏区交叠而产生的交叠电容

2020/5/9

17

等效电容:

D

rD

CBD

CGD

vBD

G CGS

2020/5/9

3

1.1 模拟电路与数字电路

Why Analog Integrated Circuits?

Why CMOS Analog Integrated Circuits?

2020/5/9

4

• 1.2 电路抽象层次

2020/5/9

5

• 1.3 模拟集成电路设计

分析

系统/电路

属性/规范

2020/5/9

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

模拟CMOS集成电路设计(毕查德·拉扎维著,陈贵灿等译,西安交通大学出版社) 绪论课件

模拟CMOS集成电路设计教材n模拟CMOS集成电路设计,毕查德.拉扎维著,陈贵灿等译,西安交通大学出版社参考资料n半导体集成电路,朱正涌,清华大学出版杜n CMOS模拟电路设计(英文),P.E.Allen,D.R.Holberg,电子工业出版社n模拟集成电路的分析与设计,P.R.Gray等著,高等教育出版社半导体集成电路发展历史n1947年BELL实验室发明了世界上第一个点接触式晶体管(Ge NPN)半导体集成电路发展历史n1948年BELL 实验室的肖克利发明结型晶体管n1956年肖克利、布拉顿和巴丁一起荣获诺贝尔物理学奖n50年代晶体管得到大发展(材料由Ge→Si)半导体集成电路发展历史n1958年TI公司基尔比发明第一块简单IC。

n在Ge晶片上集成了12个器件。

n基尔比也因此与赫伯特·克勒默和俄罗斯的泽罗斯·阿尔费罗夫一起荣获2000年度诺贝尔物理学奖。

半导体集成电路发展历史n19世纪60年代美国仙童公司的诺依斯开发出用于IC的平面工艺技术,从而推动了IC制造业的大发展。

半导体集成电路发展历史n60年代TTL、ECL出现并得到广泛应用n1966年MOS LSI发明(集成度高,功耗低)n70年代MOS LSI得到大发展(出现集成化微处理器,存储器)n80年代VLSI出现,使IC进入了崭新的阶段。

n90年代ASIC、ULSI和巨大规模集成GSI等代表更高技术水平的IC 不断涌现,并成为IC应用的主流产品。

n21世纪SOC、纳米器件与电路等领域的研究已展开n展望可望突破一些先前认为的IC发展极限,对集成电路IC的涵义也将有新的诠释。

集成电路用半导体工艺,或薄膜、厚膜工艺(或这些工艺的组合),把电路的有源器件、无源元件及互连布线以相互不可分离的状态制作在半导体或绝缘材料基片上,最后封装在一个管壳内,构成一个完整的、具有特定功能的电路、组件、子系统或系统。

模拟集成电路n1967年国际电工委员会(IEC)正式提出模拟集成电路的概念,它包括了除逻辑集成电路以外的所有半导体集成电路。

CMOS模拟集成电路设计 拉扎维课件

1st 代:MOS1,MOS2,MOS3; 2nd代:BSIM,HSPICE level=28,BSIM2 3rd代:BSIM3,MOS model9,EKV(Enz-Krummenacher-Vittoz)

目前工艺厂家最常提供的MOS SPICE模型为BSIM3v3 (UC Berkeley)

CMOS模拟集成电路设计

绪论、MOS器件物理基础

王永生 Harbin Institute of Technology Microelectronics Center

2009-1-16

提纲

2

提纲

1、绪论 2、MOS器件物理基础

HIT Microelectronics

王永生

2009-1-16

2.3.1体效应

对于NMOS,当VB<VS时,随VB下降,在没反型前, 耗尽区的电荷Qd增加,造成VTH增加,也称为“背栅 效应”

其中,γ为体效应系数

HIT Microelectronics

VTH 0

VTH

王永生

2009-1-16

MOS器件物理基础

15

2.3.2 沟道长度调制效应

当沟道夹断后,当VDS增大时,沟道长度逐渐减小, 即有效沟道长度L’是VDS的函数。

定义L’=L-ΔL, ΔL/L=λVDS

λ为沟道长度调制系数。

HIT Microelectronics

王永生

2009-1-16

MOS器件物理基础

16

2.3.3亚阈值导电性

当VGS≈VTH时和略小于VTH ,“弱”反型层依然存在, 与VGS呈现指数关系。当VDS大于200mV时,

这里ζ>1,VT=kT/q

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Spring 2013

Noise (Ch. 7)

1. Introduction An understanding of noise and its effects on circuit performance is helpful in the development of a good design. Our study pertains to inherent noise sources that are associated with the basic physical charge conduction mechanisms of electrical components. Such forms are thermal, shot, and flicker noise. In contrast to these kinds of noise, interference noise results from various external, unwanted sources, described by such terms as “interference,” “cross talk,” “hum,” “EMI,” and “RFI.” Such noise sources may or may not be random, and they are addressed in design by careful wiring layout, shielding, and other strategies. 2. Terminology A. Power Spectral Density (PSD) The PSD function, S x (f), is a description of the noise power spectrum. S x (f) for a noise waveform x(t) is the average power carried by x(t) in a one-hertz bandwidth about frequency f.

Vn2 = 4kTR ;

f ≥0

(ii) MOSFET thermal noise results primarily in the channel as a result of thermally induced, random motions in charge carriers.

2 In = 4kT γ g m

PSD for white noise

1

EE 510 Lecture 17 Handout B. Spectral Shaping

Spring 2013

Theorem. If a signal with spectrum S X (f) is applied to a linear time-invariant system with transfer function H(s), then the output spectrum is given by SY ( f ) = S X ( f ) H ( f ) Examples of Spectral Shaping:

2 In = 2qI D

C. Flicker Noise Flicker noise is found in active devices and carbon resistors. It occurs only when a DC current exists. At the interface between the gate oxide and the silicon substrate, there appear dangling bonds that give rise to extra energy states. Flicker noise results from charge carriers at the interface being randomly trapped and subsequently released by these energy states. This noise source is more significant in MOSFETs than BJTs.

To illustrate this concept, consider the following CS stage where thermal and flicker noises result in the given output noise voltage.

The total output noise voltage per unit bandwidth is 2 1 2 4kT 2 K Vn2,out = 4kT 3 g m + C WL f g m + R RD ox D

Calculations of input-referred noise voltage (figure a) and noise current (figure b) are illustrated as follows:

7

EE 510 Lecture 17 Handout

Definition for the Gaussian PDF: 1 − (x − m ) 2σ 2

2

p X ( x) =

σ 2π

exp

where m and σ and are the mean and standard deviation of the distribution. D. Correlated and Uncorrelated Sources

K 1 2 2 4kT g m = gm 3 C oxWL f C fC = K 3 gm C oxWL 8kT

5

EE 510 Lecture 17 Handout 4. Circuit Realization of Noise Sources

Spring 2013

Usually, noise sources are referred to the input of a circuit to provide a comparison basis with the level of the input signal.

Vn2 =

K 1 C oxWL f

; K ≈ 10 − 25 V 2 F

The following plot shows the effects of both flicker and spectral noise. The 1/f noise corner frequency (f c ) is a measure of where flicker noise at low frequencies becomes relatively more important than thermal noise.

Spring 2013

Shot noise occurs because of the discrete nature of charge carriers in semiconductors. It is proportional to the semiconductor’s DC bias current. As an example, the white noise spectral current for a diode is described as follows:

Referring this noise voltage to the input is done using the following calculation: Vn2,out Av2 Vn2,out

2 2 gm RD

V

2 n ,in=来自=Vn2,in = 4kT

K 2 1 4kT + + 2 3 g m C oxWL f g m RD

3

EE 510 Lecture 17 Handout 3. Types of Noise

Spring 2013

We consider three different noise sources that are observed in different electrical components. A. Thermal (Johnson, Nyquist) Noise (i) Resistor thermal noise is attributed to the thermally induced, random motions in a conductor, which in turn, give rise to observed voltage fluctuations. This is a form of white noise. Thermal noise circuit representations:

Spring 2013

The amplitude distribution for noise is described by its probability density function, PDF, as follows: P X (x) dx = probability of x < X < x + dx ; X = measured value of x(t) at time t Illustration of the amplitude distribution of noise:

The resistive regions associated with the MOSFET’s gate, source, and drain also display thermal noise, as accounted for in the following model:

4

EE 510 Lecture 17 Handout B. Shot Noise