STM32时钟详细配置

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

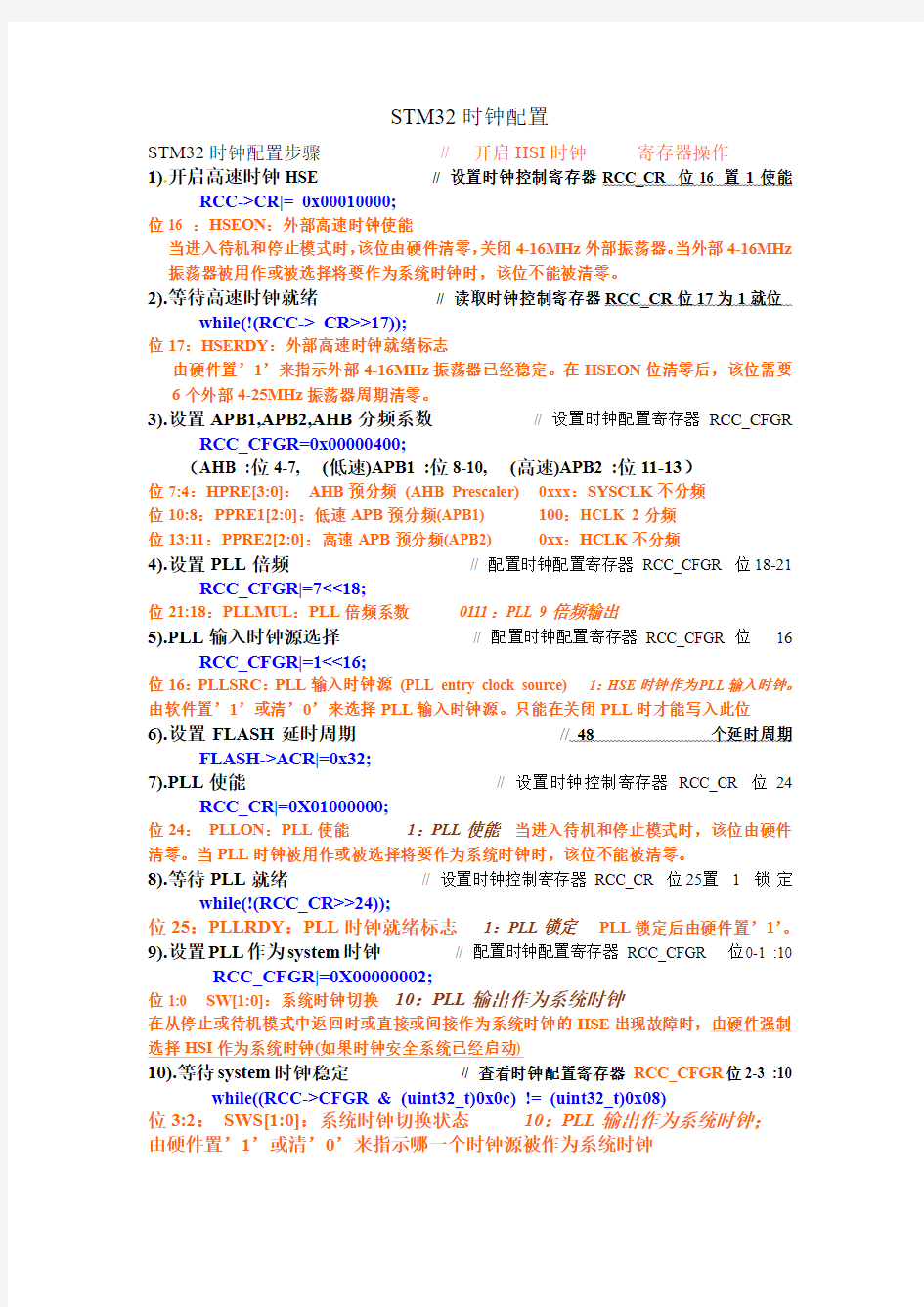

STM32时钟配置

STM32时钟配置步骤// 开启HSI时钟寄存器操作

1).开启高速时钟HSE // 设置时钟控制寄存器RCC_CR 位16 置1使能

RCC->CR|= 0x00010000;

位16 :HSEON:外部高速时钟使能

当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器。当外部4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被清零。

2).等待高速时钟就绪// 读取时钟控制寄存器RCC_CR位17为1就位

while(!(RCC-> CR>>17));

位17:HSERDY:外部高速时钟就绪标志

由硬件置’1’来指示外部4-16MHz振荡器已经稳定。在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零。

3).设置APB1,APB2,AHB分频系数// 设置时钟配置寄存器RCC_CFGR

RCC_CFGR=0x00000400;

(AHB :位4-7, (低速)APB1 :位8-10, (高速)APB2 :位11-13)

位7:4:HPRE[3:0]:AHB预分频(AHB Prescaler)0xxx:SYSCLK不分频

位10:8:PPRE1[2:0]:低速APB预分频(APB1) 100:HCLK 2分频

位13:11:PPRE2[2:0]:高速APB预分频(APB2) 0xx:HCLK不分频

4).设置PLL倍频// 配置时钟配置寄存器RCC_CFGR 位18-21

RCC_CFGR|=7<<18;

位21:18:PLLMUL:PLL倍频系数0111:PLL 9倍频输出

5).PLL输入时钟源选择// 配置时钟配置寄存器RCC_CFGR 位16

RCC_CFGR|=1<<16;

位16:PLLSRC:PLL输入时钟源(PLL entry clock source) 1:HSE时钟作为PLL输入时钟。由软件置’1’或清’0’来选择PLL输入时钟源。只能在关闭PLL时才能写入此位6).设置FLASH延时周期//48 FLASH->ACR|=0x32; 7).PLL使能// 设置时钟控制寄存器RCC_CR 位24 RCC_CR|=0X01000000; 位24:PLLON:PLL使能1:PLL使能当进入待机和停止模式时,该位由硬件清零。当PLL时钟被用作或被选择将要作为系统时钟时,该位不能被清零。 8).等待PLL就绪// 设置时钟控制寄存器RCC_CR 位25置1锁定 while(!(RCC_CR>>24)); 位25:PLLRDY:PLL时钟就绪标志1:PLL锁定PLL锁定后由硬件置’1’。 9).设置PLL作为system时钟// 配置时钟配置寄存器RCC_CFGR 位0-1 :10 RCC_CFGR|=0X00000002; 位1:0 SW[1:0]:系统时钟切换10:PLL输出作为系统时钟 在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择HSI作为系统时钟(如果时钟安全系统已经启动) 10).等待system时钟稳定// 查看时钟配置寄存器RCC_CFGR位2-3 :10 while((RCC->CFGR & (uint32_t)0x0c) != (uint32_t)0x08) 位3:2:SWS[1:0]:系统时钟切换状态10:PLL输出作为系统时钟; 由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟