NIOS性能

基于Nios_II的LCD控制器IP核设计

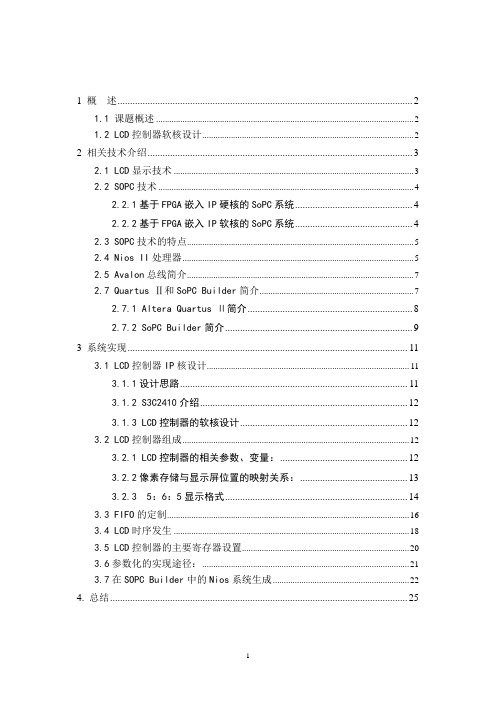

1 概述 (2)1.1 课题概述 (2)1.2 LCD控制器软核设计 (2)2 相关技术介绍 (3)2.1 LCD显示技术 (3)2.2 SOPC技术 (4)2.2.1基于FPGA嵌入IP硬核的SoPC系统 (4)2.2.2基于FPGA嵌入IP软核的SoPC系统 (4)2.3 SOPC技术的特点 (5)2.4 Nios II处理器 (5)2.5 Avalon总线简介 (7)2.7 Quartus Ⅱ和SoPC Builder简介 (7)2.7.1 Altera Quartus Ⅱ简介 (8)2.7.2 SoPC Builder简介 (9)3 系统实现 (11)3.1 LCD控制器IP核设计 (11)3.1.1设计思路 (11)3.1.2 S3C2410介绍 (12)3.1.3 LCD控制器的软核设计 (12)3.2 LCD控制器组成 (12)3.2.1 LCD控制器的相关参数、变量: (12)3.2.2像素存储与显示屏位置的映射关系: (13)3.2.3 5:6:5显示格式 (14)3.3 FIFO的定制 (16)3.4 LCD时序发生 (18)3.5 LCD控制器的主要寄存器设置 (20)3.6参数化的实现途径: (21)3.7在SOPC Builder中的Nios系统生成 (22)4. 总结 (25)1 概述1.1 课题概述本文所要进行描述的设计是运用VHDL语言和Verilog HDL语言,通过分析LCD 控制器的硬件结构和控制时序,使用SoPC技术,把Nios CPU和LCD控制器放在同一个FPGA中。

并通过对相应变量的参数化,实现有一定通用性的LCD IP 核设计。

目的是解决在利用Quartus Ⅱ进行Nios系统开发时,由于内部没有可用LCD的IP,影响产品开发的问题。

1.2 LCD控制器软核设计所要设计的LCD控制器是要求符合Avalon总线规范的。

FPGA中集合了Nios Ⅱ CPU、DMA和LCD控制器模块,以及三态桥(连接Flash)、SDRAM控制器。

基于 Nios Ⅱ的 SOPC 实验教学平台设计

基于Nios Ⅱ的 SOPC 实验教学平台设计陈晓静;吴爱平【摘要】提出了以 EP4CE30F248N FPGA 为核心的 SOPC 实验教学平台设计方案,介绍了平台的硬件组成和软件开发工具,以定时中断为实验案例介绍了 SOPC 实验的具体流程。

该平台由核心板、底板和扩展板组成,可实现的实验项目包括基本模块实验和创新型实验。

其中基本模块实验类似于单片机实验,如定时器、键盘、数码管显示模块等,目的是帮助学生理解 SOPC 系统基本设计方法;创新型实验项目是将 FPGA 并行数据处理和 Nios Ⅱ处理器灵活控制功能相结合的实验,如多通道数据采集、高精度频率计、频谱仪设计等,旨在帮助学生进一步掌握 SOPC系统设计的精髓。

该方案既能实现 SOPC 系统基本模块的实验,又能为电子设计竞赛和实际项目开发提供创新性平台,有助于培养学生的 SOPC 综合设计能力。

【期刊名称】《长江大学学报(自然版)理工卷》【年(卷),期】2016(013)022【总页数】5页(P9-13)【关键词】SOPC;Nios Ⅱ;FPGA;实验教学平台【作者】陈晓静;吴爱平【作者单位】长江大学电子信息学院,湖北荆州434023;长江大学电子信息学院,湖北荆州 434023【正文语种】中文【中图分类】TP368.1SOPC(System On a Programmable Chip)即片上可编程系统,该技术使用FPGA(Field Programmable Gate Array)的逻辑单元以及植入FPGA内部的软核处理器、存储模块和DSP模块,设计出可裁剪、可扩充、可升级的嵌入式处理系统[1]。

该系统不仅具有可编程系统的的灵活性,而且具有高速并行处理数据的能力。

近年来,SOPC技术在数据采集、目标跟踪、电能质量监测等领域得到了广泛的应用[2~4]。

SOPC系统中的处理器通常有硬核和软核2种:硬核是指嵌入在可编程芯片内部的具有固定掩模版图的处理器内核,如ARM内核;软核是指以硬件描述语言文件的形式存在,需经过编译下载,最终固化到可编程芯片内部才可使用的处理器内核,如Altera公司推出的Nios Ⅱ嵌入式软核。

基于PCIExpress总线和NiosⅡ的高速数据传输卡设计

1 P C I E x p r e s s 总 线简介

P C I E总线 是 P C I 总 线 的升 级 版 , 是 I n t e l 公 司 于1 9 9 7年 提 出的计算 机第 三代 总线 , 它彻 底改 变 了 P C I 总线在 系统 带宽 、 传输 速度 等 方 面 的 固有 缺 陷 ,

误 地传输数据。

关键词

P C I E x p r e s s总线

N i o s Ⅱ处理器 文献标志码

高速数据传输

中 图法 分类 号 T N 7 9 ;

A

测试测 量领域 , 上传 或存储 高速大容量数 据

时, 以往 的 U S B 2 . 0 、 以太 网等 方式 显 然 不 能 满 足 高

第1 3卷

第2 5期

2 0 1 3年 9月

科

学

技

术

与

工

程

Vo 1 .1 3 No . 25 Se p.2 01 3

1 6 7 1 — 1 8 1 5( 2 0 1 3) 2 5 — 7 5 2 6 — 0 7

S c i e n c e T e c h n o l o g y a n d E n  ̄ n e e i f n g

( 4 ) P C I E总线 继 承 了 P C I 总线 的优点 , 可完 全

外设 I P 、 N i o s I 1 处 理 器 软 核 以及 A v a l o n交 换 总 线

兼容 P C I 总线 。

等 。图 中 S R A M 控制器 、 三态桥、 U A R T、 定 时 器 以 及大量 通用 寄存 器 等 系统 外设 虽 然 都 是 以 I P核 的 形 式 添加 的 , 但都是通过 F P G A 中 的逻 辑 资 源 来 实

第四章NIOSII外围设备

端口数可 设置

最多32个 I/O端口

7

4.1 并行输入/输出内核

• PIO内核寄存器描述

偏移 量

寄存器名称R/W (n-1)来自…2100

数据寄 存器

读访问 写访问

R 读入输入引脚上的逻辑电平值 W 向PIO输出口写入新值

1

方向寄存器①

R/W

控制每个I/O口的输入输出方向。 0:输入;1:输出。

2

中断屏蔽寄存器 ①

主要介绍: – 硬件结构; – 内核的特性和接口; – SOPC Builder中各内核的配置选项; – 软件编程。

3

本章内容

• 4.1 并行输入/输出(PIO)内核

• 4.2 SDRAM控制器内核

• 4.3 CFI(通用Flash)控制器内核

• 4.4 EPCS控制器内核

• 4.5 定时器内核

• 4.6 UART内核

Nios II 系统

PIO 内核

寄存器

CPU通过寄存 器控制I/O端口 行为

CPU 内核

PIO 内核

PIO 内核

PIO内核结构框图

Pio[7] Pio[6] Pio[5] Pio[4] Pio[3] Pio[2] Pio[1] Pio[0] Pio[31] Pio[30] Pio[29]

Pio[3] Pio[2] Pio[1] Pio[0]

• 复位后,方向寄存器的所有位设置为0,所有的双向I/O口配置 为输入。

10

4.1 并行输入/输出内核

• PIO内核寄存器描述

– 中断屏蔽寄存器:

• 当中断屏蔽寄存器的位设为1时,使能相对应的PIO输入口中 断。

• 中断操作取决于PIO内核的硬件配置,只有配置为输入口时才 能进行中断操作。

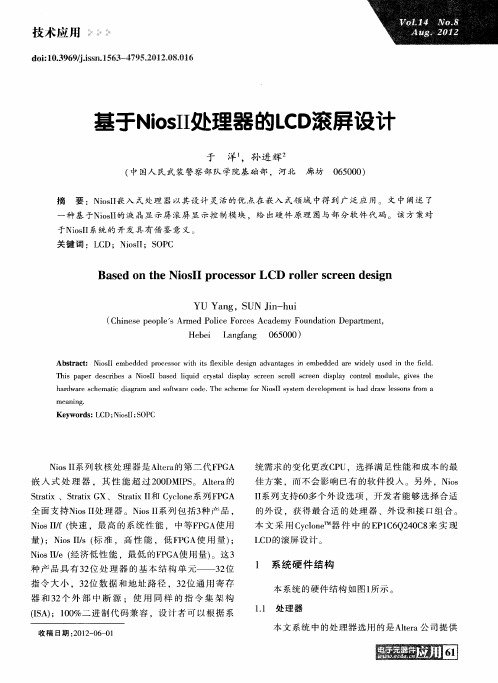

基于NiosⅡ处理器的LCD滚屏设计

收 稿 日期 :01 — 6 O1 2 20一

1 系统 硬 件 结构

本 系统 的硬件 结构 如 图1 所示 。

11 处 理 器 .

本文 系统 中的处 理器选 用 的是 A ea 司提供 hr 公

技 术应 用

s s ck y l

s r e vs es t

图 1 本 系 统 的 硬 件 结 构 图

统 需求 的变 化更改 C U,选 择满 足性 能 和成 本 的最 P 佳 方案 ,而 不会 影 响 已有 的软件 投入 。另 外 ,No is I系列 支持6 多 个外设 选 项 ,开 发者 能够 选择 合适 I 0

全 面 支持 N o 处 理器 。No 系列 包 括 3 产 品 , is I I is I I 种 N o / 快 速 ,最 高 的 系统 性 能 ,中等F G 使 用 is I I f( PA

的C co e系 列 E 1 6 2 0 8 yl n P C Q 4 C 。该 芯 片 采 用2 0脚 4 的P F  ̄Pat u dFa P c ae Q P f ls cQ a lt akg ,塑 料 方 块 平 i

面封 装 )封装 ,提供 15个 I 8 / O接 口。该 芯 片 拥 有

T i p p r d s r e o I b s d i u d c y tl d s ly s r e c ol s r e i ly c nr l mo u e ie h h s a e e c i s a NisI a e l i r sa ip a c e n s r l c e n d s a o t d l ,gv s t e b q p o

基于NiosⅡ的SOPC系统设计与研究的开题报告

基于NiosⅡ的SOPC系统设计与研究的开题报告一、选题背景及意义SOPC(System-on-a-Programmable-Chip,可编程芯片系统)是一种新的系统设计方法,其核心是将CPU、DSP、FPGA等各种数字电路系统的设计集成到一个单一的可编程处理器芯片中,这种设计方法在数字电路领域中具有非常广泛的应用前景和研究价值。

而在这种系统设计方法中,Nios Ⅱ是基于可编程逻辑设备的嵌入式处理器,具有易于设计与控制、可裁剪性强、资源占用小等优点,广泛应用于SOPC系统的设计与实现之中。

因此,本次选题旨在通过对于Nios Ⅱ的SOPC系统设计与研究进行深入探索,探究其在实际应用中的优势与不足之处,为其进一步的优化和完善提供参考依据。

二、研究方法及流程1、资料收集:在本研究中,需要深入了解Nios Ⅱ处理器的内部结构与工作原理、SOPC系统的设计与构建过程、各种数字电路模块的实现方法等相关资料,并进行整理和分析。

2、系统设计:在收集和分析相关资料的基础上,进行简化的Nios Ⅱ处理器设计和SOPC系统架构设计,并利用Quartus II工具进行系统实现和验证。

3、系统测试:完成系统的实现之后,进行系统测试,包括硬件实验和软件编程测试两个方面。

4、分析评估:分析实验数据,评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,提出系统的改进和优化方案。

三、预期结果及意义1、在实验设计过程中,通过对Nios Ⅱ的SOPC系统架构设计与实现,可以深刻理解可编程处理器芯片中各种数字电路模块的工作原理与相互联接关系,彻底掌握SOPC系统的设计与构建方法。

2、通过实验测试和数据分析,可以全面评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,研究其应用前景和推广价值,并针对其不足之处提出系统的改进和优化方案,提高系统的性能水平和可靠性。

3、研究成果可为相关技术研究和应用推广提供科学依据和参考借鉴,促进数字电路领域技术的创新和发展。

40基于NiosⅡ的双核处理器的设计与实现

随着 电子技术 与计算机技 术 的快速发展 ,产 品的新功 能和新特 性 、业 界新标 准 、市 场供求 、用户 对低功 耗甚至 零 功 耗 的 不断 追 求 , 以及产 品成 本 等越 来 越 多 因素 的影 响,使 的市场 上的各种 应用产 品 ,从基础 设备到单 纯 的消 费 电子对 嵌入 式产 品的设计有 了更 高的要求 ,这些 变化 使 研 发人 员开发 更加完 善复杂 的软件 ,在高端 产 品使 用大量 的F G , 同时也将 设计者引 向A I/ O 与非传统硬件模 型一 PA SCSC

中 国西 部科 技 2 0 年1 月 ( 08 1 上旬 ) 7 第3 期总 第1 6 第O 卷 1 5 期

基于No Ⅱ的双核处理器的设计与实现 i s

吕生峰 张 光 健

( 安 建 筑 科 技 大 学 信 控 学 院 , 陕 西 西 安 7 0 5 西 1 5) 0

摘

要 :N s lr公 司开 发的嵌 入 式软 核 处理 器 ,本 文介 绍 了Atr N0J 理 器及 基 于N01 多核 处理 器的工 作原 _】 t a oI e 是A l a .l e s 处 _I s的

( )独立多核处理器 之间是完全独立 的,各处理器不 1 参 与 其他 处 理器 的运 算 。也 可 以说它 们 是 一个 分 开 的系

统 。这种 形式 的双核系 统是… 种非常 简单 的双核系 统 ,只

是 在芯片 系统 中多添加 一个处 理器 ,所 能提 高的系 统性能

有 限。如图i( )。 a

l 多内核简介 多 内核是指在 一个 芯片பைடு நூலகம்内集 成两个 或 多个完整 的计算

~

机 内核 。半导体 工 艺技 术 的飞速 进步 和体 系结构 的不断 发 展 推动处 理器 向多核方 向 的发 展 。微 处理器 的速度 以及单 片 集成度 已经 到 了非 常高 的程 度 ,仅提 高单 核芯片 的速度 会产生过 多热 量且无法 带来相 应的 性能改 善,多核通 过在

EDA

Internal Register File

readrb writerc

8.2 SOPC设计应用 设计应用

SOPC系统设计包括哪些内容:软件设计和硬件设计两个部分,既有软硬件的独立设计,又有软 系统设计包括哪些内容:软件设计和硬件设计两个部分,既有软硬件的独立设计, 系统设计包括哪些内容 硬件协同设计以及系统调试技术。 硬件协同设计以及系统调试技术。 8.2.1 SOPC系统设计流程 系统设计流程 8.2.2 SOPC系统硬件设计 系统硬件设计 8.2.3 SOPC系统软件开发 系统软件开发 8.2.4 NiosⅡ自定义指令逻辑 Ⅱ

8.2.2 SOPC系统硬件设计 系统硬件设计

举例:利用Nios II处理器控制外围 处理器控制外围LED的显示系统设计 举例:利用 处理器控制外围 的显示系统设计 SOPC系统硬件设计包括:QuartusII开发环境下的硬件设计、SOPC Builder开发环境下构建 系统硬件设计包括: 开发环境下的硬件设计、 系统硬件设计包括 开发环境下的硬件设计 开发环境下构建 Nios II嵌入式处理器系统。 嵌入式处理器系统。 嵌入式处理器系统 硬件设计主要完成的工作: 处理器的构建和外围设备接口的设计, 硬件设计主要完成的工作:Nios II处理器的构建和外围设备接口的设计,在Quartus II中完成引 处理器的构建和外围设备接口的设计 中完成引 脚分配、电路综合及下载。 脚分配、电路综合及下载。 目的:熟悉SOPC系统的硬件设计流程和方法。 系统的硬件设计流程和方法。 目的:熟悉 系统的硬件设计流程和方法

Ⅱ处理器 8.1.3 Nios Ⅱ处理器

SOPC的核心:是嵌入式处理器内核。SOPC系统中的嵌入式内核可以使用任意一款软核处理器或 的核心:是嵌入式处理器内核。 的核心 系统中的嵌入式内核可以使用任意一款软核处理器或 硬核处理器,该处理器可以非常复杂而且功能强大,也可以非常简单。 硬核处理器,该处理器可以非常复杂而且功能强大,也可以非常简单。所以人们选择处理器 一般都会考虑相应的硬件和软件开发工具以及该处理器与可编程逻辑器件、 时,一般都会考虑相应的硬件和软件开发工具以及该处理器与可编程逻辑器件、外部设备的 接口能力。 接口能力。 Nios II处理器:是Altera公司的产品,是目前使用较多的一款嵌入式软核处理器,具有可配置性、 处理器: 公司的产品, 处理器 公司的产品 是目前使用较多的一款嵌入式软核处理器,具有可配置性、 成本低、灵活性高的优势。 成本低、灵活性高的优势。 Nios II处理器特性: 处理器特性: 处理器特性 位指令集; (1)32位指令集; ) 位指令集 位数据总线宽度和32位地址空间 (2)32位数据总线宽度和 位地址空间; ) 位数据总线宽度和 位地址空间; 个通用寄存器和32个外部中断源 (3)32个通用寄存器和 个外部中断源; ) 个通用寄存器和 个外部中断源; 乘法器和除法器; (4)32×32乘法器和除法器; ) × 乘法器和除法器 位和128位乘法的专用指令 位乘法的专用指令; (5)可以计算 位和 )可以计算64位和 位乘法的专用指令; (6)单精度浮点运算指令; )单精度浮点运算指令; 的调试逻辑, (7)基于边界扫描测试 )基于边界扫描测试JTAG的调试逻辑,支持硬件断点、数据触发以及片内和片外调试跟踪; 的调试逻辑 支持硬件断点、数据触发以及片内和片外调试跟踪; 个用户自定义指令逻辑; (8)最多支持 )最多支持256个用户自定义指令逻辑; 个用户自定义指令逻辑 万条指令每秒) (9)最高 )最高250DMIPS(25000万条指令每秒)的性能。 ( 万条指令每秒 的性能。

Chirp函数的Nios Ⅱ嵌入式实现

Chirp 函数的Nios Ⅱ嵌入式实现摘要:首先分析Chirp 函数在频域上的一般特性,提出利用FPGA 的嵌入式软核NiosⅡ处理器在嵌入式操作系统μC/OS-Ⅱ上实现Chirp 的方法,即通过NiosⅡ处理器根据Chirp 函数在频域上频率的跳变情况实时改变输出DDS(直接数字合成序列)模块的频率步进控制字的办法,控制DDS 模块的频率输出,实现Chirp 函数所要达到的扫频输出性的目的。

通过在NiosⅡIDE 编程环境中的Console 窗口观察,该设计能很好地实现Chirp 函数功能。

关键词:μC/OS-ⅡSoPC;DDs;FPGA;Chirp 函数0 引言SoC(System on(2hip)是20 世纪90 年代提出的概念,它是将多个功能模块集成在一块硅片上,提高芯片的集成度并减少外设芯片的数量和相互之间在PCB 上的连接,同时系统性能和功能都有很大的提高。

随着FPGA 芯片工艺的不断发展,设计人员在FPGA 中嵌入软核处理器成为可能,Altera 和Xilinx 公司相继推出了SoPC(System on a Programmable Chip)的解决方案,它是指在FPGA 内部嵌入包括(;PtJ 在内得各种IP 组成一个完整系统,在单片FPGA 中实现一个完整地系统功能。

与SoC 相比,SoPC 具有更高的灵活性,FPGA 的可编程特性使之可以根据需要任意定制SoC 系统;与ASIC 相比,SoPC 具有设计周期短,设计成本低的优势,同时开发难度也大大降低。

由于电磁波在传输过程中,经过色散介质如不均匀的波导,高空电离层时会发生色散现象,Chirp 函数在射电天文信号的消色散处理中发挥着重要的作用,研究在FPGA 中实现Chirp 函数是基于FPGA 的射电宇宙信号处理的重要组成部分。

l 系统总体设计图1 为基于FPGA 的射电宇宙信号处理框图。

该设计是基于SoPC 技术设计的Chirp 函数信号发生器,该系统把微处理器。

NIOS系统与计算机串口通信的实现

第 3 卷第 4 4 期

J m a fSo t w o u I o uh

I

e民sf报ni学rcc i ‘ 28 量nr No然.uSndn . ’ A.0 si大0a自eaIe i tvirtl 版 i Eo 族y ii a et 南e U t ‘tN a t s 一 … u0 g

维普资讯

第 4期

李化等:IS系统与计算机 串口通信的实现 NO

85 6

的工作是对应的: 一个发送, 另—个接收 . 为了保证数据通信的可靠性, 要制定通信协议, 然后各 自 根据协议分别编 制程 序 . 约定 通信 协议 如下 : C机 和 NI 都可 以发送 和接 收.上位 机和 下位机 均 采用查 询方 式发 送控 制 字符 现 P OS 和数据、中断方式接收控制字符和数据. 采用 R 22 5 S 3 串1异步通信,位起始位, 位数据位, 位停止位, 1 1 8 1 无奇偶 校验, 波特率 12 0p. 0 bs 每次P 9 c机向单片机发送数据时, 先发送握手信号“x F, 0F" 下位机收到握手信号则发送应答 信号“x E 至 P 0 E ” C机, 上位 P c机收到应答信号后即发送数据.— 当 N O 要向 P I样, 1 S J c机发送数据时, 也先向 P C机 发联络信号“ B 0,C机收到联络信号后发应答信号“ B O ,I S E 9" P E O " O 收到应答信号后则发送数据 了在 N OS1集成开发环境下 串口通信的软件 实现及 上位机上软件的实现. 1 1 关键词: OS 串口通信 NI 中图分类号 :P T 34 l 嵌入式 系统 文献标识码: A

Ni I A T R 公司 2 0 年推出的第二代用于可编程逻辑器件的嵌入式软核处理器, o I是 L E A s 04 具有完善的软件

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

175

Cyclone III LS (3)

EP3CLS70F484C7

135

100

140

Cyclone III (3)

EP3C40F324C6

175

145

215

Cyclone II

EP2C20F484C6

140

110

195

Cyclone

EP1C20F400C6

135

120

175

Arria® II GX

■ Timer

f The MIPS reports were obtained using the MIPS* (*Dhrystones 2.1 benchmark). You can download the Dhrystones 2.1 benchmark software from the Nios II Embedded Processor Design Examples page on the Altera website. For more information about the Dhrystones 2.1 benchmark software, refer to the readme.txt file which is included in the Dhrystones 2.1 benchmark design example.

Table 2. MIPS for Nios II Processor System (Note 1) (Part 1 of 2)

Device Family

Device Used

Nios II/f

Stratix V (1)

5SGXMA3H2F35C2

283

Stratix IV (1)

EP4SGX230HF35C2

305

285

290

HardCopy III (2)

HC322FF1152

230

220

210

HardCopy II

HC230F1020C

200

200

320

HardCopy Stratix

EP1S80F1020C5_HC

150

130

175

Cyclone IV GX

EP4CGX30CF19C6

150

120

Table 1 and Table 2 list the fMAX and millions of instructions per second (MIPS) for a system with the following components:

■ Nios II processor with JTAG debug module

Table 2 lists the value of MIPS for the different types of Nios II processors, while Table 3 lists the ratio of MIPS over the system clock (MIPS/MHz).

Nios II Performance Benchmarks

DS-N28162004-7.0

Data Sheet

Performance Benchmarks Overview

This data sheet lists the performance and logic element (LE) usage for the Nios® II soft processor and peripherals. The Nios II soft processor is configurable and designed for implementation in Altera® FPGAs. The following Nios II processors were used for these benchmarks:

Table 1. fMAX for Nios II Processor System (MHz) (Note 1)

Device Family Stratix® V (2)

Device Used 5SGXMA3H2F35C2

Nios II/f 250

Nios II/s 240

Nios II/e 320

EP2AGX95DF25C4

230

200

270

Arria GX

EP1AGX60CF484C6

140

100

150

Notes to Table 1:

(1) These results were generated using push button Analysis, Synthesis and Fitter settings in the Quartus II software. The results for Stratix V, Stratix IV, Cyclone IV GX, Cyclone III LS, and Arria II GX are generated using Qsys-based designs while other results are generated using SOPC Builder-based designs.

Stratix IV

EP4SGX230HF35C2

230

240

300

Stratix III

EP3SL150F1152C2

290

230

340

Stratix II

EP2S60F1020C3

220

1702Biblioteka 5StratixEP1S80F1020C5

150

130

170

HardCopy® IV (2)

HC4E35FF1152

■ JTAG UART

■ 64 kilobytes (KB) on-chip memory (Cyclone® designs use one megabyte [MB] of off-chip SDR SDRAM)

■ Avalon® Memory-Mapped (Avalon-MM) pipeline bridge

June 2011 Altera Corporation

Subscribe

Page 2

Performance Benchmarks Overview

f The Fast design example illustrates a system that has all the components listed. You can download the Fast design example from the Nios II Embedded Processor Design Examples page on the Altera website. For more information about the Fast design example, refer to the readme.txt file which is included in the Fast design example.

■ Nios II/f—The Nios II/f “fast” processor is designed for high performance while presenting the most configuration options which are unavailable in the other Nios II processors.

101 Innovation Drive San Jose, CA 95134

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.