数值比较器最新版本ppt课件

合集下载

数值比较器

实验五

一:实验目的:1. 掌握常见数值比较器及编码器芯片的逻辑功能及测试方法。

2. 掌握与数值比较器芯片及编码器相关组合逻辑电路设计方法。

二:实验原理:数值比较器功能:完成两个数值大小的比较。

数值比较器分类:

1.1位数值比较器

2.多位数值比较器

编码器功能:将输入的每一个高低电平编成

对应的二进制代码。

常见芯片;

:

实验内容:

1. 病房呼叫系统

医院有一二三四号病房,每个病房设置有呼叫器,护士值班室设有数码管显

示单元。

设计要求:

1.当病房呼叫按钮按下时,值班室数码管显示对应的病房号。

2.病房呼叫优先级为一-二-三-四,从高到低。

电路图如图

结果如下

2.三个四位二进制数排列

利用两个74LS85完成三个四位二进制数的排列,利用数码管显示最大值。

分析;先将四位二进制数A与B进行比较,得出较大得数,再将它与C比较得出较大的数也就是ABC三个四位二进制数中最大的数。

电路图如图所示:

结果如下

:。

【实用】比较器与选择器PPT文档

1.电路构成:由四个异或门和一个或非门组成。

德输州信入息工程学大校欢小迎你比! 较器:可以比较两个数码的大小的比较器。

G是选通信号端,低电平有效; 3.工作原理:Y = 1时,两个数相等; 1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 A1、A2、A3、A4及B1、B2、B3、B4为输入的多个信号,S为旋转开关,P为控制信号――输入选通脉冲。 能够比较两个数码的逻辑电路。 A1、A2、A3、A4及B1、B2、B3、B4为输入的多个信号,S为旋转开关,P为控制信号――输入选通脉冲。 1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 多路选择器功能:与一个单刀多掷开关相似。 适用场合:广泛运用于多输入、单输出的数据传输网络。 G是选通信号端,低电平有效;

2.集成多路选择

数据选择集成电路74LS157的管脚排列图:

功能表:

表15.1.2 功能表来自输入GS

A

B

H

×

×

×

L

L

L

×

L

L

H

×

L

H

×

L

L

H

×

H

输出 Y

L L H L H

G是选通信号端,低电平有效; S是选择信号端,用来选择哪一路信号输出。

谢谢交流!

输入

1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 多路选择器是从多个输入信号中,选择一个并且单个输出的电路。

3.真值表

一位大小比较器真值表

输 Ai 0 0 1 1

入 Bi 0 1 0 1

输 Y1(Ai>Bi)

0 0 1

0

出 Y1(Ai<Bi)

0 1 0

德输州信入息工程学大校欢小迎你比! 较器:可以比较两个数码的大小的比较器。

G是选通信号端,低电平有效; 3.工作原理:Y = 1时,两个数相等; 1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 A1、A2、A3、A4及B1、B2、B3、B4为输入的多个信号,S为旋转开关,P为控制信号――输入选通脉冲。 能够比较两个数码的逻辑电路。 A1、A2、A3、A4及B1、B2、B3、B4为输入的多个信号,S为旋转开关,P为控制信号――输入选通脉冲。 1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 多路选择器功能:与一个单刀多掷开关相似。 适用场合:广泛运用于多输入、单输出的数据传输网络。 G是选通信号端,低电平有效;

2.集成多路选择

数据选择集成电路74LS157的管脚排列图:

功能表:

表15.1.2 功能表来自输入GS

A

B

H

×

×

×

L

L

L

×

L

L

H

×

L

H

×

L

L

H

×

H

输出 Y

L L H L H

G是选通信号端,低电平有效; S是选择信号端,用来选择哪一路信号输出。

谢谢交流!

输入

1.电路构成:(一位二进制数的比较)两个非门和两个与门构成。 多路选择器是从多个输入信号中,选择一个并且单个输出的电路。

3.真值表

一位大小比较器真值表

输 Ai 0 0 1 1

入 Bi 0 1 0 1

输 Y1(Ai>Bi)

0 0 1

0

出 Y1(Ai<Bi)

0 1 0

数据比较器

A3 B3 A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

四位二进制数比较器的真值表

比较输入

输出

A2 B2 ×

A1 B1 ×

A0 B0 ×

A>B 1

A<B 0

×

×

×

0

1

A2>B2

×

×

1

0

A2<B2

×

×

0

1

A2=B2

A1>B1

×

1

0

A2=B2

进行比较,所以对于单元6而言,当 A19~23=B19~23 时,输出端FA>B和FA<B 的输出是0还是1无关紧要的。

A<B

B3 B2 B1 B0 A>B A3 A2 A1 A0 A=B

74LS85 6

FA>B

FA=B

FA<B

总输出

当单元1出现相等情况时,单元6 将自动选择单元2进行比较,并 依次比较下去。最低位单元(单 元5)的接法则不同,它的3个输 出端分别接至单元6的相应的控 制输入端,而控制输入端A>B和 A<B接0,而A=B必须接1,以保 证在A=B时,单元6的FA=B有输出

F A< B

F A =B A>B

74LS85 A < B

A =B

B15 A15 B14 A14 B13 A13 B12 A12

B11 A11 B10 A10 B 9 A 9 B 8 A 8

F A>B F A< B

74LS85

F A =B A>B A< B

A =B “ 1”

B3 A3 B2 A2 B1 A1 B0 A0

三数据选择器比较器全加器

输入数据:D1 D0 ; D3 D2 D1 D0 ;

输出: Y =Di 。 D7 D6 D5 D4D3 D2 D1D0 ;

数据选择器的应用

① 作数据选择,实现多路信号分时传送; ② 级联扩展; ③ 实现组合逻辑函数; ④ 在数据传输时实现并—串转换; ⑤ 产生序列信号。

4选1数据选择器 74LS153

输 W出

信 号

4 选1数据选择器的功能图

数据选择 器类似一 个多பைடு நூலகம்开 关。选择 哪一路信 号由相应 的一组地 址信号控 制。

数据选择器

输 D0

入 数

D1

据 Dn

…

…

Am A0 选择端(地

址信号) 输

Y出

数 据

E 使能端

使能端 E : 控制芯片的工作情况

逻辑 关系

输入

控制端 选择端

(输入地址代码)

42选选11::AA10A0 8选1:A2 A1 A0

序列信号:01101001。

电路图

8/1数据选择器 应用—并入串出

例:用数据选择器2片74LS153(4选1)、 译码芯片74LS247(4-7段译码器)和数码 器管,使电路在任意时刻现实2、0、1、2 四个数字。

电路图

数值比较器—原理

1位数值比较器:

数值比较器—原理

2位数值比较器

多位2进制数进行比较时,如果高位已经比较出〉 或〈,则可直接比较出结果,否则则应进一步比较低位。

设计时采用函数式对照法。地址端 作为输入端,数据输入端可以综合 为一个输入端。

8/1数据选择器 应用—扩展

例:用2片74LS151实现16选1数据选择器①

74LS151实现16选1数据选择器①

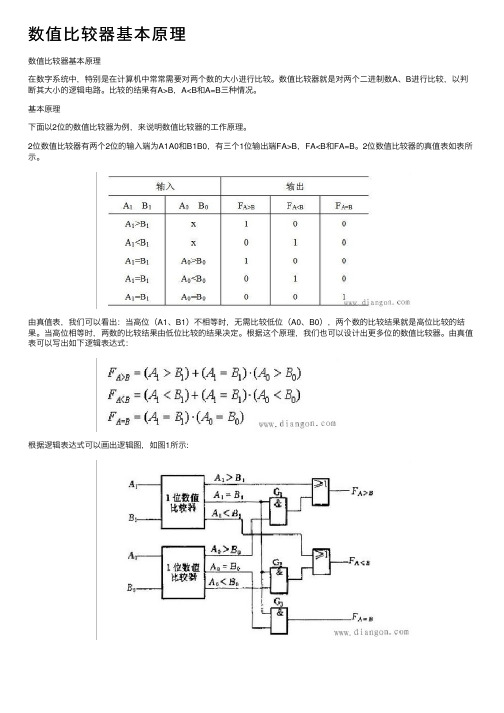

数值比较器基本原理

数值⽐较器基本原理

数值⽐较器基本原理

在数字系统中,特别是在计算机中常常需要对两个数的⼤⼩进⾏⽐较。

数值⽐较器就是对两个⼆进制数A、B进⾏⽐较,以判断其⼤⼩的逻辑电路。

⽐较的结果有A>B,A<B和A=B三种情况。

基本原理

下⾯以2位的数值⽐较器为例,来说明数值⽐较器的⼯作原理。

2位数值⽐较器有两个2位的输⼊端为A1A0和B1B0,有三个1位输出端FA>B,FA<B和FA=B。

2位数值⽐较器的真值表如表所⽰。

由真值表,我们可以看出:当⾼位(A1、B1)不相等时,⽆需⽐较低位(A0、B0),两个数的⽐较结果就是⾼位⽐较的结果。

当⾼位相等时,两数的⽐较结果由低位⽐较的结果决定。

根据这个原理,我们也可以设计出更多位的数值⽐较器。

由真值表可以写出如下逻辑表达式:

根据逻辑表达式可以画出逻辑图,如图1所⽰:。

8数值比较器解析

A’>B’ A’=B’ A’<B’:扩展输入端,级联时低位向高位 的进位位。若A=B时,要由这三位输入来决定比较结果。

2020/2/8

26

输

A3,B3 A2,B2

10

×

01

×

A3 = B3

10

A3 = B3

01

A3 = B3 A2 = B2

A3 = B3 A2 = B2

A3 = B3 A2 = B2

74LS283电路是一个四位加法器电路,可实 现两个四位二进制数的相加,其逻辑符号如图323所示。

2020/2/8

21

图3-23 74LS283电路的逻辑符号

CI是低位的进位, CO是向高位的进位, A3A2A1A0和B3B2B1B0是两个二进制待加数, S3、S2、S1、S0是对应各位的和。

2020/2/8

( An Bn )Cn1 AnBn

2020/2/8

19

Sn An Bn Cn1

由表达式得

Cn ( An Bn )Cn1 AnBn 逻辑图:

仿真

图3-22 全加器

2020/2/8

(a)电路图 (b)逻辑符号

20

3.5.2 多位加法器

全加器可以实现两个一位二进制数的相加, 要实现多位二进制数的相加,可选用多位加法器 电路。

(1)A>B:只有当A=1、B=0时,A>B才为真;

(2)A<B:只有当A=0、B=1时,A<B才为真;

(3)A = B:只有当A=B=0或A=B=1时,A = B才为真。

A

0

0

1

2020/2/8

1

B

YA>B

YA<B

YA=B

2020/2/8

26

输

A3,B3 A2,B2

10

×

01

×

A3 = B3

10

A3 = B3

01

A3 = B3 A2 = B2

A3 = B3 A2 = B2

A3 = B3 A2 = B2

74LS283电路是一个四位加法器电路,可实 现两个四位二进制数的相加,其逻辑符号如图323所示。

2020/2/8

21

图3-23 74LS283电路的逻辑符号

CI是低位的进位, CO是向高位的进位, A3A2A1A0和B3B2B1B0是两个二进制待加数, S3、S2、S1、S0是对应各位的和。

2020/2/8

( An Bn )Cn1 AnBn

2020/2/8

19

Sn An Bn Cn1

由表达式得

Cn ( An Bn )Cn1 AnBn 逻辑图:

仿真

图3-22 全加器

2020/2/8

(a)电路图 (b)逻辑符号

20

3.5.2 多位加法器

全加器可以实现两个一位二进制数的相加, 要实现多位二进制数的相加,可选用多位加法器 电路。

(1)A>B:只有当A=1、B=0时,A>B才为真;

(2)A<B:只有当A=0、B=1时,A<B才为真;

(3)A = B:只有当A=B=0或A=B=1时,A = B才为真。

A

0

0

1

2020/2/8

1

B

YA>B

YA<B

YA=B

比较器的应用(问题).ppt

2019/3/22

返回目录

常见问题

1、比较器74LS85的管脚是如何排列的? 答:如图所示:

Vcc A3 B2 A2 A1 B1 A0 B0

16 15 14 13 12 11 10 1 2 3 4 5 6 7 9 8

B3 A<B A=B A>B A>B A=B A<B GND

2019/3/22

2019/3/22

返回目录

实验原理

(1)比较器原理 比较器对两组同样位数的二进制数进行数值比较。有等值比较 器和量值比较器两类,等值比较器只检验两数是否相等,量值比 较器不但要检验两数是否相等,还要判断出它们的大小。按数据 的传输方式,又有串行比较器和并行比较器之分。 现以具有控制输入端的四位量值比较器74LS85为例加以说明,它 有8个数码输入端(A0~A3,B0~B3),三个控制输入端(a>b) (a<b)(a=b)和三个控制输出端( A>B)(A<B)和( A=B)。 四位量值比较器74LS85以并行方式对二进制码和BCD码进行直接 比较,比较时先比较两组输入数据的最高位,如不等则输出比较 结果,如相等则再比较下一位,依次类推,直至最低位,这样的 比较可以提高比较速度。 对于两组四位字,比较结果直接在三个输出端输出,而较长的字, 则可将比较器级联起来进行比较。级联时,将低位比较器的三个 输出端接到高位比较器的控制输入端,而低位比较器的控制输入 端(a=b)必须接高电平;(a>b)和(a<b)必须接低电平。这样 的级联方式,要经过两级门延迟时间来完成长字的比较,还有另 一种能进一步降低比较时间的级联方式,并联方式。 返回目录

2019/3/22

(2)电子锁原理 利用比较器可以做一个有趣的电子锁实验, 将两个比较器串联,形成一个八位比较器,并假 设A组的8个输入为开锁的钥匙,B组的8个输入为 电子锁的密码。输入A组数据,与B组数据(密码) 做比较,如果A组等于B组,发光二极管发光并开 锁;如果A组不等于B组,则蜂鸣器报警,表示有 危险情况。我们可以利用两片四位比较器,将其 串联起来完成一个8位电子锁, 在电路中, A=B 的输出端驱动发光二极管, A>B 和 A<B的输出端接一个或门,只要有其中一种情况发 生,或门就输出高电平。

返回目录

常见问题

1、比较器74LS85的管脚是如何排列的? 答:如图所示:

Vcc A3 B2 A2 A1 B1 A0 B0

16 15 14 13 12 11 10 1 2 3 4 5 6 7 9 8

B3 A<B A=B A>B A>B A=B A<B GND

2019/3/22

2019/3/22

返回目录

实验原理

(1)比较器原理 比较器对两组同样位数的二进制数进行数值比较。有等值比较 器和量值比较器两类,等值比较器只检验两数是否相等,量值比 较器不但要检验两数是否相等,还要判断出它们的大小。按数据 的传输方式,又有串行比较器和并行比较器之分。 现以具有控制输入端的四位量值比较器74LS85为例加以说明,它 有8个数码输入端(A0~A3,B0~B3),三个控制输入端(a>b) (a<b)(a=b)和三个控制输出端( A>B)(A<B)和( A=B)。 四位量值比较器74LS85以并行方式对二进制码和BCD码进行直接 比较,比较时先比较两组输入数据的最高位,如不等则输出比较 结果,如相等则再比较下一位,依次类推,直至最低位,这样的 比较可以提高比较速度。 对于两组四位字,比较结果直接在三个输出端输出,而较长的字, 则可将比较器级联起来进行比较。级联时,将低位比较器的三个 输出端接到高位比较器的控制输入端,而低位比较器的控制输入 端(a=b)必须接高电平;(a>b)和(a<b)必须接低电平。这样 的级联方式,要经过两级门延迟时间来完成长字的比较,还有另 一种能进一步降低比较时间的级联方式,并联方式。 返回目录

2019/3/22

(2)电子锁原理 利用比较器可以做一个有趣的电子锁实验, 将两个比较器串联,形成一个八位比较器,并假 设A组的8个输入为开锁的钥匙,B组的8个输入为 电子锁的密码。输入A组数据,与B组数据(密码) 做比较,如果A组等于B组,发光二极管发光并开 锁;如果A组不等于B组,则蜂鸣器报警,表示有 危险情况。我们可以利用两片四位比较器,将其 串联起来完成一个8位电子锁, 在电路中, A=B 的输出端驱动发光二极管, A>B 和 A<B的输出端接一个或门,只要有其中一种情况发 生,或门就输出高电平。

数据对比模板PPT课件

logologologologoxxxx项目展示项目展示xxxx公司公司logologoxxxx项目展示项目展示xxxx公司公司添加标题添加标题添加标题添加标题添加标题添加标题素材天下网sucaitianxiacomppt模板免费下载无需注册logologoxxxx项目展示项目展示xxxx公司公司添加文本添加文本添加文本添加文本添加文本添加文本logologoxxxx项目展示项目展示xxxx公司公司添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本添加文本logologoxxxx项目展示项目展示xxxx公司公司aaccddeeffbb10010040401010303080805050logologoxxxx项目展示项目展示xxxx公司公司logologoxxxx项目展示项目展示xxxx公司公司strengthsstrengths优势优势logologoxxxx项目展示项目展示xxxx公司公司weaknessesweaknesses劣势劣势缺乏具有竞争意义的技能技术缺乏有竞争力的有形资产无形资产人力资源组织资产关键领域里的竞争能力正在丧失logologoxxxx项目展示项目展示xxxx公司公司素材天下网sucaitianxiacomppt模板免费下载无需注册10logologoxxxx项目展示项目展示xxxx公司公司11logologoxxxx项目展示项目展示xxxx公司公司12logologoxxxx项目展示项目展示xxxx公司公司13logologo适用抽象商务类适用抽象商务类14

LOGO

点击添加标题

.

1

目

录

XX项目展示

.

LOGO

2

XX公司

列表页

素材天下网 [PPT模板免费下载无需注册]

LOGO

点击添加标题

.

1

目

录

XX项目展示

.

LOGO

2

XX公司

列表页

素材天下网 [PPT模板免费下载无需注册]

4-5-三-数据选择器比较器全加器

Y AB AC ABC ABC AB(C C ) AC ( B B) ABC ABC ABC ABC ABC ABC ABC ABC 1 A B C 0 A B C 0 A BC 0 A BC 1 AB C 1 AB C 1 ABC 1 ABC

i 0 2n 1

1

0 0 0 0

X

0 0 1 1

X

0 1 0 1

0

D0 D1 D2 D3

一般Di可以当做一个变量处理:

可以取原变量;反变量;0;1。

(Di=1时,对应的最小项在式中出现)

设计步骤

(1)确定应该选用的数据选择器:

n:地址变量个数

) n k;(或n k 1

k:函数的变量个数

Y AB AC ABC ABC 1 A B C 0 A B C 0 A BC 0 A BC 1 AB C 1 AB C 1 ABC 1 ABC

比较上面两式,令: A2=A,A1=B, A0=C,D1=D2=D3=0, D0=D4=D5=D6=D7=1

可用真值表来理解(p95表3-17),请列出真值表。

同理,可用5片4选1连接后扩为16选1,请同学们自行分析要 求扩充的输入端更多时,例如4选1扩为32选1,或64选1, 甚至更多时,则显然能显示出用译码器作片选功能的优越 性。

8选1数据选择器 74LS151

逻辑图 功能表

选择端

输出端 数据输入端

变换

F A( BC ) A( BC ) A( BC ) 1 BC ) (

与四选一选择器输出的逻辑式比较

可以令:

【优】比较器与选择器最全PPT

2.逻辑函数式:

Y A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0

3.工作原理:Y = 1时,两个数相等;Y = 0时,两数不等。

二、大小比较器

1.电路构成:(一位二进制数的比较)两个非门和两个 与门构成。

2. 逻辑功能:

当 A i B i,Y 1 A iB i 1 ,Y 2 B iA i 0 当 A i B i,Y 1 A iB i 0 ,Y 2 B iA i 1

个输出的电路。

1.4选1选择器 能够比较两个数码的逻辑电路。

Y = 0时,两数不等。

A 、A 、A 、A 及B 、B 、B 、B 为输入的多个信号,S G数是据选选通择信集号成端电,路低74电LS平1有57效的;管脚排列图:

适1.用电场路合构:成广:泛由运1四用个于异多或输2门入和、一单个输3或出非的门数组据4成传。输网络1。 2

当 Ai Bi,Y1Y20

3.真值表

一位大小比较器真值表

输 Ai 0 0 1 1

入 Bi 0 1 0 1

输 Y1(Ai>Bi)

0 0 1

0

出 Y1(Ai<Bi)

0 1 0

0

4.多位数码的比较

可采用逐位比较法,首先从最高位开始,依次比出结果。

5.1.2 多路选择器 多路选择器是从多个输入信号中,选择一个并且单

G是选通信号端,低电平有效;

入、单输出的数据传输网络。

也叫数据选择器。

2.集成多路选择

数据选择集成电路74LS157的管脚排列图:

功能表:

表15.1.2 功能表

输入

G

S

Байду номын сангаас

A

B

H

Y A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0

3.工作原理:Y = 1时,两个数相等;Y = 0时,两数不等。

二、大小比较器

1.电路构成:(一位二进制数的比较)两个非门和两个 与门构成。

2. 逻辑功能:

当 A i B i,Y 1 A iB i 1 ,Y 2 B iA i 0 当 A i B i,Y 1 A iB i 0 ,Y 2 B iA i 1

个输出的电路。

1.4选1选择器 能够比较两个数码的逻辑电路。

Y = 0时,两数不等。

A 、A 、A 、A 及B 、B 、B 、B 为输入的多个信号,S G数是据选选通择信集号成端电,路低74电LS平1有57效的;管脚排列图:

适1.用电场路合构:成广:泛由运1四用个于异多或输2门入和、一单个输3或出非的门数组据4成传。输网络1。 2

当 Ai Bi,Y1Y20

3.真值表

一位大小比较器真值表

输 Ai 0 0 1 1

入 Bi 0 1 0 1

输 Y1(Ai>Bi)

0 0 1

0

出 Y1(Ai<Bi)

0 1 0

0

4.多位数码的比较

可采用逐位比较法,首先从最高位开始,依次比出结果。

5.1.2 多路选择器 多路选择器是从多个输入信号中,选择一个并且单

G是选通信号端,低电平有效;

入、单输出的数据传输网络。

也叫数据选择器。

2.集成多路选择

数据选择集成电路74LS157的管脚排列图:

功能表:

表15.1.2 功能表

输入

G

S

Байду номын сангаас

A

B

H