存储器阵列

DELL服务器磁盘阵列的扩容

DELL服务器磁盘阵列的扩容

Dell服务器磁盘阵列的扩容最为有效的方式是添加新的磁盘到磁盘

阵列中,从而减少服务器中的存储空间,提高性能,并为未来的存储需求

提供更多的灵活性和灵活性。

在扩容Dell服务器磁盘阵列之前,建议客

户在熟悉Dell服务器磁盘阵列的功能和结构之前,需要考虑到以下几点:

1、首先需要了解磁盘阵列的结构,以及与其他硬件设备之间的关系。

Dell服务器磁盘阵列可以分为单容量阵列和可变容量阵列,需要知道每

种磁盘阵列可以容纳多少磁盘。

2、要考虑服务器的性能,检查磁盘阵列的性能,查看是否支持RAID。

RAID可以提高服务器的存储性能和可靠性,并可以帮助恢复数据。

3、确定扩容的硬件需求,可以是添加磁盘阵列,添加控制器,可以

是添加硬件RAID卡,也可以是添加RAID软件,这些因素影响硬件扩容的

成功率,最终的硬件扩容计划将包含所有这些因素。

4、开始准备扩容操作之前,需要获得正确的软件驱动程序和工具,

例如PEAKFinder,它可以帮助用户检测硬件,将其映射到实际的硬件驱

动程序,从而提供稳定的性能。

5、确保软件驱动程序和工具已经正确安装。

存储器那点事(一)常见存储器分类

存储器那点事(一)常见存储器分类前言注:本文中所谈到的存储器主要是指磁盘阵列,通过SAN/NAS/iSCSI等接口与主机相连,虽然说SAN交换机、物理带库、磁带机和光盘塔也属于存储的范畴,但不在本文讨论范围内。

存储器,或者称作存储阵列,是当今业界一个比较Fashion的词,见过不少这个圈子里的公司为了提高档次,会主动往存储行业靠,经常自我标榜“哥所在的系统集成公司是高科技,不仅搬箱子,哥还做存储”,“哥公司自己生产具有完全知识产权的存储器”…(当然现在再这么说有点out了,现在流行自我标榜“哥公司现在做云计算高科技呢”)。

当然,这个圈子里面的人在和身边朋友自我介绍是做存储这个高科技行业时,也经常碰到另外一种情况,“哥们你们那边250G的盘多少钱一块啊,你们卖U盘么?”…那么存储器究竟该如何定义呢?在我看来,二十多年前Sun公司提出了“网络就是计算机”的理念,对于整个IT行业发生了翻天覆地的变化,那么我们也完全可以说“存储也是计算机”。

存储是什么呢,对,存储也是计算机。

2000年前的存储器,多是作为主机的附属品出现的,记得97年本人在做系统管理员时,看到厂商在调试几套HP 9000和SUN小型机,几个集成商的工程师将一个个磁盘塞进一个独立架子里面(后来才知道那叫磁盘柜),一边塞进去还一边说:“哥们千万注意啊,这玩意叫磁盘阵列,贼贵,一块磁盘顶一台夏利呢”。

我们当时大吃一惊,高科技啊,一块小铁片竟然顶得上大街上一辆出租车(其实当时也不过是给个JBOD+软件RAID,现在想想,真叫暴利啊)…而且当时安装磁盘阵列也是看起来很高深的一件事情,不同于主机UNIX操作系统要插入光盘,输入命令、不断回车,磁盘阵列的安装往往是在主机安装完后再导入一些软件,然后运行一个脚本,出去吃个饭、抽根烟….就完成了。

这就是早期DAS阶段的典型工作流程,存储器在当时仅仅是服务器的附属品。

2000年左右以后,国内的存储器市场慢慢进入了一个繁荣发展阶段,具有独立控制器的磁盘阵列产品越来越多(不再依赖于主机端的软件RAID技术);另外除了IBM/HP/SUN/Compaq/SGI五大UNIX厂商有自己的存储器产品外,独立存储厂商在国内也如雨后春笋般出现了,EMC(第一次还以为是那个做显示器的厂商)、Brocade、Netapp、MCData、HDS等存储网络产品公司也慢慢地出现在招标书和投标现场,可以说,2000年以后,存储器进入了一个快速发展的时期。

IBM储存(磁盘阵列柜)基础知识培训

5

磁盘阵列柜的应用

由于磁盘阵列柜具有数据存储速度快、存储容量大等优点,所以磁盘阵列柜通 常比较适合在企业内部的中小型中央集群网存储区域进行海量数据存储。

6

存储网络的架构

企业存储技术发展日新月异,早期大型服务器的DAS 技术( Direct Attached Storage,直接附加存储,又称直连存储),后 来为了提高存储空间的利用及管理安装上的效率,因而有了SAN( Storage Area Network,存储局域网络)技术的诞生,SAN 可 说是DAS 网络化发展趋势下的产物。早先的SAN 采用的是光纤通 道(FC,Fiber Channel)技术,所以在iSCSI出现以前,SAN 多半 单指FC 而言。一直到iSCSI 问世,为了方便区别,业界才分别以 FC-SAN和IP-SAN。 NAS(Network Attached Storage:网络附 属存储)是一种将分布、独立的数据整合为大型、集中化管理的数 据中心,以便于对不同主机和应用服务器进行访问的技术。

2

基本配置 Server

HBA

Fibre Channel SCSI Chip Controller

RAID sub-system

SCSI Chip Controller Ethernet to Client workstations Dual Controller RAID with only one controller in use (B not used in this example). This RAID system has four SCSI buses with five drives on each bus.

14

SAN的组成

SAN由服务器,后端存储系统,SAN连接设备组成;

3.2 SRAM存储器

A11 A10 A9 A8 A0 片选 译码

8根数据线

CS0

CS1

CS2

CS3

D7

D0 WE

... ..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

..

1K×4

……

2. 存储器与 CPU 的连接

(1) 地址线的连接 (2) 数据线的连接 (3) 读/写线的连接

3.2 SRAM存储器

• 主存(内部存储器)是半导体存储器。根 据信息存储的机理不同可以分为两类:

– 静态读写存储器(SRAM):存取速度快,存储 容量小 – 动态读写存储器(DRAM):存储容量大,存取 速度慢。

3.2 SRAM存储器

一、基本的静态存储元阵列(64×4位) 1、存储位元 2、三组信号线

00000H 32KB ROM 96KB RAM 07FFFH 08000H

1FFFFH

(2)由题知:ROM区的容量为32KB, RAM区 的容量为96KB,利用32KB×8位RAM芯片和 32KB×4位ROM芯片,设计128KB×8位存储 器,需要RAM芯片:96/32=3(片);需要 ROM芯片:8/4=2(片)。 其中,两片ROM芯片串联后,与3片RAM 芯片并联。17条地址线中,15条低位地址线 连接到芯片,2位高位地址线利用2:4译码器 生成片选信号。存储器与CPU连接的示意图 如下:

• 分散式刷新:把一个存储系统周期tc分为两半,周 期前半段时间tm用来读/写操作或维持信息,周期后 半段时间tr作为刷新操作时间。这样,每经过128个 系统周期时间,整个存储器便全部刷新一遍。

NANDFlash阵列存储系统中FTL的设计与实现

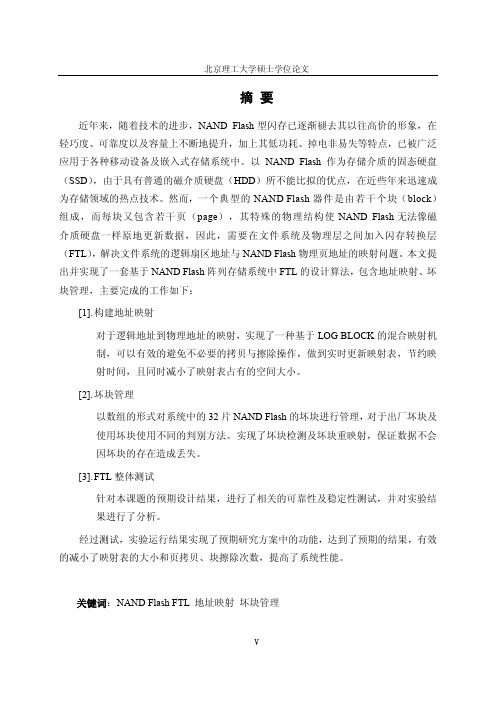

摘要近年来,随着技术的进步,NAND Flash型闪存已逐渐褪去其以往高价的形象,在轻巧度、可靠度以及容量上不断地提升,加上其低功耗、掉电非易失等特点,已被广泛应用于各种移动设备及嵌入式存储系统中。

以NAND Flash作为存储介质的固态硬盘(SSD),由于具有普通的磁介质硬盘(HDD)所不能比拟的优点,在近些年来迅速成为存储领域的热点技术。

然而,一个典型的NAND Flash器件是由若干个块(block)组成,而每块又包含若干页(page),其特殊的物理结构使NAND Flash无法像磁介质硬盘一样原地更新数据,因此,需要在文件系统及物理层之间加入闪存转换层(FTL),解决文件系统的逻辑扇区地址与NAND Flash物理页地址的映射问题。

本文提出并实现了一套基于NAND Flash阵列存储系统中FTL的设计算法,包含地址映射、坏块管理,主要完成的工作如下:[1].构建地址映射对于逻辑地址到物理地址的映射,实现了一种基于LOG BLOCK的混合映射机制,可以有效的避免不必要的拷贝与擦除操作,做到实时更新映射表,节约映射时间,且同时减小了映射表占有的空间大小。

[2].坏块管理以数组的形式对系统中的32片NAND Flash的坏块进行管理,对于出厂坏块及使用坏块使用不同的判别方法。

实现了坏块检测及坏块重映射,保证数据不会因坏块的存在造成丢失。

[3].FTL整体测试针对本课题的预期设计结果,进行了相关的可靠性及稳定性测试,并对实验结果进行了分析。

经过测试,实验运行结果实现了预期研究方案中的功能,达到了预期的结果,有效的减小了映射表的大小和页拷贝、块擦除次数,提高了系统性能。

关键词:NAND Flash FTL 地址映射坏块管理AbstractWith the technological advances, NAND Flash memory has gradually changed its image of costliness in recent years. In the area of weight, reliability and capacity, NAND Flash has upgraded continuously, with its characteristics of low power-consumption and non-volatile, NAND Flash has been widely used in a variety of mobile devices and embedded memory systems. The solid-state drive (SSD), which is a storage system based on NAND Flash, completely eliminates the mechanical defects of the hard disk drive (HDD). Therefore, NAND Flash is rapidly becoming a hot area of storage technology recently. However, a typical NAND Flash device is made up of number of blocks, and each block is made up of number of pages, its unique physical structure enable NAND Flash’s updating operation is different from HDD’s, because NAND Flash need a write should be preceded by an erase operation. So, a flash translation layer (FTL) is introduced to solve the mapping problem between the logical address and physical address. In this paper, the design of FTL in NAND Flash array system includes the following:[1].Mapping schemeTo complete the mapping, a LOG BLOCK-based hybrid mapping scheme is proposed. It can effectively avoid the unnecessary copying and erasing operations, and achieve the real-time updating. The scheme is time-saving and space-saving.[2].Bad block managementIn the form of an array to manage bad blocks, there are different methods to identify the initial and runtime bad blocks. The implementation of the bad blocks re-mapping to ensure that data would not be lost due to bad blocks.[3].The overall test for FTLFor the expecting result of the design, a relevant test of the reliability and stability is carried out, and experimental results are analyzed.All of the experimental results showed that the design of FTL in NAND Flash array system was compact and steady, the mapping scheme implemented in the FTL reduced the size of mapping table, the times of page copy and block erase effectively. It provided well compatibility in the system.Key Words:NAND Flash FTL Address Mapping Bad Block Management目录第1章绪论 (1)1.1 课题来源及意义 (1)1.2 课题相关技术背景 (1)1.2.1 固态硬盘简介及其分类 (1)1.2.2 固态硬盘控制器简介 (3)1.2.3 SSD设计的关键问题 (4)1.3 本文的研究内容与组织结构 (4)第2章NAND Flash阵列存储系统的基本原理 (8)2.1 Flash型存储器简介 (8)2.1.1 NAND Flash与NOR Flash (8)2.1.2 SLC NAND Flash与MLC NAND Flash (10)2.1.3 NAND Flash器件的指令 (12)2.1.4 NAND Flash器件的操作特点 (14)2.1.5 NAND Flash器件的相关参数介绍 (15)2.2 NAND Flash阵列存储系统硬件结构 (17)第3章 NAND Flash阵列存储系统中FTL的设计与实现 (19)3.1 两种典型的设计方法 (19)3.1.1 闪存型文件系统 (19)3.1.2采用FTL结构的文件系统 (20)3.2 FTL的多种算法研究 (21)3.3 NAND Flash阵列存储系统中FTL的设计方法 (26)3.3.1 FTL的设计目标 (26)3.3.2 FTL设计流程 (27)3.4 地址映射的实现 (29)3.4.1 NAND Flash阵列混合地址映射的实现 (29)3.4.2 映射表查找及更新方法 (37)3.5坏块管理表的建立方法 (37)3.5.1 坏块管理流程 (37)3.5.2 初始化坏块检测的实现 (39)3.5.3使用中坏块的辨识与检测 (40)3.5.4坏块查找表与重映射原理 (41)3.6冗余字节的信息存储安排 (41)第4章实验结果分析 (43)4.1 系统兼容性分析 (43)4.2突发状况下保证数据安全方法 (43)4.3 实验测试方案及结果 (44)4.3.1 实验测试方案 (44)4.3.2 坏块管理形式 (44)4.3.3地址映射机制的比较 (45)4.3.4 读写测试及分析 (47)总结 (52)参考文献 (54)致谢 (57)第1章绪论1.1 课题来源及意义NAND Flash,一种非易失性存储介质,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘。

海康威视磁盘阵列使用说明

海康威视磁盘阵列使用说明一.登录1.存储系统默认登录账户为:web_admin 密码为:1232.登录时应以高级模式登录二.设定IP SAN的访问IP管理员可以通过与存储设备相互连通的网络,来设置IP SAN的访问IP。

存储设备分为管理网口和数据网口,可以通过管理网口或者数据网口连接管理PC连接管理网口后,用户可以将用来进行存储管理的设备IP改为同网段的IP,确认网络连接正常后,便可以在IE中输入:https://192.168.10.138:2004来登录IP SAN的管理界面。

一.网络配置下图是系统正常登录后的界面,如图1所示图11.进入系统后,可以首先进入网络管理,在进入网络管理界面后首先要进行网口绑定:点击“绑定管理”按钮,在弹出的界面选择要绑定的网口且绑定模式为“虚拟化”,在点击“创建绑定”并确认绑定成功2.接下来就是“网口管理”,网口管理即就是修改系统IP地址,进入网口管理界面如图2所示:可在此修改系统的访问IP地址图2二.创建RAID1.网络管理之后就是RAID管理,首先要创建阵列,进入“阵列创建”界面,如图3所示图3输入阵列名称,并将阵列类型选为RAID5,然后在可用物理盘中勾选至少3块盘创建阵列,选好后点击“创建阵列”即可。

2.第二步则要进行“阵列重构”,阵列重构是对于已经存在的阵列中,某个物理盘出现不稳定或者出现故障的情况下,为了拯救出故障硬盘中的数据而设定的,从而达到保护数据和恢复阵列的完整性。

但,前提是系统中存在可用的物理盘,并且和出故障的硬盘容量大小相同。

如图4所示图4初始时候阵列自动重构状态默认是关闭的,首先我们要开启自动重构然后输入阵列名称并选择1块可用物理盘,点击“重构阵列”(阵列重构一般是在有故障盘的时候才会用到)3.接下来就要进入“热备盘管理”,热备盘是用来防止阵列中出现掉盘或者磁盘出故障时及时自动化去替换出现故障的硬盘。

其界面如下图5 选择要添加的热备盘点击“添加热备盘”即可图54.之后就是阵列校验,阵列校验的目的是预先防止数据存储过程中出现的错误和长期读写造成的文件丢失,从而达到数据的有效性和完整性。

非易失性存储器讲解

非易失性存储器1. 绪论随机存储器(如 DRAM 和 SRAM 的缺点之一就是掉电后所存储的数据会随之丢失。

为了克服这个问题,人们已设计并开发出了多种非易失或 /且可编程的存储器。

最近,基于浮栅概念的闪存由于其小的单元尺寸和良好的工作性能已经成为最通用的非易失存储器。

因此 , 在本文中,我们将着重介绍 ROM 的两种结构(即 NOR 和 NAND 阵列和闪存的基本结构及其应用。

2. MOS ROM 阵列的两种实现方法2.1 基本 ROM 单元只读存储器阵列可以看做是一种简单的组合布尔逻辑,即它对每个输入组合(地址都会产生一个指定的输出值。

因此, 在一个特定地址存储二进制信息, 可以通过被选行 (字线与被选列 (位线间有无数据路径 (相当于特定位置上有无元件或元件是否在标准电压下导通来实现。

而实现数据路径的基本结构有两种,即 NOR 和NAND 阵列。

图 2.1 ROM 的 1和 0 单元的不同实现方式首先,考虑最简单的单元,如图 2.1(a所示,这是一个基本的 ROM 单元。

假设位线 BL 通过一个电阻接地,没有任何其他的激励或输入。

这就是 0单元中的情况(2.1(a下图。

由于字线 WL 和位线 BL 之间不存在任何实际的连接,所以 BL 的值为低电平而 WL 得值无关。

反之,当把一个高电压 WL V 加在 1单元的字线上时二极管导通,字线被上拉至( WL D on V V ,结果在位线上形成了一个 1。

总之,在 WL 和 BL 之间是否存在一个二极管区分了 ROM 单元中存放的是 1还是 0。

2.2 NOR ROM 结构然而,由于二极管单元的位线与字线是不隔离的,所有需要用来充电位线电容的电流必须通过字线和它的驱动器来提供, 而这些电流这大容量存储器中是非常大的, 因此, 这一1(aDiode ROM (bMOS ROM 1(cMOS ROM 2方法只适用于小存储器。

一个改善隔离的方法是在单元中使用一个有源器件,如图 2.1(b所示, 其工作原理与二极管单元相同,但是它的所有输出驱动电流都是由单元中的 MOS 管提供的, 字线驱动器只负责充电和放电字线电容。

熟悉ROM电路的阵列逻辑图

3.外存储器 外存储器与内存储器相比,存储容量大,可

靠性高,价格低,在脱机情况下可永久保存信息。 但速度较内存储器慢得多,它属外部设备。 主要有:软盘存储器、硬盘、光盘等。

JHR

第二节 只读存储器(ROM) 只读存储器(ROM)中的信息一旦写入,在正常 工作时,只能读出信息而不能修改,其所存信息 在断电后仍能保持,常用于存放固定的信息。 一、功能与结构

存储器的功能:是存放不同程序的操作指令及 各种需要计算、处理的数据,所以它相当于系统存 储信息的仓库。

典型的存储器:由数以千万计的有记忆功能的 存储单元组成,每个存储单元可存放一位二进制数 码和信息。

随着大规模集成电路制作技术的发展,半导体 存储器因其集成度高、体积小、速度快,目前广泛 应用于各种数字系统中。

JHR

[解]由图可知,逻辑函数F1、F2由EPROM矩阵组 成。因此可直接写出输入和输出间的与—或表达式。 即

JHR

F1 XYZ XYZ XYZ XYZ F2 XYZ XYZ XYZ XYZ

由上式看出: 当XYZ=000, 001,100, 101时,F1=1; 当XYZ=011, 101, 110,111时,F2=1。

2. 内存储器(主存储器)

内存储器是数据和代码的临时存放设备,存放 输入/输出数据以及CPU进行计算、处理的数据。

JHR

内存储器可分为RAM(Random Access Memory ,随 机存储器)和ROM(Read Only Memory ,只读存储 器)。目前,内存储器一般为半导体存储器。

(1)随机存储器RAM RAM的特点是可读可写,但关机后存储的信

JHR

[解](1)逻辑函数Y1、Y2由EPROM矩阵实现。 根据EPROM的结构特点,与阵列为固定结构,或 阵列为可编程结构。因此输入和输出间的逻辑关 系可直接写成与—或表达式,输入变量是A、B、 C,直接加在EPROM地址端,输出变量Y1、Y2由 EPROM数据输出端输出。

Dell EMC CX3-Series iSCSI 存储阵列使用 Microsoft Windows

使用 Microsoft ® Windows Server ® 故障转移群集的 Dell|EMC CX3-Series iSCSI 存储阵列 硬件安装与故障排除指南简介群集硬件的布线准备用于群集的系统故障排除iSCSI 配置工作表群集数据表注、注意和警告本说明文件中的信息如有更改,恕不另行通知。

© 2008 Dell Inc. 版权所有,翻印必究。

未经 Dell Inc. 书面许可,严禁以任何形式复制这些材料。

本文中使用的商标;Dell 、DELL 徽标、PowerEdge 、PowerVault 是 Dell Inc 的商标;Active Directory 、Microsoft 、Windows 、Windows Server 、Windows XP 和 Windows NT 是 MicrosoftCorporation 在美国和/或其它国家和地区的商标或注册商标;EMC 、Navisphere 和 PowerPath 是 EMC Corporation 的注册商标,而 Access Logix 、MirrorView 、SAN Copy 和 SnapView 是 EMC 的商标。

本说明文件中述及的其它商标和产品名称是指拥有相应商标和产品名称的公司或其制造的产品。

Dell Inc. 对本公司的商标和产品名称之外的其它商标和产品名称不拥有任何专有权。

2008 年 7 月 Rev. A00注: "注"表示可以帮助您更好地使用计算机的重要信息。

注意: "注意"表示可能会损坏硬件或导致数据丢失,并告诉您如何避免此类问题。

警告: "警告"表示可能会导致财产损失、人身伤害甚至死亡。

返回目录页面群集硬件的布线使用 Microsoft ® Windows Server ® 故障转移群集的 Dell|EMC CX3-Series iSCSI 存储阵列 硬件安装与故障排除指南鼠标、键盘和显示器的布线电源设备的布线公用网络和专用网络的群集布线存储系统的布线鼠标、键盘和显示器的布线在机架中安装群集配置时,必须安装开关盒,以将鼠标、键盘和显示器连接至节点。

宏杉存储阵列安装维护手册

铜川煤炭局煤矿安全监测监控系统升级改造项目存储系统维护手册杭州宏杉科技有限公司目录第一部分实施方案41项目概况41.1软硬件信息41.2拓扑图41.3版本信息51.4产品条码62存储配置62.1设备名称对应表62.2存储IP地址规划62.2.1MacroSAN-162.2.2MacroSAN-262.2.3MacroSAN-372.3权限配置72.4RAID划分72.4.1MacroSAN-172.4.2MacroSAN-292.4.3MacroSAN-3112.5LUN划分132.5.1MacroSAN-1132.5.2MacroSAN-2132.5.3MacroSAN-3132.6LUN分配132.6.1MacroSAN-1132.6.2MacroSAN-2142.6.3MacroSAN-3143iSCSI接入服务器14第二部份用户须知与日常维护151用户须知151.1致命错误:(可能会导致数据丢失等不可挽回后果)151.2严重错误:(可能会导致业务中断等严重后果)152日常维护162.1开机顺序162.1.1启动FC交换机和存储扩展柜162.1.2启动存储控制器162.1.3启动物理服务器172.1.4启动物理服务器上的业务172.2关机顺序172.2.1停止物理服务器上的业务172.2.2关闭物理服务器172.2.3关闭存储控制器172.2.4关闭FC交换机和存储扩展柜193日志查看与收集194备份配置文件205注意21文档说明本手册共分为三个部分:第一部分实施方案:供日后维护时参考使用。

第二部分用户须知与日常维护:列出用户使用注意事项和日常查看日志、收集存储信息及备份配置信息的方法。

第一部分实施方案1项目概况1.1 软硬件信息1.2 拓扑图1.3 版本信息1.4 产品条码2存储配置2.1 设备名称对应表2.2 存储IP地址规划2.2.1 MacroSAN-12.2.2 MacroSAN-22.2.3 MacroSAN-32.3 权限配置GUI用户名:adminGUI密码:admin2.4 RAID划分2.4.1 MacroSAN-12.4.2 MacroSAN-22.4.3 MacroSAN-32.5 LUN划分2.5.1 MacroSAN-12.5.2 MacroSAN-22.5.3 MacroSAN-32.6 LUN分配2.6.1 MacroSAN-12.6.2MacroSAN-22.6.3MacroSAN-32.7 iSCSI接入服务器第二部份用户须知与日常维护1 用户须知尊敬的用户,您好:很高兴您选择了宏杉科技的存储产品,宏杉科技热忱为您服务。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A0

字线

A1

wOO

w01

wlO w11

B

地址译ቤተ መጻሕፍቲ ባይዱ驱动系统

-维和二维地址译码方案 -—维地址译码方案:

-存储体阵列的每一个存储单元由一条字线驱动, 也叫单译码结构.

x 32bit RA

地址

地址有10根

-字线根数需要:210 = 1024根

1024■字 x 32-位

阵列

§32

数据

地址译码驱动系统

Address-4-

4:16 Decoder 1111

字线15

1

____■ 1110 字线14

维

地

址

1

译

码

位

线 L7位

线6 位

11

1 位元

位元

1—

……1位元

线

线1 位;

0

11

1 位元

1~

位元

位元J-

……1 位元

1-

位元

1~

0001 0000

字线1

1

字线0

1

位元J- 位元J位元J- 位元J-

Datay Data6

……1

位元

字线

存储 [ 位元 "P =0 没充过电&

位线

字线 0

存储

充满位电元& -I-

存储器结构

Address—2^

2:4 译码器

11

10

字线3 字线2

01 字线1

00 字线0

位线2

位线1

位线。

地址译码驱动系统

-CPU给出指定存储单元的地址.

-把该地址翻译成访问指定存储单元的控制信号

A0 A0 A1 A1

wo

列线1

H

列线0

□□□ H□

□□□

□H

o巫

Wo 30 H

11

10

01

00

2:4

译码

丫地址译

码

■y地址

存储端口

-所有的存储器都有一个或者多个端口・ -每一个端口提供对一个存储器地址的读/写访问. -前面介绍的都是单端口存储器. -多端口存储器可以同时支持对多个地址的访问.

2个读端口 1个写端口

CLK

SAMSUNG 501 KLHBGIIGENDB0I11

NA1HM00N

存储器阵列位元,字

字线

存储阵列

位线7 位线6 位线5 位线4 位线3 位线2 位线1 位线0

存储“字”

存储器阵列位元,字举例

字线

存储 位元

位线

存储阵列

字线

存储 位元

位线7 位线6 位线5 位线4 位线3 位线2 位线1 位线0

丨

I______________

______________

______________

________Array

M

WE3 41 RD1

A2 RD2

3端口存储:

存储器阵列

地址 译码 驱动 电路

在横向,4条(A6--A9)用在纵向 -则共生成字线条数为:26+24=64+16=80

0

地址译码驱动系统

X2 :

地译 4

址 W1

译

1

码

1

0

0

1

X地址 —2-

0

0

行线3 行线2 行线1

行线。

列线3

列线2

I

□wr □

w Er

I

H□□I□□□□wwr

d

H

00H□□ □

□ 0 □□□ □ □ o

woi

word2

T ■H ■, ■T

存储“字"

存储器阵列位元

字线 =1

存储 位元 没充过电&

位线

=0

u

字线=1

位线

存储 1

位元 -p

充满电&

=1

字线 =0

存储 [ 位元 "P =0 没充过电&

位线

字线 0

存储 位元 充满电

位线 =?

r1

B

存储器阵列位元

字线

存储 位元 没充过电&

位线 二 0

位 字线=1

存储 1

位元 -p =1 充满电&

出/写入M-bit数据值

N

地址

数据

一般存储器阵列 的电路符号

存储器阵列

-二维存储器位元阵列

•每一个位元存储一位数据

-N位地址,M位数据:

-2N 行 and M 列 列数(一行数据位数,字长) 数(字数,容量)

阵列大小

深度x宽度=2N x M

存储器阵列Example

-22 X 3-bit 阵列 -字数:4个 -字长:3-bits -例如,在地址10存储一个3-bit的字100

存储器阵列

-有效存储大量数据的存储器阵列 -3种常见类型:

-DRAM (Dynamic random access memory ) -SRAM (Static random access memory ) -ROM (Read only memory ) -在每一个N-bit地址指定的独特地址空间,读

Address

Address Data 11 0 1 0

01 1|1|O| 深度 00迎▼

Data

B

存储器阵列

地址頌

1024-字 x 32-位

阵列

数据

存储器结构

地址 译码 驱动 电路

存储阵列

I/O 和 R/W 控制电路

数据总线

R/W信号

SAMSUNG 625 K9G8G08U0M

PCBO

FEE86JKX

1-

1

位元

1~

……1 位元

H Dat位ai '元Data。

地址译码驱动系统

: -二维地址译码方案

-从CPU来的地址线分成两部分,分别进入X (横向) 地址译码器和Y (纵向)地址译码器,由二者同时 有效的字线交叉选中一个存储单元。

地址译码驱动系统

-二维地址译码方案:

蜘:1K X 32 位〕 -可以将lKx32bit RAM的10条地址线中6条(A0--A5)用