存储器和阵列结构设计

ROM存储器内涵EPROM2716存储器地介绍

课 堂 教 学 实 施 方 案课 题:只读存储器ROM 、主存储器的设计5.3 只读存储器ROM指在微机系统的在线运行过程中,只能对其进行读操作,而不能进行写操作的一类存储器,在不断发展变化的过程中,ROM 器件也产生了掩模ROM 、PROM 、EPROM 、EEPROM 等各种不同类型。

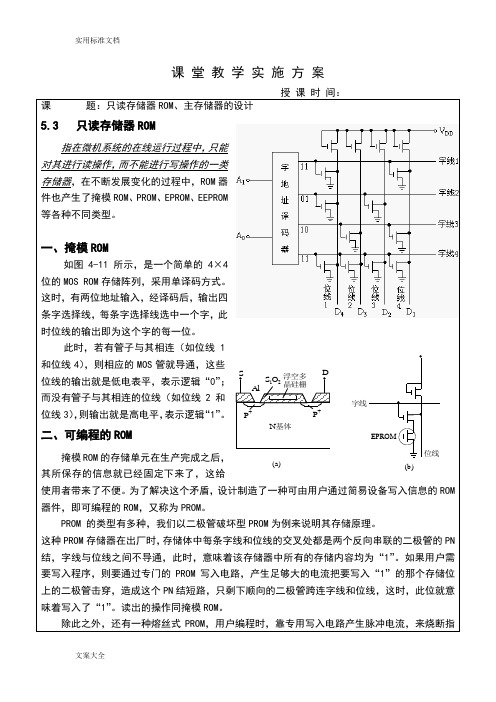

一、掩模ROM如图4-11所示,是一个简单的4×4位的MOS ROM 存储阵列,采用单译码方式。

这时,有两位地址输入,经译码后,输出四条字选择线,每条字选择线选中一个字,此时位线的输出即为这个字的每一位。

此时,若有管子与其相连(如位线1和位线4),则相应的MOS 管就导通,这些位线的输出就是低电表平,表示逻辑“0”;而没有管子与其相连的位线(如位线2和位线3),则输出就是高电平,表示逻辑“1”。

二、可编程的ROM掩模ROM 的存储单元在生产完成之后,其所保存的信息就已经固定下来了,这给使用者带来了不便。

为了解决这个矛盾,设计制造了一种可由用户通过简易设备写入信息的ROM器件,即可编程的ROM ,又称为PROM 。

PROM 的类型有多种,我们以二极管破坏型PROM 为例来说明其存储原理。

这种PROM 存储器在出厂时,存储体中每条字线和位线的交叉处都是两个反向串联的二极管的PN 结,字线与位线之间不导通,此时,意味着该存储器中所有的存储内容均为“1”。

如果用户需要写入程序,则要通过专门的PROM 写入电路,产生足够大的电流把要写入“1”的那个存储位上的二极管击穿,造成这个PN 结短路,只剩下顺向的二极管跨连字线和位线,这时,此位就意味着写入了“1”。

读出的操作同掩模ROM 。

除此之外,还有一种熔丝式PROM ,用户编程时,靠专用写入电路产生脉冲电流,来烧断指P +P +A lS i O 2SD浮空多晶硅栅N 基体字线EPROM(a)(b)位线实用标准文档文案大全。

二维阵列结构设计-概述说明以及解释

二维阵列结构设计-概述说明以及解释1.引言1.1 概述概述二维阵列结构设计是指在平面内按照一定规则排列元素或组件,以实现特定功能或性能的设计过程。

在现代科学技术领域中,二维阵列结构设计被广泛应用于各种领域,如天线阵列、传感器阵列、光电阵列等。

通过合理的设计和优化,可以实现更高效的性能和更灵活的功能。

本文将从二维阵列结构的定义、特点和设计原则等方面探讨其重要性和发展方向。

1.2 文章结构本文将按照以下结构展开讨论二维阵列结构设计的相关内容:1. 引言:首先对文章的主题进行概述,介绍文章的结构和目的,引出对二维阵列结构设计的重要性和必要性进行探讨。

2. 正文:2.1 二维阵列结构的定义和特点:介绍二维阵列结构的基本概念和特点,为后续讨论提供基础。

2.2 二维阵列结构的设计原则:探讨二维阵列结构设计的一些基本原则和方法,以便读者更好地理解如何进行有效的设计。

3. 结论:3.1 总结二维阵列结构设计的重要性:总结本文对二维阵列结构设计的探讨,强调其在实际应用中的重要性和价值。

3.2 展望未来二维阵列结构设计的发展方向:对未来二维阵列结构设计的发展趋势和方向进行展望,为读者提供对未来工作的启示。

通过以上结构,本文将系统性地介绍二维阵列结构设计的相关内容,希望能够给读者带来一些启发和思考。

1.3 目的二维阵列结构设计的目的是为了提供一种有效的方法来组织和管理大量数据或元素。

通过设计一个合理的二维阵列结构,可以更容易地对数据进行存储、检索和处理,提高数据处理的效率和准确性。

此外,二维阵列结构设计还可以帮助优化系统的性能和资源利用率,提高系统的可扩展性和可维护性。

在设计二维阵列结构时,需要考虑到数据的类型、规模、访问模式等因素,并根据实际需求选择合适的数据结构和算法。

通过合理的设计,可以使数据的组织结构更加清晰和高效,提升系统整体的性能和用户体验。

因此,二维阵列结构设计是一项重要的技术工作,对于提升系统的功能和性能具有重要意义。

flash存储阵列结构及存储原理

flash存储阵列结构及存储原理Flash存储阵列结构及存储原理一、引言随着信息技术的快速发展,存储设备变得越来越重要。

在各种存储设备中,Flash存储器由于其高速、低功耗、可靠性高等特点而备受青睐。

本文将介绍Flash存储阵列的结构和存储原理。

二、Flash存储阵列的结构Flash存储阵列是由多个Flash存储芯片组成的,它们通过控制器相互连接。

一个Flash存储芯片通常由多个存储单元组成,每个存储单元都可以存储一个比特的数据。

为了提高存储密度,每个存储单元通常还可以存储多个比特的数据。

Flash存储阵列通常采用多级存储结构,将多个存储单元组成一个块,多个块组成一个页,多个页组成一个主存储区。

每个存储单元都有一个唯一的地址,可以通过地址来访问和操作其中的数据。

三、Flash存储原理1. 存储过程Flash存储器使用非易失性存储技术,它可以在断电后保持存储的数据不丢失。

在写入数据时,Flash存储器需要先擦除一个块,然后再将数据写入。

擦除是一个相对较慢的过程,一般需要几毫秒甚至更长的时间。

因此,Flash存储器的写入速度相对较慢。

而读取数据时,Flash存储器可以直接访问存储单元,速度较快。

2. 坏块管理随着Flash存储芯片使用时间的增加,由于擦除和写入操作的限制,存储单元可能会出现坏块。

坏块是指由于某些原因,存储单元无法正常擦除或写入数据的情况。

为了保证数据的可靠性和存储效率,Flash存储阵列需要进行坏块管理。

坏块管理通常通过在控制器中维护一个坏块表来实现,将出现坏块的存储单元标记为不可用,从而避免对坏块进行读写操作。

3. 数据安全性由于Flash存储器的特殊性,当出现断电或异常情况时,存储单元中的数据可能会丢失或损坏。

为了保证数据的安全性,Flash存储阵列通常采用错误检测和纠正编码技术。

这些技术可以检测和纠正存储单元中的错误,从而提高数据的可靠性。

4. 读写算法Flash存储器采用的读写算法对于性能和寿命有着重要影响。

薄膜存储器设计原理及应用

薄膜存储器设计原理及应用薄膜存储器是一种使用薄膜作为储存介质的存储器,它具有体积小、速度快、功耗低等优点,适用于各种计算机和电子设备中。

本文将从薄膜存储器的设计原理以及应用方面进行介绍。

薄膜存储器的设计原理主要包括储存单元的结构设计、存储介质的选择和读写操作原理。

首先是储存单元的结构设计。

薄膜存储器通常采用二维阵列的方式组织储存单元,每个储存单元由一个薄膜电容器和一个晶体管组成。

薄膜电容器是储存信息的基本单元,其内部由两层金属电极和一个绝缘层构成。

晶体管则用于控制电容器的读写操作,通过控制晶体管的导通与否,可以实现对电容器的充放电。

其次是存储介质的选择。

常见的存储介质包括氧化铝薄膜、硅酸盐薄膜等。

这些材料具有高密度、长寿命、低功耗等特点,可以满足薄膜存储器对于存储介质的要求。

同时,存储介质的选择还需要考虑其与电容器的充放电性质的匹配,以确保薄膜存储器的稳定性和可靠性。

最后是读写操作原理。

对于薄膜存储器的读操作,首先需要将要读取的储存单元的地址选通,使其与读操作线路相连。

然后,通过控制电压的方式,判断电容器的电荷状态,并将其转化为相应的电信号。

对于薄膜存储器的写操作,也需要将要写入的储存单元的地址选通,并根据要写入的数据信息,控制晶体管的导通与否,对电容器进行充电或放电。

薄膜存储器具有广泛的应用领域。

首先是在计算机内存方面,薄膜存储器可以作为主存或者高速缓存来使用。

其快速的读写速度和低功耗特性,使得它成为了现代计算机系统中重要的存储组件。

其次是在电子产品中的应用。

例如,智能手机、平板电脑和移动设备等,在限制尺寸和功耗的条件下,需要高性能的存储器来满足用户对速度和体验的需求。

薄膜存储器具有较小的体积和低功耗的特点,能够满足这些产品对存储器的要求。

此外,薄膜存储器还广泛应用于嵌入式系统和物联网设备中。

这些设备通常在资源受限的环境下工作,因此需要小型化和低功耗的存储器。

薄膜存储器不仅可以满足这些需求,还具有较高的可靠性和稳定性,能够适应各种恶劣的工作环境。

flash存储阵列结构及存储原理

flash存储阵列结构及存储原理一、引言随着信息时代的到来,数据量的爆发式增长给传统存储系统带来了巨大的挑战。

为了满足高性能、高可靠性和高容量的存储需求,flash存储阵列应运而生。

它以其快速的读写速度、低延迟和可靠性等优势,成为了现代存储系统的重要组成部分。

二、flash存储阵列的基本结构flash存储阵列由多个flash芯片组成,这些芯片通过控制器进行管理和操作。

每个flash芯片由多个存储单元组成,每个存储单元可以存储一定量的数据。

为了提高存储容量和读写性能,flash芯片通常采用多层堆叠的方式,使得每个芯片的存储单元数量大大增加。

flash存储阵列中的每个flash芯片都有自己的访问接口,通过控制器对这些接口进行管理和调度,实现对存储单元的访问和操作。

控制器还负责处理数据的编码、错误校验、读写请求的调度等功能。

此外,控制器还负责管理芯片之间的数据传输和数据的冗余备份,以提高系统的可靠性。

三、flash存储原理flash存储采用电子存储技术,数据以电荷的形式存储在存储单元中。

存储单元由浮栅电容和控制栅组成,在写入数据时,通过给控制栅施加高电压,将电荷注入浮栅电容中,改变浮栅电容的电荷状态,从而实现数据的存储。

读取数据时,通过控制栅和源极之间的电压差来判断浮栅电容中是否有电荷,从而确定存储单元中存储的数据。

flash存储的特点是可以进行快速的随机读取操作,但写入操作相对较慢。

为了解决写入速度慢的问题,flash存储采用了块擦除的操作方式。

块擦除是指在写入新数据之前,需要将整个存储块的数据擦除,然后再写入新数据。

这种操作方式带来了一定的性能损失,但可以确保写入数据的准确性和一致性。

四、flash存储阵列的工作原理flash存储阵列通过将多个flash芯片组织起来,形成一个存储单元的数组。

在写入数据时,控制器将数据分散存储到各个flash芯片中的存储单元中,从而实现数据的并行写入。

在读取数据时,控制器可以同时从多个flash芯片中读取数据,从而提高读取的效率。

阵列工艺流程

阵列工艺流程

《阵列工艺流程》

阵列工艺流程是一种在半导体制造中常用的工艺流程,它主要用于制作集成电路中的阵列部分,如存储器和传感器等。

在阵列工艺流程中,首先需要设计和制造掩模板。

掩模板是一个具有精密图案的透光板,它被用来在硅片上进行光刻,从而形成所需的器件结构。

然后将掩模板与硅片结合,通过光刻和刻蚀的工艺,将图案转移到硅片表面。

接着进行掺杂、膨胀氧化和金属化等工艺步骤,最终形成了完整的阵列结构。

阵列工艺流程的关键在于高精度的图案转移和对器件结构的控制。

在整个流程中,需要严格控制各个工艺步骤的参数,以确保最终器件具有稳定的性能和可靠的品质。

随着半导体技术的不断发展,阵列工艺流程也在不断完善和优化。

新材料、新工艺和新装备的引入,使得阵列器件的制造变得更加精密和高效。

总的来说,《阵列工艺流程》是一种复杂而关键的半导体制造工艺,它在现代科技中发挥着重要的作用。

随着技术的进步,相信它的应用领域和发展前景还将继续拓展。

nand flash的物理存储单元的阵列组织结构

nand flash的物理存储单元的阵列组织结构NAND Flash是一种非易失性存储器,广泛应用于各种电子设备中,如手机、平板电脑、闪存盘等。

它由一系列的存储单元组成,每个存储单元可以存储一个或多个位信息。

这些存储单元按照一定的阵列组织结构进行排列,从而形成整个NAND Flash芯片。

NAND Flash的物理存储单元通常是由一对浮栅电极和控制门电极构成的。

浮栅电极位于控制门电极的下方,两者之间有一层非导电介质隔离。

在正常工作状态下,浮栅电极将保持不导电状态。

当电压信号被加载到控制门电极上时,电场将穿过非导电介质隔离,导致浮栅电极上的电荷被吸引或排斥。

通过操作控制门电压的大小和信号的频率,可以实现存储单元内部的信息的读取和写入。

在NAND Flash芯片中,所有的存储单元按照一定的行和列的排列方式进行组织。

每个存储单元都有一个唯一的物理地址,通过这个地址可以准确定位到特定的存储单元。

行和列的排列方式决定了存储单元的访问模式。

通常,一次读取或写入操作会涉及到多个存储单元,这些存储单元被组织成所谓的存储块。

存储块是NAND Flash中的最小逻辑单位,它由一组相邻的存储单元组成。

一个存储块通常包含若干行和列,行数和列数的具体取决于芯片的规格和厂商的实现。

每个存储单元都有一个唯一的物理地址,而存储块则使用逻辑地址来进行标识。

逻辑地址和物理地址之间的映射关系由Flash控制器进行管理。

为了在NAND Flash中进行数据的读取和写入操作,Flash控制器需要了解存储单元的排列方式和映射关系。

这些信息通常以元数据的形式存储在芯片内部。

元数据包含了存储块的状态、健康程度、使用情况等信息。

Flash控制器可以根据这些信息对存储单元进行管理和调度,以保证数据的可靠性和性能。

除了存储块的组织方式,NAND Flash还需要考虑存储单元的读取和写入速度。

由于存储单元内部的物理结构决定了读取和写入操作的速度,NAND Flash芯片通常会使用一些优化技术来提高性能。

陕西师范大学_计算机组成原理_课件ppt_白中英第5版_chp3

∙31/171∙ 陕西师范大学 计算机科学学院

图(a)表示写1到存储 位元。此时输出缓 冲器关闭、刷新缓 冲器关闭,输入缓 冲器打开(R/W为 低),输入数据 DIN=1送到存储元位 读放 线上,而行选线为 高,打开MOS管, 于是位线上的高电 平给电容器充电, 表示存储了1。

播放I

MOS管

∙27/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

∙28/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

∙29/171∙ 陕西师范大学 计算机科学学院

3.3 DRAM存储器

一、DRAM存储位元的记忆原理

› ›

SRAM存储器的存储位元是锁存器,它具 有两个稳定的状态。 DRAM存储器的存储位元是由一个MOS 晶体管和电容器组成的记忆电路,如图 3.6所示。

图(c)表示从存储位 元读出1。输入缓冲 器和刷新缓冲器关闭, 输出缓冲器/读放打 开(R/W为高)。行 选线为高,打开 MOS管,电容上所 存储的1送到位线上, 通过输出缓冲器读出 放大器发送到DOUT, 即DOUT=1。

∙34/171∙ 陕西师范大学 计算机科学学院

图(d)表示(c)读出1后 存储位元重写1。由于 (c)中读出1是破坏性 读出,必须恢复存储 位元中原存的1。此时 输入缓冲器关闭,刷 新缓冲器打开,输出 缓冲器读放打开, DOUT=1经刷新缓冲器 送到位线上,再经 MOS管写到电容上。

∙14/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

主存(内部存储器)是半导体存储器。根

据信息存储的机理不同可以分为两类: 相对而言 › 静态读写存储器(SRAM): 存取速度快,一般用作Cache › 动态读写存储器(DRAM): 存储容量大,一般用作主存

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SRAM 时序 自定时技术

12.2 存储器内核

• 只读存储器

– NOR ROM / NAND ROM

• 非易失性读写存储器

– EPROM / EEPROM / Flash

• 读写存储器

– SRAM / DRAM

存储器和阵列结构设计11

12.2.1 只读存储器

• 工作原理

• 优缺点比较BL源自BLBLDecoder reduces the number of select signals

K = log2N

存储器和阵列结构设计5

存储阵列

Problem: ASPECT RATIO or HEIGHT >> WIDTH

存储器和阵列结构设计6

Amplify swing to rail-to-rail amplitude

Decoder

Word N2 2 Word N2 1

Input-Output (M bits)

Intuitive architecture for N x M memory Too many select signals:

N words == N select signals

Input-Output (M bits)

Cell

注意在布线GND信号时采用了扩散区

存储器和阵列结构设计15

• 单元的大部分面积用于位线接触和接地连接 • 解决方案:采用不同的存储器结构

VDD Pull-up devices BL [0] BL [1] BL [2] BL [3] WL [0]

WL [1]

WL [2]

WL [3]

未被选中的行,字线全部为高电平

思考题12.31 MOS NAND ROM

确定图12.13的ROM中存放在地址0、1、2和3处的数据值

Selects appropriate word

层次化的存储结构

优点: 1、本地字线和位线的长度较短 2、快地址只用来激活被寻址的块节省功耗

存储器和阵列结构设计7

例12.2 层次化的存储结构

Clock generator

Z -address buffer

X -address buffer

Predecoder and block selector Bit line load

WL[0]

WL [1]

GND

WL [2] WL [3]

GND

BL [0] BL [1] BL [2] BL [3]

存储器和阵列结构设计14

ROM存储器编程

• 存储单元和上拉晶体管尺寸的问题 • 噪声容限换取性能 • ACTIVE和CONTACT编程方式的比较

Polysilicon Metal1 Diffusion Metal1 on Diffusion

12.1.2 存储器总体结构和单元模块

M bits

S0

Word 0

S1 S2

Word 1 Word 2

A0

Storage

cell

A1

M bits

S0 Word 0 Word 1 Word 2

Storage cell

NworSdNs2 2

SN2 1

Word N 2 2 Word N 2 1

AK2 1 K 5 log2N

Memory

Read-Only Memory

Random Access

SRAM DRAM

Non-Random Access

FIFO LIFO Shift Register CAM

EPROM E2PROM

FLASH

Mask-Programmed Programmable (PROM)

存储器和阵列结构设计4

本章重点

1. 存储器的分类和结构 2. 只读、非易失性及读写存储器的数据存储单元 3. 外围电路——灵敏放大器、译码器、驱动器和时序产生

器 4. 存储器设计中的功耗和可靠性问题

存储器和阵列结构设计1

12.1 引言

• 密集的数据存储电路是数字电路或系统设计者的主要考 虑之一

• 将存储单元组成大的阵列,这可以使外围电路的开销最 小并增加存储密度

I/O buffer

x1/x4 controller

Y-address buffer

X -address buffer

Local row decode

存储器和阵列结构设计8

[Hirose90]

I/O Buffers Commands Address Decoder 29 Validity Bits Priority Encoder

VDD

WL

WL

WL

1

BL

BL

BL

WL

0

WL WL

GND

二极管ROM

MOS ROM1

MOS ROM2

图12.9 ROM的1和0单元的不同实现方式

存储器和阵列结构设计12

思考题12.1 MOS NOR ROM阵列

确定图12.10的ROM中存放在地址0、1、2和3处的数据值

BL[0] BL[1] BL[2] BL[3]

• 本章的意义在于它应用了大量前几章中介绍过的电路技 术

• 存储器设计可以看成一个高性能、高密度和低功耗电路 的设计实例

存储器和阵列结构设计2

12.1.1 存储器分类

• 时序参数

– 读出时间/写入时间/读周期/写周期

存储器和阵列结构设计3

半导体存储器分类

Read-Write Memory

Non-Volatile Read-Write

128 K Array Block 0 Subglobal roGwlodbeaclordoewr dSeucbogdleorbal row decoder

BBlolcokck3130

Block 1

CS, WE buffer

Transfer gate Column decoder

Sense amplifier and write driver

CAM存储器

• 支持3种工作模式:读、写和匹配

Data (64 bits)

Comparand Mask

Control Logic R/W Address (9 bits)

CAM Array 29 words 3 64 bits

存储器和阵列结构设计9

存储器时序

DRAM 时序 多路分时寻址技术

存储器和阵列结构设计10

WL[0] VDD

WL[1]

WL[2] VDD

WL[3]

Vbias Pull-down loads

注意:图中如何使电源线在相邻单元之间共享而减少了它们的用量

存储器和阵列结构设计13

思考题12.2 MOS NOR ROM存储器阵列

确定图12.11的ROM中存放在地址0、1、2和3处的数据值

V DD Pull-up devices