第五章 组合逻辑电路典型例题分析

组合逻辑电路例题解析.

第11章组合逻辑电路例题解析F 一个输出函数,用 T i 、T 2分别标注中间变量。

(2 )写出输出逻辑函数表达式为 T 1=A O B T 2=C O D表 11.1A BcD 1 戸1A B cD F 0 0 0 01 0 c 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 \ 1 1 0 1 1 0 0 1 0 0 0 1 1 0 0 1 0 t (} 1 1 1 1 0 1 0 0 I 1 0 11 J 1 0 0 0111| 11111F= T 1O T 2=A O B O C O D(3 )根据表达式列出真值表如表 11.1所示。

(4 )功能说明。

从真值表可看出,当 A , B , C , D 四输入变量中有偶数个 1 (包括全0 )时电路输出F 为1,而有奇数个1时,输出F 为0,因此这是一个四输入的偶校验电路。

例11. 2组合逻辑电路如图11.2所示。

已知A , B , C 是输入变量,F 1和F 2是输出函数, 试写出输出函数 F 1和F 2的逻辑表达式,并分析该组合逻辑电路的逻辑功能。

解:(1)根据逻辑图可写出输出函数 F 1和F 2的逻辑表达式并化简。

H = AB ; I = A+B ; J = IC = (A+B)C ; K = I+C = A+B+C : M = HC = ABCN = H+J = AB+(A+B)C Q = KN = (A+B+C)AB+(A+B)C例11. 1分析图11.1电路的逻辑功能。

解 ⑴在图11.1中,有A , B , C , D 四输入变量, 图 11.1y輛入输出输入精出A B C岭A B C y(与0000010010 001]010101 U1010I1001 0i10111i11 F1=ABC+(A+B+C)(A+B)(A+C)(B+C)=ABC+ABC+ABC+ABC=A(B O C)+A(B O C)=A O B O CF2= N= AB+(A+B)C=AB+AC+BC (2)根据F l和F?的逻辑表达式列出真值表如表11.2所示。

第3、5章 组合电路和时序电路(总复习)

【总复习卷】第3、5章组合逻辑电路和时序逻辑电路在数字电路系统中,按照逻辑功能和电路特点,各种数字集成电路可分为组合逻辑电路和时序逻辑电路两大类。

【知识结构图】【本章重点】第3章、组合逻辑电路1.组合逻辑电路在电路结构及逻辑功能上的特点。

2.编码器和译码器的电路设计。

3.各类编码及译码器逻辑功能介绍。

4.集成编码器及译码器使用。

第5章、时序逻辑电路1.时序逻辑电路在电路结构及编逻辑功能上的特点。

2.各类寄存器寄存数码的原理。

3.二进制和非二进制计数器工作原理及波形图。

4.简单异步二进制计数器的设计。

5.常用中大规模计数器的使用。

【本章难点】1.编码器、译码器真值表的写法。

2.同步计数器计数状态的分析。

【本章考点】1.组合逻辑电路和时序逻辑电路的各自的特点。

2.编码器和译码器电路设计及工作原理分析。

3.寄存器寄存数码的工作过程(波形)。

4.各种类型计数器的计数状态表、状态转换图、工作波形图。

综合训练(第3、5章)一、填空题1. 在数字电路系统中,按照逻辑功能和电路特点,各种数字集成电路可分为_________逻辑电路和_________逻辑电路两大类。

2. 把0和1按一定规律编排,使每组代码具有一个特定的含义的过程,称为_________。

把代码的特定含义翻译出来的过程称为_________。

3. ________常用于接收、暂存、传递数码等。

存放n位二进制数码需要______个触发器。

4. 能实现_________操作的电路称为计数器;按计数时各触发器状态转换与计数脉冲是否同步。

可分为_________计数器和_________计数器。

_________进制计数器是各种计数器基础。

5. 一个四位二进制减法计数器状态为_________时,再输入一个计数脉冲,计数状态为1111,并向高位发出__________信号。

6. 要把y0、y1.......y11、y12十三个信号编成二进制代码.至少需要_________位二进制数码。

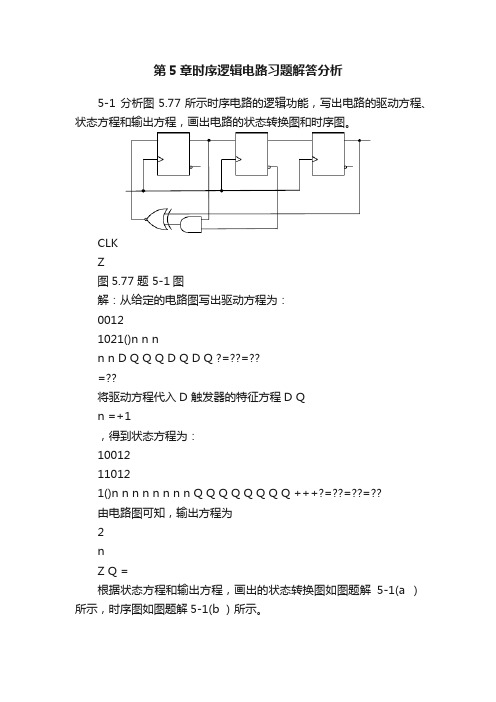

第5章时序逻辑电路习题解答分析

第5章时序逻辑电路习题解答分析5-1 分析图5.77所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图5.77 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n nn n D Q Q Q D Q D Q ?=??=??=??将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n n n n Q Q Q Q Q Q Q Q +++?=??=??=??由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图5.78所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图5.78 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ?=?==+??将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++?=?==+??电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图5.79(a)所示,其输入波形如图5.79 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

第5章组合逻辑、时序逻辑Verilog语言描述(已排)

5.1.1 组合逻辑电路的连续赋值实现

以2路选择器为例:

module mux2to1( a, b, sel, out); input a, b; input sel; output out; assign out = (sel) ? b:a;

endmodule

注意:

连续赋值语句的被赋值变量只能是线网wire型。

注意: 过程块描述的组合逻辑电路: 1. 被赋值变量只能是reg型; 2. 触发方式采用电平触发; 3. always@( )引导的敏感量要完整。

5

always过程块与连续赋值语句描述的组合逻辑电路效果相同 两种方法描述的2路选择器电路均相同, 综合工具根据Verilog代码综合自动生成的电路均为下图所示

4

5.1.2 组合逻辑电路的always过程块实现

仍然以2路选择器为例: module mux2to1( a, b, sel, out);

input a, b; input sel; output out; reg out; always @(sel or a or b)

out = (sel) ? b:a; endmodule

endmodule

13

对应的CMOS工艺下D触发器的电路结构

. d

q

. . . clk

rst clk

d

T1

clk

q

T3

rst

clk clk

clk clk

T2

T4

.q

D触发器符号

clk

clk

D触发器电路图

说明:复位信号不受时钟信号clk的影响。 只要复位信号rst为高电平时,电路就复位,输出q为0。

14

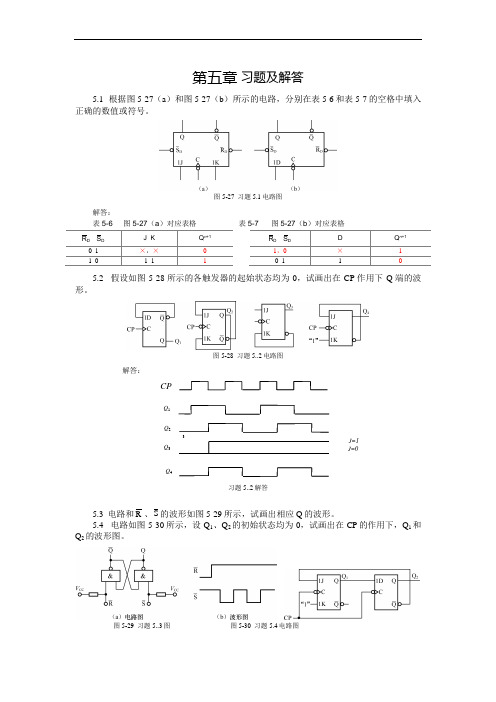

第五章 习题及解答

解答:

习题5..2解答

5.3电路和 、 的波形如图5-29所示,试画出相应Q的波形。

5.4电路如图5-30所示,设Q1、Q2的初始状态均为0,试画出在CP的作用下,Q1和Q2的波形图。

图5-29习题5..3图图5-30习题5.4电路图

解答:

习题5..3解答习题5.4解答

5.5试画出图5-31(a)所示的电路在图5-31(b)的激励信号的作用下,Q和Z的波形(设Q的初始状态为0)。

第五章

5.1根据图5-27(a)和图5-27(b)所示的电路,分别在表5-6和表5-7的空格中填入正确的数值或符号。

图5-27习题5.1电路图

解答:

表5-6图5-27(a)对应表格表5-7图5-27(b)对应表格

J K

Qn+1

D

Qn+1

0 1

×,×

0

1,0

×

1

1 0

1 1

1

0 11Βιβλιοθήκη 05.2假设如图5-28所示的各触发器的起始状态均为0,试画出在CP作用下Q端的波形。

图5-31习题5..5图

解答:

习题5..5解答

5.6逻辑电路如图题5-32所示,已知CP和X的波形,试画出Q1和Q2的波形。触发器的初始状态均为0。

解答:

`

图5-32习题5..6图`

5.7逻辑电路如图5-33所示,已知CP'和A的波形,画出触发器Q端的波形,设触发器的初始状态为0。

解答:

5.8逻辑电路和各输入信号波形如图5-34所示,画出两触发器Q端的波形。两触发器的初始状态均为0。

图5-34习题5..8图

解答:

5.9逻辑电路和输入信号波形如图5-35所示,画出各触发器Q端的波形。触发器的初始状态均为0。

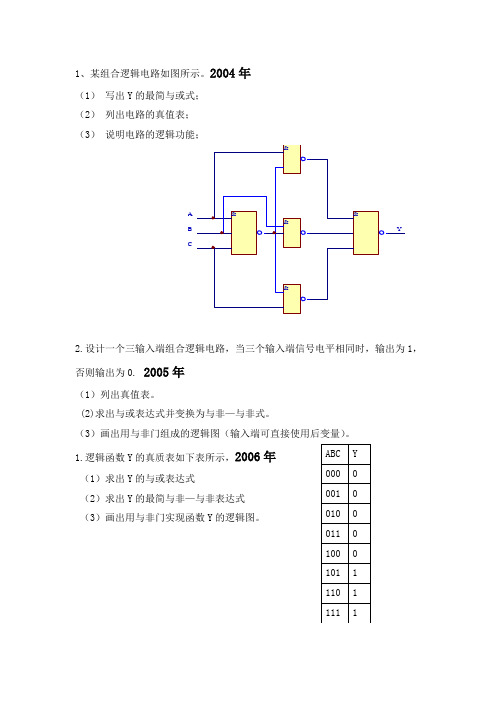

组合逻辑电路分析.

A B C(1) 写出Y 的最简与或式; (2) 列出电路的真值表; (3) 说明电路的逻辑功能;2.设计一个三输入端组合逻辑电路,当三个输入端信号电平相同时,输出为1,否则输出为0. 2005年(1)列出真值表。

(2)求出与或表达式并变换为与非—与非式。

(3)画出用与非门组成的逻辑图(输入端可直接使用后变量)。

1.逻辑函数Y 的真质表如下表所示,2006年(1)求出Y 的与或表达式(2)求出Y 的最简与非—与非表达式 (3)画出用与非门实现函数Y 的逻辑图。

(1)写出Y1、Y2、Y3的表达式; (2)写出Y 的最简与或门; (3)画出化简后的逻辑电路图。

A B C图3.31、组合逻辑电路的输入A 、B 、C 和输出F 的波形如图所示。

2008年 (1)列出真值表;(2)写出逻辑函数表达式并化简; (3)用最少的与非门实现。

1、只有一辆自行车,要求只有在A 同意的情况下,B 和C 才可以骑,但B 具有优先权,B 不骑时C 才可以骑。

(1)列出真值表。

(2)写出最简逻辑表达式,(3)试用与非门设计电路,画出逻辑电路图。

2009年三、简答题1. (8-5中)设一位二进制半加器的被加数为A ,加数为B ,本位之和为S ,向高位进位为C ,试根据真值表 1).写出逻辑表达式 2).画出其逻辑图。

真值表:2.(8-5难)设一位二进制全加器的被加数为A i,加数为B i,本位之和为S i,向高位进位为C i,来自低位的进位为C i-1,根据真值表1).写出逻辑表达式2).画出其逻辑图。

真值表:3.(8-1难)分析图示逻辑电路:1).列真值表2).写出逻辑表达式3).说明其逻辑功能。

=++,根据给出的4.(8-3难*)用一个74LS138译码器实现逻辑函数Y ABC ABC ABC部分逻辑图完成逻辑图的连接。

5.(8-1中)简单回答组合逻辑电路的设计步骤。

6.(8-1难)试用2输入与非门和反向器设计一个3输入(I0、I1、I2)、3输出(L0、L1、L2)的信号排队电路。

第5章时序逻辑电路思考题与习题题解

思考题与习题题解5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。

(2)构成一异步2n进制加法计数器需要n 个触发器,一般将每个触发器接成计数或T’型触发器。

计数脉冲输入端相连,高位触发器的CP端与邻低位Q端相连。

(3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4个时钟脉冲CP后可串行输出4位数码。

(4)要组成模15计数器,至少需要采用 4 个触发器。

5-2判断题(1)异步时序电路的各级触发器类型不同。

(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

(×)(3)具有N个独立的状态,计满N个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。

(√)(4)计数器的模是指构成计数器的触发器的个数。

(×)5-3单项选择题(1)下列电路中,不属于组合逻辑电路的是(D)。

A.编码器B.译码器C.数据选择器D.计数器(2)同步时序电路和异步时序电路比较,其差异在于后者( B)。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关(3)在下列逻辑电路中,不是组合逻辑电路的有( D)。

A.译码器B.编码器C.全加器D.寄存器(4)某移位寄存器的时钟脉冲频率为完成该操作需要(B)时间。

100KHz,欲将存放在该寄存器中的数左移8位,A.10μSB.80μSC.100μSD.800ms(5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要(C )个触发器。

A.6B.7C.8D.10(6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。

A.10B.15C.32D.32768(7)一位8421BCD 码计数器至少需要(B)个触发器。

(完整版)组合逻辑电路设计例题

9.4、组合逻辑电路的分析与设计习题1、在一旅游胜地,有两辆缆车可供游客上下山,请设计一个控制缆车正常运行的逻辑电路。

要求:缆车A 和B在同一时刻只能允许一上一下的行驶,并且必须同时把缆车的门关好后才能行使。

设输入为A、B、C,输出为Y。

(设缆车上行为“1”,门关上为“1”,允许行驶为“1”)(1) 列真值表;(2)写出逻辑函数式;(3)用基本门画出实现上述逻辑功能的逻辑电路图。

解:(1)列真值表:(3)逻辑电路图:)()(____________BACBABACCBABCAF⊕=+=+=2、某同学参加三类课程考试,规定如下:文化课程(A)及格得2分,不及格得0分;专业理论课程(B)及格得3分,不及格得0分;专业技能课程(C)及格得5分,不及格得0分。

若总分大于6分则可顺利过关(Y),试根据上述内容完成:(1)列出真值表;(2)写出逻辑函数表达式,并化简成最简式;(3)用与非门画出实现上述功能的逻辑电路。

(3)逻辑电路图(2)逻辑函数表达式BCACABCBABCCBABCCBAABCBCAABCCBABCAF+=+=+=+=++=++=)()(__________________ABFAFBCAFBC3、中等职业学校规定机电专业的学生,至少取得钳工(A)、车工(B)、电工(C)中级技能证书的任意两种,才允许毕业(Y )。

试根据上述要求:(1)列出真值表;(2)写出逻辑表达式,并化成最简的与非—与非形式;(3)用与非门画出完成上述功能的逻辑电路。

解:(1(3)逻辑电路:(2)逻辑表达式:最简的与非—与非形式:ABC C AB C B A BC A F +++=_____________________________________________________________________________________________________________AB BC AC AB BC AC AB BC AC AB BC AC F ••=•+=++=++=4、用基本逻辑门电路设计一个一位二进制全加器,输入变量有:A 为被加数,B 为加数,C 为较低位的进位,输出函数为本位和S 及向较高位的进位H 。

组合逻辑电路的分析

9

解:(1)据题意,列出真值表。

如I0、I1、I2均为0,则L0、L1、L2也均为0。

输入

I0

I1

I2

0

0

0

1

×

×

0

1

×

0

0

1

输出

L0

L1

L2

0

0

0

1

0

0

0

1

0

0

0

1

2019/11/18

数字电子技术

10

当I0为1时,无论I1和I2为1还是0,输出L0为1, L1和L2为0;

输入

I0

I1

I2

0

0

0

1

×

×

0

1

×

0

0

1

输出

L0

L1

L2

0

0

0

1

0

0

0

1

0

0

0

1

2019/11/18

数字电子技术

11

当I0为0且I1为1,无论I2为1还是0,输出L1为1, 其余两个输出为0;

输入

I0

I1

I2

0

0

0

1

×

×

0

1

×

0

0

1

输出

L0

L1

L2

0

0

0

1

0

0

0

1

0

0

0

1

2019/11/18

数字电子技术

12

当I2为1且I0和I1均为0时,输出L2为1,其余两个 输出为0;

输入

I0

组合逻辑电路分析与设计习题解答

A

B

C

D

F

A

B

C

D

F

0

0

0

0

0

1

0

0

0

0

0

0

0

101来自001

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

0

1

0

1

1

1

0

1

0

0

0

1

1

0

0

0

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

1

1

0

1

0

1

1

1

0

1

1

1

1

1

组合逻辑电路设计(1)

A

B

C

D

组合逻辑电路分析(3)

F ABCD ABC D ABCD ABC D ABCD ABC D ABCD ABC D

CD

AB

00

01 11

10

00

1

1

01

1

1

11

1

1

10

1

1

组合逻辑电路分析(3)

F ABCD ABC D ABCD ABC D ABCD ABC D ABCD ABC D

电路功能: 在ABC取值中,若1

的个数为奇数,则输出 S为1;

在ABC取值中,若1 的个数为两个或三个, 则输出C为1;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章 组合逻辑电路典型例题分析

第一部分:例题剖析

例1.求以下电路的输出表达式:

解:

例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.

解:

Y = AC BC ABC

= AC +BC + ABC

= C(AB) +CAB = C (AB)

T4138的功能表

&

&

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y

7

“1”

T4138

A B C

A2A1A0YaYbS1 S2 S

3

0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S1S2S31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A2A1A0Y0Y1Y2Y3Y4Y5Y6Y70 1 1 1 1 1 1 1

1 0 1 1 1 1 1 1

1 1 0 1 1 1 1 1

1 1 1 0 1 1 1 1

1 1 1 1 0 1 1 1

1 1 1 1 1 0 1 1

1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 0

例3.分析如图电路,写出输出函数Z的表达式。CC4512为八选一数据选择器。

解:

例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。(表

中未出现的输入变量状态组合可作为约束项)

CC4512的功能表

ADIS INH2A1A0Y

1 0 10 00 00 00 00 00 00 00 0

0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

Z

CC4512

A

0

A

1

A

2

D0 D1 D2 D3 D4 D5 D6 D

7

DIS

INH

D

1

D

A B C D Y

0 0 0 0 1

0 0 0 1 0

0 0 1 0 1

0 0 1 1 0

0 1 0 0 0

CD

AB 00 01 11 10

00 1 0 0 1

01 0 1 0 1

11 ××××

10 0 1 ××

&

&

A

B

第一步画卡诺图第三步

画逻辑电路图

例5.写出下面组合电路的输出表达式,分析逻辑功能。

解:第一步 写出表达式,进行化简。

第二步 说明功能: 此电路为三变量中,取值为奇数个一时,Y输出为1,或者判奇数电路。

例6:四选一数据选择器框图如下图所示。已知

用它实现函数 :

(1) 写出F的最小项表达式;

(2) 在图上括号中把满足输出函数F的信号A、B、C及常量1、0填在括号中。

解:本题不难分析可得出如下结论:

若A=A1,B=A0,则D0=1,D1=1,D2=0,D3=C

&

Y

A

B

C

&&&&&

&

Y = AB A ·AB B ·C ·AB A ·AB B ·AB A ·AB B ·C ·C

= A B C + A B C + A B C + A B C

= A B C

++

第二部分:即学即练

第五章 组合逻辑电路自测练习

1、四选一数据选择器框图如下图所示。已

知

用它实现函数 :

(1) 写出F的最小项表达式;

(2) 在图上括号中把满足输出函数F的信号A、B、C及常量1、0填在括号中。

2、试分析下图电路的功能,写出输出Z的表达式。双四选一数据选择器CC1419的 功能表

达式如下:

3、试写出下图所示门电路组成的逻辑电路的逻辑表达式和逻辑真值表,并分析其逻辑

功能。

输入 输出

S A B Y0 Y1 Y2 Y3

1 φ φ

0 0 0 0 1

1 0

4、如图所示3线-8线译码器T4138逻辑功能表达式为:

,,……,,

正常工作时,S1=1, 。

写出Z1和Z2的表达式,列出真值表,说明电路功能。

5、试用四选一多路选择器实现函数

6、试分析下图所示电路,列出真值表,说明电路功能。

1 1

7、试用一片八选一多路选择器实现逻辑函数:

8、试用一片四选一多路选择器实现逻辑函数:

9、分析下图所示电路,列出真值表和Y3、Y2、Y1、Y0的逻辑表达式,说明电路功能。

10、试分析下图所示逻辑电路,列出真值表,写出Y1、Y2、Y3的逻辑表达式,说明电路

功能。

11、分析下图所示电路,列出真值表,写出F的逻辑表达式,说明电路功能。

第五章 组合逻辑电路自测题参考答案

1、

若A=A1,B=A0,则D0=1,D1=1,D2=0,D3=C

2、

3、S = 0 时,

真 值 表

输 入 输 出

S A B Y0 Y1 Y2 Y3

1 × × 1 1 1 1

0

0 0 0 1 1 1

0 1 1 0 1 1

1 0 1 1 0 1

1 1 1 1 1 0

功能:2线-4线译码器

4、

= (本位和)

= (进位)

功能:一位全加器。真值表如下:

5、设:S1 = A1 ,S0 = A0 ,Z = Y

D1 = 0 D2 = V D3 = 1

输入 输出

A B C Z2 Z1

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

6、功能:一位二进制比较器。真值表如下:

输入 输出

A B Y0 Y1 Y2

0 0 0 1 0

0 1 0 0 1

1 0 1 0 0

1 1 0 1 0

7、设A = A2 ,B = A1 ,C = A0 ,F = Y

则D0 = D4 = D4 = D7 = 1,D2 = D3 = D5 = D6 = 0

电路如下图:

8、设A = A1 ,B = A0 ,F = Y

则 D0 = 1 ,D1 = 0

D2 = ,D3 = C

电路如下图:

9、Y0 = , , ,

功能:2线-4线译码器。(真值表如下)。

10、

功能:4线-2线优先编码器(真值表略)。

11、F=AB+BC+AC,功能:多数表决电路。真值表如下:

输入 输出

A B C F

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1