电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现

基于AD7606的多通道数据采集系统设计

基于AD7606的多通道数据采集系统设计

陶海军;张一鸣;曾志辉

【期刊名称】《工矿自动化》

【年(卷),期】2013(039)012

【摘要】针对DSP芯片TMS320F2812自带的AD转换模块不能满足同步采集电流和电压参数要求的问题,设计了一种基于AD7606的多通道数据采集系统.详细介绍了系统中电压/电流输入电路、输入滤波电路、AD7606与TMS320F2812接口电路、AD转换程序的设计.测试结果表明,与TMS320F2812自带的AD转换模块进行AD转换的结果相比,采用AD7606进行AD转换的结果精度高、误差小,适合高精度AD转换电路.

【总页数】4页(P110-113)

【作者】陶海军;张一鸣;曾志辉

【作者单位】北京工业大学电子信息与控制工程学院,北京 100124;河南理工大学电气工程与自动化学院,河南焦作454003;北京工业大学电子信息与控制工程学院,北京 100124;北京工业大学电子信息与控制工程学院,北京 100124;河南理工大学电气工程与自动化学院,河南焦作454003

【正文语种】中文

【中图分类】TD67

【相关文献】

1.基于AD7606的同步多通道语音采集系统设计 [J], 王森

2.基于AD7606的智能电网数据采集系统设计 [J], 王水鱼;王伟

3.基于AD7606的树莓派多通道数据采集系统设计 [J], 刘喜梅;吕文韬

4.基于FPGA的多通道数据采集系统设计应用 [J], 王旭东;陈涛;郑磊

5.基于FPGA的多通道数据采集系统设计应用 [J], 王旭东;陈涛;郑磊

因版权原因,仅展示原文概要,查看原文内容请购买。

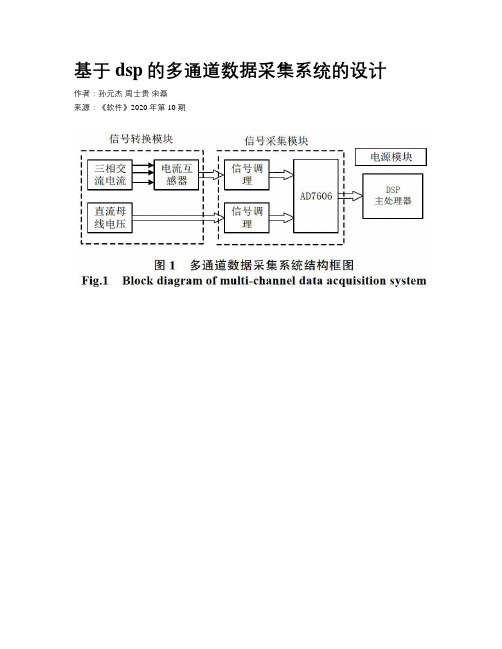

基于dsp的多通道数据采集系统的设计

基于dsp的多通道数据采集系统的设计作者:孙元杰周士贵宋磊来源:《软件》2020年第10期摘要:针对DSP内部AD采样电路精度低等问题,设计了一种以AD7606高精度实时的模数转换器,进行采集交流信号,并介绍分析了AD7606得硬件电路和软件设计。

最后通过实验对比了DSP TMS320F28335内部AD和AD7606这两种模数转换得精度,相对于DSP TMS320F28335内部AD,AD7606具有采样精度更高,误差小,能够高速采样,适用于永磁同步电机的数据得采集转换。

关键词: AD7606;硬件电路;高速采样中图分类号: TP274.2 文献标识码: A DOI:10.3969/j.issn.1003-6970.2020.10.026本文著录格式:孙元杰,周士贵,宋磊. 基于DSP的多通道数据采集系统的设计[J]. 软件,2020,41(10):105108【Abstract】: Aiming at the low accuracy of the internal AD sampling circuit of the DSP, a high-precision real-time digital-to-analog converter based on the AD7606 is designed, and the hardware circuit and software design of the AD7606 are introduced and analyzed. Finally, the two AD-analog conversion precisions in the DSP TMS320F28335 and AD7606 are compared throughexperiments. Compared with the DSP TMS320F28335 AD, the AD7606 has higher sampling accuracy, less error, and high real-time performance. Acquisition conversion.【Key words】: AD7606; Hardware circuit; High-speed sampling0 引言隨着永磁同步电机的广泛应用,各种控制算法控制理论的不断在永磁同步电机的控制中应用。

16通道声发射同步数据采集中的电路设计

16通道声发射同步数据采集中的电路设计16通道声发射同步数据采集是一种用于采集多个声源信号并实现同步数据传输的技术。

在这种技术中,多个声源信号将被同时采集并用于数据传输,这就需要一个稳定可靠的电路设计来实现这一功能。

本文将介绍16通道声发射同步数据采集中的电路设计,包括硬件和软件部分。

一、硬件设计1. 信号输入在16通道声发射同步数据采集中,首先需要设计一个能够接收多个声源信号的信号输入电路。

这个电路一般会使用16个输入通道,每个通道都会有一个专门的接收电路。

这些接收电路可以是放大器、滤波器等,用来增强和净化声源信号。

2. 数据转换和传输接收到声源信号后,需要将这些信号进行数字化处理,然后传输给输入输出接口,用于后续处理。

在这个过程中,通常会使用模数转换器(ADC)来完成模拟信号到数字信号的转换,然后通过串行通信接口(SPI)、并行接口等方式将数据传输给主控制器。

3. 主控制器主控制器是整个系统的核心部分,它将接收到的数字化声源信号进行处理和分析,并将这些数据传输给外部设备。

在16通道声发射同步数据采集中,主控制器一般会选用高性能的微处理器或者数字信号处理器(DSP)。

4. 时钟同步为了实现数据的同步采集,需要设计一个时钟同步电路,可以让所有通道的数据采集动作在同一时刻进行。

这需要使用精准的时钟电路,通过外部时钟信号或者自身的时钟生成电路来实现。

5. 供电管理在整个系统中,需要设计一个供电管理电路,用于为各个模块提供稳定的电源。

这个电路一般包括稳压器、滤波器等,用于消除功率噪声和提供稳定的电压输出。

1. 数据处理在16通道声发射同步数据采集中,需要设计一套完善的数据处理算法,用于处理和分析接收到的声源信号。

这个算法一般会包括信号滤波、功率谱分析、时域分析等,用于获取声源信号的各种特征。

接收到的数据需要进行存储和传输,一般会设计一个数据存储和传输模块。

这个模块一般会使用固态存储器,如SD卡、EEPROM等,用于存储采集到的数据。

基于FPGA+AD7606的多通道数据采样系统设计与实现

基于FPGA+AD7606的多通道数据采样系统设计与实现蒋思宇;王斌;余龙海;余腾飞

【期刊名称】《电子设计工程》

【年(卷),期】2022(30)22

【摘要】随着电网的发展,基于柔性互联技术的配电网逐渐成为未来智能配电网的发展趋势。

为了满足柔性配电设备在监测其电能质量过程中实时性高精度多通道的采集需求,基于Altera公司的EP4CE10F17C8型FPGA提出了一种实时采样设计方案。

系统利用AD7606采样芯片,结合硬件电路中常用的状态机思想,完成FPGA 对AD7606的相关配置,实现高精度多通道AD采样系统。

通过实验表明,设计的采样系统能够满足一定的采样速度、采样精度及采样可靠性要求,可应用在柔性互联配电等领域。

【总页数】5页(P103-107)

【作者】蒋思宇;王斌;余龙海;余腾飞

【作者单位】武汉科技大学信息科学与工程学院;大力电工襄阳股份有限公司;湖北春田电工技术有限公司

【正文语种】中文

【中图分类】TN79

【相关文献】

1.基于多通道采样数据的高速存储系统设计

2.基于VXI总线的多通道多采样率数据采集系统实现

3.基于高速采样ADC的多通道数据采集系统设计

4.一种基于

FPGA的多通道数据采集系统设计与实现5.基于STM32和USB的多通道数据采集系统设计与实现

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP+FPGA+AD的多通路模拟信号采集方案的研究

基于DSP+FPGA+AD的多通路模拟信号采集方案的研究作者:王志伟张炜来源:《科技视界》 2014年第20期王志伟张炜(平高集团有限公司,河南平顶山 467001)【摘要】随着数字信号处理技术和计算机的不断发展,现代工业生产和科学技术研究都需要借助数字处理技术。

本文主要研究如何用现场可编程逻辑门阵列(FPGA:XC3S1200E),数字信号处理器(DSP:TMS320F28335)和模数转换器件(AD:AD7606)建立模拟信号采集方案。

本文详细介绍了模拟信号采集硬件方案、软件方案。

【关键词】DSP+FPGA结构;采集方案;模数转换1 硬件方案框图(图1)2模数转换模数转换就是将模拟量转换为数字量的过程。

理论分析指出,只有适当的采样频率才能真实地反映原始信号波形。

经验数据表明,至少使用4倍于信号最高频率的采样频率才能保证不会丢失信号的任何信息。

AD7606模数转换芯片是AI公司推出的一款高性能模数转换芯片。

它的主要特征是,8通道双极性模拟量输入,最大输入范围±10V,轨对轨采样保持,16位并联或串联多种输出方式,最高200k SPS的采样速率。

完全符合一般用途的模拟信号采样要求。

使用3片AD可以同时完成24路的模拟信号采集3异步总线异步通信总线提供可以在FPGA和AD之间提供一个隔离作用,同时完成AD的输出电平和FPGA的I/O电平对接。

SN74LVC16245是由TI公司设计的一款被专门用来做异步总线通信的芯片。

可以通过设置器件的(OE)、(DIR)可很容易实现总线的关闭、数据的双向传输,并且数据的双向传输功能基本上不需要额外的时序要求即可实现。

4DSP+FPGA结构DSP(Digital Singnal Processor)是一种具备完整指令系统的微处理器。

片内集成了控制单元、运算单元、各种寄存器和通信单元等,同时还可以外扩各种存储器,具有强大的运算能力和高运算速度。

TMS320F28335是TI公司的一款低端多功能DPS芯片,内嵌32位高性能CPU、DMA存储器、增强型控制外设、32位时钟定时器、串行端口外设和内部模数转换器等丰富外设模块。

基于STM32及AD7606的16通道同步数据采集系统设计

基于STM32及AD7606的16通道同步数据采集系统设计摘要: 介绍了基于STM32及AD7606的同步数据采集系统的软硬件设计。

主控芯片采用基于ARM Cortex-M4内核的STM32F407IGT6,实现对AD 采集数据的实时计算并通过以太网络进行数据传输。

A7606为16位、8通道同步采样模数数据采集系统[],利用两片AD7606,可以实现对16路通道的实时同步采样。

经过测试,该系统可以实现较高精度的实时数据采集。

0 引言[此处找书介绍STM32],该芯片主频可达168MHz,具有丰富的片内外设,并且与前代相比增加了浮点运算单元(Floating Point Unit,FPU),使其可以满足数据采集系统中的 [介绍AD7606]1 系统总体方案设计整个系统由传感器模块、信号调理模块、数据采集模块、处理器STM32、及通信模块及上位机系统组成。

系统整体结构框图如图1所示。

本系统是为液态金属电池性能测试设计,需要测量电池的充放电电压、电流以及交流加热系统的电压、电流,并以此计算出整个液态金属电池储能系统的效率。

因此两片AD7606的16个通道分为两组,每组8个通道,这两组分别测量4路直流、交流的电压和电流信号。

AD7606通过并行接口与STM32连接,STM32读取AD 采样数据后进行计算,并将数据通过网络芯片DP83848通过UDP 协议发送给上位机。

上位机负责显示各通道采集信息、绘制波形以及保存数据等。

STM32F407IGT6霍尔直流传感器上位机软件DP83848直流信号交流信号交流互感器调理电路调理电路AD7606AD7606图1 系统整体结构框图2 系统硬件设计2.1 模拟信号采集电路设计 模拟信号的采集包含直流电压、电流,交流电压、电流四部分。

直流信号的采集分别使用霍尔电压传感器HNV025A 和霍尔电流传感器HNC100B ,两种传感器的电路原理图类似,仅以霍尔电压传感器电路原理图为例说明,如图2-1所示。

基于AD7606的同步多通道语音采集系统设计

基于AD7606的同步多通道语音采集系统设计

王森

【期刊名称】《电子质量》

【年(卷),期】2018(0)3

【摘要】语音是用于信息交流的重要媒介,清晰的提取语音信号是准确信息传递的前提,面对日益复杂的声场环境,麦克风阵列系统以优异的性能逐渐替代单麦克风系统.为了更好地应用麦克风阵列实现语音定位与增强,设计了一款包含低噪声前置放大器、信号调理电路和高速多路同步采集ADC的麦克风阵列系统.经过试验,该系统能够清晰准确地实现多路语音信号采集.

【总页数】3页(P31-33)

【作者】王森

【作者单位】山东科技大学电气与自动化工程学院,山东青岛266590

【正文语种】中文

【中图分类】TP274+.2

【相关文献】

1.基于AD7606的多通道数据采集系统设计 [J], 陶海军;张一鸣;曾志辉

2.基于AD7606的SVG数据同步采集系统设计 [J], 黄华钦;刘桂英;周路平;曾林俊;胡宸

3.基于FPGA的多通道同步实时高速数据采集系统设计 [J], 易志强;韩宾;江虹;张秋云

4.基于GD32F407及CL1606的多通道同步采集系统设计 [J], 罗瑞;徐涛;卢少微;

马克明

5.基于AD7606的树莓派多通道数据采集系统设计 [J], 刘喜梅;吕文韬

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DE0-Nano的多通道模拟信号采集系统设计

作者简介:金瑞(1993-),女,湖北咸宁人,硕士研究生。研究方向:嵌入式 FPGA 设计。 刘昌华(1963-),男,湖北武汉人,教授,硕士生导师。研究方向:计算机网络及应用、嵌入式 FPGA 设计。

1 引言

由于在智能电网中,待测的电压和电流值一般要经过互 感器输出到 ADC,所以在它的设计中可能有会含有一定数量 的互感器。但是电流和电压往往属于小信号一类,因此,需 要高动态范围(Dynamic Range)、高 SNR 的 ADC,同时为 提高信号处理技术的准确度,实现未来智能化变电站系统所 需要的分辨率和性能,需要模数转换器 ADC 具有强大的同 步采样能力 [1]。

将 +5 V 电 源 经 过 0.1 µF 去 耦 电 容 连 接 到 AD7606 的 4 个 VCC 电源引脚,使本设计供电电源处于稳定的状态; 将 +3.3 V 电 源 经 过 0.1 µF 去 耦 电 容 连 接 VDRIVE 引 脚, 要 使 AD7606 与 FPGA 在 同 一 电 源 下 一 起 工 作, 需 要 在 Quartus II 13.0 平 台 上 配 置 管 脚 时 将 I/O Standard 设 置 为 3.3-VLVCOMS;将 +3.3 V 电源(逻辑高电平)经过两个电 阻分压得到高电平连接 RANGE 引脚,采用的模拟电压范围 是 ±10 V;将 +3.3 V 电源连接到 PAR/SER/BYTE SEL 引脚、 将地信号(逻辑低电平)经过 2 k 电阻连接 DB15 引脚,本 设计采用串口接口模式;将 +3.3 V 电源连接 REFSEL 引脚, 采用内部基准电压模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电力系统中多通道同步采样ADC(AD7606)与浮点DSP(ADSP-21479)通信的设计与实现内容1. 简介31.1 AD7606简介31.2 ADSP-21479简介42. AD7606和ADSP-21479配置与连接53. 时序分析64. 测试结果和结论74.1测试结果74.2结论105. DSP参考代码106. 参考文献121简介1.1AD7606简介AD7606是16位,8通道同步采样模数数据采集系统。

AD7606完全满足电力系统的要求,具有灵活的数字滤波器、2.5V基准电压源、基准电压缓冲以及高速串行和并行接口。

它采用5V单电源供电,可以处理±10V和±5V真双极性输入信号、同时所有通道均能以高达200kSPS 的吞吐率采样。

图1 AD7606的内部原理框图。

图2 AD7606的管脚图。

• A Vcc模拟电源,4.75V~5.25V• Vdrive逻辑部分电源• Vdd模拟输入部分正电压• Vss模拟输入部分负电压• DGND 数字地• AGND 模拟地1.2ADSP-21479简介ADSP-21479是SIMD (单指令多数据)SHARC家族中的一员,它基于65nm的最新工艺,具有低成本,低功耗的的特点,是一颗集成有大容量片上SRAM和ROM的32/40位浮点DSP。

ADSP-21479是性能出色,266MHZ/1596MFLOP:• 266 MHz/1596FLOPS SIMD SHARC内核,支持32-bit浮点、40-bit浮点以及16/32-bit 定点数据类型• 支持多达5 Mb 片内SRAM• 支持16位宽SDR、SDRAM存储器接口• 数字应用接口DAI,支持多达8个的高速同步串口(SPORT)及SPI串口• 2个精确时钟发生器• 20线数字I/O端口• 3个定时器、UART、I2C兼容接口• ROM/JTAG安全模式• 供应196引脚CSP_BGA封装与100引脚LQFP封装产品,适合于工业客户的要求• 供应商业级、工业级温度与汽车级温度等级产品图3 ADSP-21479的内部原理框图。

2AD7606和ADSP-21479配置与连接AD7606芯片的供电采用单5V供电,见图4所示:图4。

AD7606供电示意图。

AD7606采用硬件配置方式,具体配置如下:1) 设置RANGE=0时,模拟输入范围是±5Vref。

2) 设置/PAR /SER/BYTE SEL为高电平,选择使用串行模式。

3) CONVSTA, CONVSTB ,使用同源激励。

4) 设置REF SELECT=0 ,使用外部参考电压SHARC ADSP-21479 SRU设置:SPORT0_SCLK ◊ DAIP 1SPORT0_FS ◊ DAIP 4SPORT0_DA ◊ DAIP 5FLAG4 ◊ DPI_PIN1FLAG5 ◊ DPI_PIN2根据以上配置,ADSP-21479通过SPORT口与AD7606联系的系统示意图如图5所示:图5 采用串行方式时,AD7606与ADSP-21479硬件连接示意图3时序分析AD7606工作时序如图6,通过DSP的FLAG信号驱动CONVST A/B信号启动转换过程,BUSY标志着工作状态,连接到DSP的中断输入。

BUSY为高时表示处于转换状态,转换完毕后高到低的下降沿引起DSP中断,DSP在响应中断通过SPORT0读取8通道ADC转换好的数据。

图6 AD7606串行读取数据时序ADSP-21479 SPORT口的时序如图7所示,在FS信号启动后,数据随着时钟节拍被读取。

我们选择SPORT数据宽度是32位,那么四次FS信号即可读取八个通道的数据。

图7 ADSP-21479 SPOR T串行数据接收时序4测试结果和结论DSP软件设置50K的采样信号,对8个通道的数据进行同时采样。

各模拟通道输入信号分别为:通道5连接1KHz正弦波,其余通道接地。

4.1测试结果1) 利用VDSP5.0++ 的plot窗口(VDSP->View->Debug Windows->Plot)观察5通道数据,1. 通道5提取到1KHz正弦波;4.2结论这种连接方式只使用DSP的一个串行SPORT口即可同时读取8路ADC的数据。

但由于8路数据都通过一路数据输出给DSP,而AD7606支持的最高串行时钟频率有限,模数转换还要占用一部分采样周期,因此串行输出的连接下,AD7606不能工作在最高200KSPS采样率下。

根据AD7606数据手册,AD7606的SCLK上限为23.5MHz。

FLAG信号驱动CONVST A/B 信号,单路串行输出八通道数据。

不考虑转换时间最高采样率可达23500000/(16×8)=183.5kHz,由于每个周期数据转换将消耗一定时间,所以实际无法达到此速度。

假设采样周期用Tconvst 表示,根据AD7606数据手册,模数转换时间为3.45us,所以Tconvst-3.45us代表采样周期中传输数据的时间。

八通道总数据量为128个时钟周期,所以(Tconvst-3)/128近似为每bit数据的时钟周期。

由于SCLK最大为23.5MHz,据此可以推算出此模式下最高采样频率:(Tconvst(max)-3.45)/128 = 1/23.5Tconvst(max)≈8.89us即最高采样率为1/ Tconvst(max) = 112KSPS同理可知,若采用两口同时输出转换数据,即启动2个SPORT分别读取8个通道的数据,实际最高采样率能达到161K SPS。

当AD7606采用并行方式输出到DSP时,即可得到最高200KSPS采样率。

5DSP参考代码1. 配置SRU// This function will setup the SRU RegistersvoidInitSRU(void){//Generating Code for connecting : SPORT0_CLK to DAI_PIN1SRU (HIGH, PBEN01_I);SRU (SPORT0_CLK_O, DAI_PB01_I);//Generating Code for connecting : SPORT0_FS to DAI_PIN4SRU (HIGH, PBEN04_I);SRU (SPORT0_FS_O, DAI_PB04_I);//Generating Code for connecting : DAI_PIN5 to SPORT0_DASRU (LOW, PBEN05_I);SRU (DAI_PB05_O, SPORT0_DA_I);//Generating Code for connecting : FLAG4 to DPI_PIN1SRU (HIGH, DPI_PBEN01_I);SRU (FLAG4_O, DPI_PB01_I);//Generating Code for connecting : FLAG5 to DPI_PIN2SRU (HIGH, DPI_PBEN02_I);SRU (FLAG5_O, DPI_PB02_I);}2. IRQ1 BUSY中断服务程序void AD7606_BUSY_IRQs(intsig_int){busy++;interrupt(SIG_SP0,Count_SPORT0_RX_IRQs);#ifdef DMA* (volatile int *)SPCTL0 =( SPEN_A | SLEN32 | ICLK | IFS | LAFS | SDEN_A | FSR | DITFS| LFS );#endif#ifdef CORE* (volatile int *) SPCTL0 =( SLEN16 | ICLK | IFS | FSR | LAFS | LFS | DITFS); *(volatile int *) SPCTL0 |=SPEN_A ;#endif}3. SPORT初始化程序voidinit_sport(){* (volatile int *) SPCTL0 = 0;* (volatile int *) SPCTL1 = 0;* (volatile int *) SPMCTL0 = 0;* (volatile int *) SPMCTL1 = 0;SPORT_DMA_setup:* (volatile int *) IISP0A =(int)rx_buf0a ;* (volatile int *) IMSP0A = 1;* (volatile int *) CSP0A = CHNUM;//configure the sport/* *//* CLKDIV0=[fCCLK(266 MHz)/4xFSCLK(17 MHz)]-1 = 0x0005 *//* FSDIV0=[FSCLK(10 MHz)/TFS(2 MHz)]-1 = 31 = 0x001F *///13m hz 1m 0x00080003;/* Configure SPORT0 as a reciever (Rx) */* (volatile int *) DIV0 = 0x001F0005;}4. SPORT 中断程序void Count_SPORT0_RX_IRQs(intsig_int){SP0I_counter++;#ifdef CORErx_buf0a[(SP0I_counter-1)*CHNUM]=(short)(*pRXSP0A);#endif* (volatile int *) SPCTL0 =0;finished=1;#ifdef DMAif(SP0I_counter==1024){* (volatile int *) IISP0A =(int)rx_buf0a ;SP0I_counter=0;}else* (volatile int *) IISP0A =(int)(rx_buf0a+ (SP0I_counter)*CHNUM); * (volatile int *) IMSP0A = 1;* (volatile int *) CSP0A = CHNUM;#endifinterrupt(SIG_SP0,SIG_IGN);}。