数字信号处理器与串行EEPROM的接口设计

SPI和IIC详解

支持可靠通信的硬件CRC 可触发中断的主模式故障、过载以及CRC错误标志 支持DMA功能的1字节发送和接收缓冲器:产生发送和接受请求

10

第10页,共30页。

11

第11页,共30页。

控制寄存器SPI_CR1

BIDIMODE 0 0 1 1

BIDIOE X X 1 0

RXONLY 0 1 X X

9

第9页,共30页。

STM32的SPI接口

3线全双工同步传输 带或不带第三根双向数据线的双线单工同步传输 8或16位传输帧格式选择 主或从操作

支持多主模式

8个主模式波特率预分频系数(最大为fPCLK/2) 从模式频率(最大为fPCLK/2) 主模式和从模式的快速通信 主模式和从模式下均可以由软件或硬件进行NSS管理:主/从操作模式的动态改变 可编程的时钟极性和相位 可编程的数据顺序,MSB在前或LSB在前 可触发中断的专用发送和接收标志

发送CRC寄存器(SPI_TXCRCR)

17

第17页,共30页。

SPI中断

中断响应函数 Void SPIx_IRQHandler(void) ;

18

第18页,共30页。

SPI配置流程

(1)配置引脚复用功能 i) 使能spi时钟;

ii)设置引脚复用 (2)设置工作模式

i) 主/从设置

ii) 数据格式设置

iii)时钟极性/相位设置 iv)单线/双线模式、接收/输出模式 v) CRC设置 vi) 中断/DMA设置 (3)使能SPI,开始工作

19

第19页,共30页。

初 始 化 函 数

20

第20页,共30页。

/

发 送

接 收 函 数

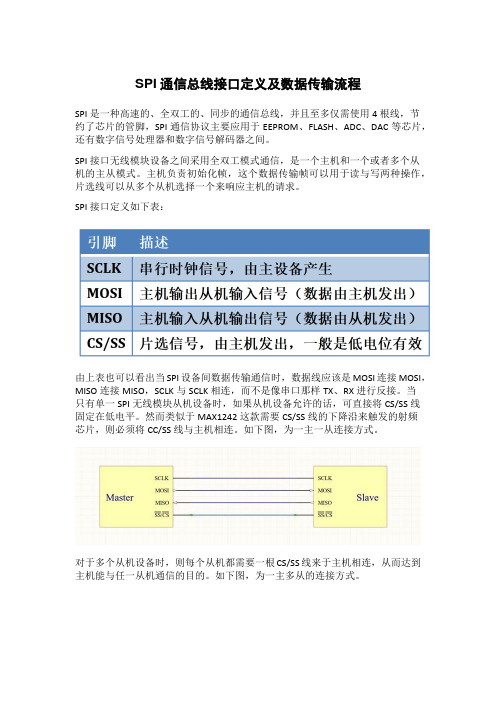

SPI通信总线接口定义及数据传输流程

SPI通信总线接口定义及数据传输流程SPI是一种高速的、全双工的、同步的通信总线,并且至多仅需使用4根线,节约了芯片的管脚,SPI通信协议主要应用于EEPROM、FLASH、ADC、DAC等芯片,还有数字信号处理器和数字信号解码器之间。

SPI接口无线模块设备之间采用全双工模式通信,是一个主机和一个或者多个从机的主从模式。

主机负责初始化帧,这个数据传输帧可以用于读与写两种操作,片选线可以从多个从机选择一个来响应主机的请求。

SPI接口定义如下表:由上表也可以看出当SPI设备间数据传输通信时,数据线应该是MOSI连接MOSI,MISO连接MISO,SCLK与SCLK相连,而不是像串口那样TX、RX进行反接。

当只有单一SPI无线模块从机设备时,如果从机设备允许的话,可直接将CS/SS线固定在低电平。

然而类似于MAX1242这款需要CS/SS线的下降沿来触发的射频芯片,则必须将CC/SS线与主机相连。

如下图,为一主一从连接方式。

对于多个从机设备时,则每个从机都需要一根CS/SS线来于主机相连,从而达到主机能与任一从机通信的目的。

如下图,为一主多从的连接方式。

大多数从机设备都有着三态逻辑的特性,因此当设备未被选中时,它们的MISO 信号线会变成高阻抗状态(电气断开)。

没有三态输出的设备则需外接三态缓冲器才能与其他的从机设备共享SPI总线。

数据传输在SPI通信中,SPI主机设备以从机设备支持的频率通过SCLK线给到SPI从机设备,这点也意味着从机是无法主动向主机发送数据的,只能主机轮询向从机发或者从机设备主动通过一个IO口来告知主机数据到达。

在SPI每个时钟周期内,都会进行一次全双工数据的传输。

主机通过MOSI线上发送1bit时,从机也会在读取到之后通过MISO线发送1bit数据出去。

这说明,即使只进行单工通信,也会保持此通信顺序。

SPI传输通常涉及到两个给定了字长的移位寄存器。

例如在主机、从机中的8bit 的移位寄存器。

FM1288中文数据手册

图 13:IIS 的上升沿锁存,LRCK 高左声道,1 个周期的延迟.........................29

图 14:IIS 的上升沿锁存,LRCK 高左声道,0 个周期的延迟.........................30

图 15:IIS 的上升沿锁存,LRCK 高为右声道,1 个周期的延迟.....................30

图 4 : fm-1288Biblioteka 例 如 表 格1 单独的最小系

统....................................................................15

图 5:例如 UART 协议..............................................................................................22

图 10:IIS 的下降沿锁存,LRCK 高左声道,0 个周期的延迟..........................28

图 11:IIS 的下降沿锁存,LRCK 高为右声道,1 个周期的延迟.....................28

图 12:IIS 的下降沿锁存,LRCK 高为右声道,0 个周期的延迟.....................29

4

状态信息

本产品数据表的状态是产品信息。

预报 关于富迪产品开发设计人员的信息。文档中指定的所有值都是设计的目标

值。如果指定的最小值和最大值,仅作为指导到最终规格的限制,并且不能被视 为最终的值。

所有的详细规格,包括引脚电气规格没有通知情况下也可能被富迪改变。

预生产信息

引脚和机械尺寸规格定稿。文档中指定的所有值都是设计的目标值。如果指 定的最小值和最大值,仅作为指导到最终规格的限制,并且不能被视为最终的值。

PCI9052接口电路的功能及应用

PCI9052接口电路的功能及应用摘要:PCI总线是Pentium主机最常见的总线,基于PCI总线形成的CompactPCI和PXI总线广泛地应用在仪器和自动化领域。

PCI适配卡的接口设计变得越来越重要,介绍PCI专用接口电路PCI9052的功能,通过一个例子介绍它的应用。

关键词:外部设备互连总线;局部总线;接口电路;PCI9052;应用1 引言PCI总线具有独立于处理器、高数据传速率、即插即用、低功耗、适应性强等特点,已成为微型机的主流总线。

基于PCI总线形成的CompactPCI和PXI总线广泛应用于仪器和自动化领域。

随着PCI总线的广泛应用,其接口的设计开发显得尤为重要。

由于PCI总线的独特性能,如信号负载能力、支持数据的突发传送、地址/数据、命令/字节使能信号总线复用等,使中小规模的器件难以实现接口电路。

实现PCI总线接口一般采用CPLD或FPGA设计PCI接口,这种方法难度很大;另一种是采用专用的PCI接口电路,使设计开发者免除繁琐的时序分析,缩短开发周期,降低开发成本。

本文介绍PCI9052接口电路的功能及其在PCI板卡设计中的应用。

2 接口电路PCI9052是PLX公司开发的低价位PCI总线目标接口电路,功耗低,采用PQFP型160引脚封装,符合规范,它的局部总线(LOCAL BUS)可以通过编程设置为8/16/32位的(非)复用总线,数据传送率可达到132Mb/s。

提供了ISA接口,可以使ISA适配器迅速、低成本地转换到PCI总线上。

主要功能与特性如下所述:异步操作。

PCI9052的Local Bus与PCI总线的时钟相互独立运行,两总线的异步运行便于高、低速设备的兼容。

Local Bus的运行时钟频率范围为0MHz~40MHz,TTL电平,PCI的运行时钟频率范围为0MHz~33MHz。

支持突发操作。

PCI9052提供一个64字节的写FIFO和一个32字节的读FIFO,从而支持预取模式即突发操作。

ARM,DSP,CPLD,EDA,FPGA名词解释

ARM,DSP,CPLD,EDA,FPGA名词解释什么是armARM (Advanced RISC Machines),既可以认为是一个技术的名字,也可以认为是对一类微处理器的通称,还可以认为是一种公司的名字。

1991 年 ARM 公司成立于英国剑桥,主要出售芯片设计技术的授权。

目前,采用 ARM技术知识产权( IP )核的微处理器,即我们通常所说的 ARM 微处理器,已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于 ARM 技术的微处理器应用约占据了 32 位 RISC 微处理器 75 %以上的市场份额, ARM 技术正在逐步渗入到我们生活的各个方面。

ARM 公司是专门从事基于 RISC 技术芯片设计开发的公司,作为知识产权供应商,本身不直接从事芯片生产,*转让设计许可由合作公司生产各具特色的芯片,世界各大半导体生产商从ARM公司购买其设计的 ARM 微处理器核,根据各自不同的应用领域,加入适当的外围电路,从而形成自己的 ARM 微处理器芯片进入市场。

目前,全世界有几十家大的半导体公司都使用 ARM 公司的授权,因此既使得 ARM 技术获得更多的第三方工具、制造、软件的支持,又使整个系统成本降低,使产品更容易进入市场被消费者所接受,更具有竞争力。

什么是单片机单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

同时,学习使用单片机是了解计算机原理与结构的最佳选择。

可以说,二十世纪跨越了三个“电”的时代,即电气时代、电子时代和现已进入的电脑时代。

不过,这种电脑,通常是指个人计算机,简称PC机。

它由主机、键盘、显示器等组成(如图1所示)。

还有一类计算机,大多数人却不怎么熟悉。

这种计算机就是把智能赋予各种机械的单片机(亦称微控制器)。

基于PCI总线的实时图像识别与跟踪平台设计

基于PCI总线的实时图像识别与跟踪平台设计关键词:PWM SG3524 控制器在没有红外探测器或其它图像采集设备的条件下,可以先开发基于PCI总线的图像处理平台,由计算机模拟图像的生成并完成图像的高速传输,以缩短系统开发周期,使系统灵活、实用、便于进行功能扩展。

采用美国TI公司的新一代高性能浮点数字信号处理器TMS320C6701(以下简称C6701)研制了实时图像识别与跟踪处理平台,利用不变矩进行图像识别,采用质心跟踪方案,获得了很好的实验效果。

充分发挥了C6701强大的数字信号处理能力,并为后续的研究提供了很好的软硬件平台基础。

1C6701数字信号处理器简介C6701芯片内有8个并行处理单元,分为相同的两组。

采用甚长指令字VLIW结构,使C6701成为高性能的数字信号处理芯片。

其单指令字长为32b,8个指令组成一个指令包,总字长为256b。

芯片内部设置了专门的指令分配模块,可以将每个256b指令包同时分配到8个处理单元,8个单元可同时运行。

芯片的最高时钟频率达到167MHz,此时浮点运算处理能力可达到1GFLOPS。

外部存储器接口EMIF支持8/16/32b数据宽度的各种类型的同步、异步存储器,便于系统扩展。

C6701片内有64KB的数据RAM和64KB的程序RAM;片外存储空间分为4个区(CE0、CE1、CE2、CE3);有4个相互独立的可编程DMA通道,还有第五个DMA通道可与HPI接口。

2PCI9054的主要特点及应用PCI09054是美国PLX公司生产的一种32b33MHz的PCI总线主控I/O加速器。

采用先进的PLX流水线结构;符合PCI本地总线规范2.2版,突发传输速率达到132MB/s;本地总线复用/非复用的32b地址/数据线,有M、J、C三种工作模式,但C模式的数据和地址总线是非复用的;支持8b、16b、32b外围设备和存储设备,本地总线操作速率高达50MHz;内部有6种可编程的FIFO,可实现零等待的突发传输及本地总线时钟和PCI总线时钟的异步操作,支持主模式、从模式和DMA传输模式。

8b10b_SERDES_数字CDR

8b/10b SERDES的接口设计摘要串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

起初,SERDES 是独立的ASSP 或ASIC 器件。

在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

本方案是以CEM最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

关键字:HR03、SERDES、CDR1硬件接口:KinT_dataT_clkR_clk硬件的接口如上图所示,主要包括发送与接收模块。

发送模块包括8b/10b编码器,并串转换器,锁相环(PLL)频率合成器和发送器,接收模块包括8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的10 位8b/10b 编码,并串转换用于将10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将CMOS 电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

在接收端,接收器将接收到的低摆幅差分信号还原为CMOS 电平的串行信号,CDR 从串行信号中抽取时钟信息,完成对串行数据的最佳采样,串并转换利用CDR 恢复的时钟,将串行信号转换成10 位的并行数据,Comma 检测器检测特殊的Comma 字符,调整字边界,字边界正确的并行数据经过8b/10b 解码,还原为字节信号,传送到上层协议芯片,完成整个信息传输过程。

PCI接口简介

简介PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,它是目前个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽。

PCI插槽也是主板带有最多数量的插槽类型,在目前流行的台式机主板上,ATX结构的主板一般带有5~6个PCI 插槽,而小一点的MATX主板也都带有2~3个PCI插槽,可见其应用的广泛性。

编辑本段发展历史PCI是由Intel公司1991年推出的一种局部总线。

从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。

管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能,它为显卡,声卡,网卡,MODEM等设备提供了连接接口,它的工作频率为33MHz/66MHz。

最早提出的PCI 总线工作在33MHz 频率之下,传输带宽达到了133MB/s(33MHz X 32bit/8),基本上满足了当时处理器的发展需要。

随着对更高性能的要求,1993年又提出了64bit 的PCI 总线,后来又提出把PCI 总线的频率提升到66MHz。

目前广泛采用的是32-bit、33MHz 的PCI 总线,64bit的PCI插槽更多是应用于服务器产品。

由于PCI 总线只有133MB/s 的带宽,对声卡、网卡、视频卡等绝大多数输入/输出设备显得绰绰有余,但对性能日益强大的显卡则无法满足其需求。

目前PCI接口的显卡已经不多见了,只有较老的PC上才有,厂商也很少推出此类接口的产品。

当然,很多服务器不需要显卡性能好,因此使用古老的PCI显卡。

通常只有一些完全不带有显卡专用插槽(例如AGP 或者PCI Express)的主板上才考虑使用PCI显卡,例如为了升级845GL主板。

PCI显卡性能受到极大限制,并且由于数量稀少,因此价格也并不便宜,只有在不得已的情况才考虑使用PCI显卡。

【转载】SPI总线和I2C总线的异同点

【转载】SPI总线和I2C总线的异同点总结的简单、明了、适⽤!⼀:SPI接⼝的全称是"Serial Peripheral Interface",意为串⾏外围接⼝,是Motorola⾸先在其MC68HCXX系列处理器上定义的。

SPI接⼝主要应⽤在EEPROM、FLASH、、AD,还有和数字信号解码器之间。

(1)MOSI – 主器件,从器件数据输⼊(2)MISO – 主器件数据输⼊,从器件数据输出(3)SCLK –,由主器件产⽣,最⼤为fPCLK/2,从模式频率最⼤为fCPU/2(4)NSS – 从器件使能信号,由主器件控制,有的IC会标注为CS(Chip select)⼆:I2C总线是由Philips公司开发的⼀种简单、双向⼆线制同步串⾏总线。

它只需要两根线即可在连接于总线上的器件之间传送信息。

SDA(串⾏数据线)和SCL(串⾏时钟线)都是双向I/O线。

三:2种总线的异同点1:I2C总线是半双⼯,2根线SCL SDA;SPI总线实现全双⼯,4根线SCK CS MOSI MISO。

2:I2C是多主机总线,通过SDA上的地址信息来锁定从设备;SPI只有⼀个主设备,主设备通过CS⽚选来确定从设备。

3:I2C总线传输速度100Kbps----4Mbps;SPI可达30Mbps以上。

4:I2C总线空闲时SDA SCL都是⾼电平,SPI总线空闲状态由CPOL(时钟极性)决定。

5:I2C⾼电平时SDA下降沿标志传输开始,上升沿标志传输结束;SPI总线CS拉低标志传输开始,CS拉⾼标志传输结束。

6:I2C总线SCL⾼电平采样;SPI具体根据CPHA(时钟相位)决定,⼀般情况下,master device是SCK的上升沿发送,下降沿采集。

7:I2C和SPI总线数据传输都是MSB(最⾼有效位)在前,LSB在后(串⼝是LSB在前)。

8:I2C总线和SPI总线时钟都是由主设备产⽣,并且只在数据传输时发出时钟。

SPI详解

• spif: SPI interrupt flag, 当接收寄存器满并且发送寄 存器空时, 或者有写冲突发生时,中断标志为1, 如果允许发中断,则会像cpu发起中断请求。 • wcol: Write collision bit, 写冲突位,当发送正在进 行时往发送寄存器里写数据会造成该位置1,CPU要写 入的数据不会写入,CPU如果响应写冲突中断,应 该将wcol位清除。通过写该位将wcol位清除。(请 思考,可否CPU写入时,写入数据) • sprf: treg, SPI receive register满时为1,空时为0。 • spte: rreg, SPI tramsmit register空时为1,满时为0。 cpu可以根据该寄存器的状态得知SPI master的当前 状态,采取相应的读写或者修改状态位的操作。

• 在系统时钟的上升 沿,地址线、数据 线、写信号及片选 信号发生变化,则 发起新的传输。数 据传输的第一个时 钟周期称为SETUP 周期,即如图 所示 的(T2—>T3周期)。 在第二个时钟周期 的上升沿PENABLE 变为高电平,这个 周期称为ENABLE周 期。传输在这个周 期结束后完成, PENABLE信号随之 变低。

Bandwidth 8 8

paddr b00 b 01

8 8 8

b 10 b 10 b 11

spcr

spie spe reserved(0) spmstr cpol cpha spr[1] spr[0]

• • • • • • •

默认值8’h14 spie: SPI interrupt enable bit, 为1时才可以发起中断。 spe: SPI enable bit, 为1时才能工作。 spmstr: SPI master mode bit, 为1时为master 模式。 cpol: clock polarity bit,0,空闲时mater时钟为0;1,为1。 cpha: clock phase(一会我们看时序图) spr: SPI clock rate bit, spr[1:0] decides 串行发送时钟是主时钟的几倍 (周期)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字信号处理器与串行EEPROM 的接口设计王 新,王归新,张昌盛,康 勇(华中科技大学,湖北省武汉市430074)【摘 要】 介绍了串行电擦除可编程只读存储器93LC56A 的性能、接口时序及DSP 芯片T MS320F240串行外设接口(SPI )模块的主要特点。

针对这两种接口的时序配合问题,给出了从接口电路到软件设计的解决方案,并在程序实例的基础上进行了深入的分析。

关键词:数字信号处理器,串行外设接口,串行EEPROM ,接口中图分类号:TP334.7收稿日期:20032082110 引 言T MS320F240是第一个数字电机控制器的专用数字信号处理器(DSP ),它确立了单片数字电机控制器的标准,将高性能的DSP 内核和丰富的外设功能集成,广泛应用于厂房自动化系统、工业化电机驱动和功率转换以及供热、通风和空调系统中。

在这些控制系统中,对一些状态参数往往不仅要求能够做到在线修改,而且希望这些修改过的参数在断电时能够继续保持,以备下次上电时恢复系统的状态。

这时就需要在系统中配置能在线改写、并在失电时能够保持数据的EEPROM 。

串行EEPROM 不需要复杂的地址、数据和控制总线,仅由几根线就可以完成操作,节省了大量的硬件资源,这对一些I ΠO 口线比较紧张的系统来说尤其重要。

本文介绍Microchip 公司生产的93LC56A (串行电擦除可编程只读存贮器)与T MS320F240接口的性能特点、硬件接口时序和接口软件编程思路及其接口调试。

这在我们开发的以T MS320F240为内核的不间断电源(UPS )中得到了应用。

整个方案具有性能稳定、接口简洁、经济实用的优势。

1 TMS320F240与93LC56A 的接口1.1 93LC56A 的接口信号93LC56[1]是用C MOS 工艺制造的三线串行接口,容量为2kB ,能提供256×8位(93LC56A )或128×16位(93LC56B ),字写入时间小于10ms ,最大时钟额度2MH z ,可擦写106次。

通过写入擦Π写禁止指令,可有效避免误写入。

由于T MS320F240的串行外设接口(SPI )为8位,故选择93LC56A 。

93LC56A 共有7条指令,每个命令以数位“1”作为起始位,然后是2位操作码与6位地址,分别为读(RE AD )、擦Π写允许(EWE N )、写(WRITE )、全写(WRA L )、擦除(ERASE )、整片擦除(ERA L )和擦Π写禁止(EW DS )指令。

其指令格式如表1所示。

表1 93LC56A 指令格式指令S B操作码地址数据输入数据输出C LK周期ERASE 111X A7A6A5A4A3A2A1A0-(RDY ΠBSY )12ERAL 10010X X X X X X X -(RDY ΠBSY )12EWDS 10000X X X X X X X -HIGH 2Z 12EWE N 10011X X X X X X X -HIGH 2Z 12RE AD 110X A7A6A5A4A3A2A1A0-D72D020WRITE 101X A7A6A5A4A3A2A1A0D72D0(RDY ΠBSY )20WRAL 10001X XX X X X X D72D0(RDY ΠBSY )201.2 93LC56A 的接口时序图1为93LC56A 与外面接口时的数据同步时序。

图1 数据同步时序写指令先写入起始位、操作码、地址码,再写入D7~D0共8位数据,当D0位被时钟脉冲C LK 移入DI后,CS 必须在下一个时钟脉冲C LK 之前变低至少250ns 后再变高,以启动自定时编程周期,这时,DO 脚指示芯片的RE AD ΠBUSY 状态,当DO 脚为低电平,表示芯片处于忙状态,DO 脚为高电平,表明写指令结束。

图2为93LC56A 与外面接口时的写操作时序。

・36・第30卷第1期2004年1月 电子工程师 E LECTRONIC E NGI NEER V ol.30N o.1 Jan.2004图2 写(WRITE)时序 读指令使DO 脚上输出串行数据。

芯片从DI 脚接收有效数据后,对指令和地址进行译码,随后将地址译码器所选中的寄存器的内容送至8位串行移位寄存器,然后先在DO 脚输出一位逻辑“0”,接着依次输出D7~D0数据,结束后,DO 端变成高阻态,在下一个C LK 脉冲上升沿稳定。

图3为93LC56A 与外面接口时的读操作时序。

图3 读(READ)时序1.3 TMS320F240的SPIT MS320F240的SPI 是一个高速同步串行I ΠO 口,它允许1~8位串行比特流以特定的传输速率移进或移出芯片。

可通过设置相应的各个控制寄存器来实现对各管脚、各单元工作模式和工作过程的控制[1]。

图4为T MS320F240的SPI 时钟设计时序。

时钟极性位(SPICCR.6)和时钟相位位(SPICT L.3)控制引脚SPIC LK 上的4种不同的时钟设计。

时钟极性位选择时钟有效沿为上升沿还是下降沿,时钟相位位则选择时钟的1Π2周期延时。

图4 TMS320F240的SPI 时钟设计时序4种不同的时钟设计如下:a )无延时的上升沿:SPI 在SPIC LK 的上升沿发送数据,而在SPIC LK 的下降沿接收数据。

b )有延时的上升沿:SPI 在SPIC LK 的上升沿之前的半个周期发送数据,而在SPIC LK 的上升沿接收数据。

c )无延时的下降沿:SPI 在SPIC LK 的下降沿发送数据,并在SPIC LK 的上升沿接收数据。

d )有延时的下降沿:SPI 在SPIC LK 的下降沿之前的半个周期发送数据,而在SPIC LK 的下降沿接收数据。

通过设置时钟极性位及时钟相位位可以决定SPI 接收和发送的时序。

1.4 TMS320F240与93LC56A 的接口电路T MS320F240与93LC56A 接口电路如图5所示。

图5 TMS320F240与93LC46A 的接口电路由93LC56A 的各种操作时序可以看出,合理设计T MS320F240的SPI 的传输速率及接口时钟,并将T MS320F240的SPISTE 设置为通用I ΠO 口,提供符合93LC56A 要求的片选信号,则可以满足93LC56A 数据同步时序的要求。

2 模块的软件编程下面以图5所示的接口电路说明如何通过程序来对T MS320F240进行控制,使它的SPI 能够满足93LC56A 的时序要求及指令格式,从而完成各种指令的操作,实现模块的系统功能。

在系统程序的初始化部分应该对程序中用到的寄存器和临时变量作说明:.bss SPIWRDAT A ,1;写入或者读出的数据.bss SPIWRADDR ,1;数据对应的地址2.1 设置工作时钟及初始化SPI 模块设定C LKI N 为20MH z ,SY SC LK 为10MH z ,选择移位序列中字符为8位,接口时钟设计为有延时的上升沿,主网络传输速率为1Mbit Πs ,则SPIC LK 的周期为1ms ,占空比为50%,可见能够满足93LC56A 数据同步时序图中C LK 及DI 的要求。

设定SPISTE 为通用I ΠO 口,且输出低电平,配置SPIC LK 引脚包含并输出SPI 时钟,SPISI MO 为输出SPI数据,SPIS OMI 输入SPI 数据。

2.2 写操作子程序写数据SPIWRDAT A 到93LC56A 指定地址SPI 2・46・・计算机与自动化技术・ 电子工程师 2004年1月WRADDR中去。

93LC56A接收到数据位1时开始启动,对之前接收到0的数据位不动作。

把00001010B存入串行数据寄存器,SPI自动从高位到低位移位输出。

93LC56从收到第1个数据“1”时开始启动,它收到的有效数据1010B即为写指令。

由于接口时钟设计为有延时的上升沿,则SPI在SPIC LK的上升沿之前的半个周期发送1位数据, 93LC56A则在SPIC LK的上升沿接收这位数据,而且SP 在SPIC LK的下降沿接收93LC56A输出的1位数据,由于这时DO上没有数据输出,故DSP接收不到数据。

读SPI状态寄存器,看SPI完成标志位是否为1,可以判断出DSP是否已经把串行数据寄存器的8位数据发送完。

如果SPI完成标志位变成1,则说明SPI已经发送或者接收完了字符的最后位。

此时读串行数据寄存器,可将此标志位清零,SPI就开始新的传送和接收任务了。

先发送写入的地址SPIWRADDR,再发送需要写入的数据SPIWRDAT A。

在发送前将SPISTE置为高电平,发送完成后再将SPISTE置为低电平,并合理设置延时,以满足CS对高低电平的需要。

如果指令有效,则93LC56A将开始写操作,即将数据SPIWRDAT A写入到指定地址SPIWRADDR中。

重新设定SPIS OMI为通用I O口,且为输入引脚,则可以读取D0上的状态。

如果D0变高,说明93LC56A已经把数据写入到指定地址中去了。

恢复SPIS OMI的设置,将SPISTE置为低电平,写操作子程序结束。

2.3 读操作子程序T MS320F240从93LC56A的指定地址SPIWRADDR 中读取数据并存到SPIWRDAT A中去。

SPIRE AD: LDP #SPICCRΠ128 SP LK #01010010B,SPIPC1 ;置SPISTE为高 NOP SP LK #00001100B,SPI DAT ΠΠ把读指令存入串行数据寄存器SPIRE AD1: LACC SPI-STS AND #040h BC ND SPIRE AD1,E Q LAC L SPI BUF;发送完成,清SPI完成标志 LDP #4 LAC L SPIWRADDR LDP #SPICCRΠ128 S AC L SPI DAT ΠΠ把读数据地址SPIWRADDR存入串行数据寄存器SPIRE AD2: LACC SPI-STS AND #040h BC ND SPIRE AD2,E Q LAC L SPI BUF ;发送完成,清SPI完成标志 SP LK #10000111B,SPICCR SP LK #00000110B,SPICT L SP LK #00000111B,SPICCR SP LK #01010101B,SPI DAT ΠΠ配置接口时钟设计为无延时的上升沿,则DSP在SPI2C LK的上升沿经DI发送数据给93LC56A,93LC56A则在SPIC LK的上升沿经DO发送数据给DSP。

SPI发送的数据对93LC56A的工作无影响,仅仅用来提供SPI2C LK。

DSP在SPIC LK的下降沿接收93LC56A输出的1位数据SPIRE AD3: LACC SPI-STS AND #040h BC ND SPIRE AD3,E Q LAC L SPI BUF ;发送完成,清SPI完成标志 LDP #4 S AC L SPIWRDAT A ΠΠ已经发送完成,SPI已收到93LC56A发出的数据 LDP #SPICCRΠ128 SP LK #00010011B,SPIPC1 ;置SPISTE为低 NOP SP LK #10000111B,SPICCR SP LK #00001110B,SPICT L SP LK #00000111B,SPICCR ΠΠ恢复SPI配置:接口时钟设计为有延时的上升沿 RET2.4 各子程序的调用有了以上的子程序,就可构造实用的参数掉电保存程序。