最新同步复接器分接器的FPGA设计与实现

Turbo码Max-Log-MAP算法研究及其实现

Re s e a r c h a n d i m pl e me n t a t i o n o f t h e Ma x - Lo g - M AP a l g o r i t hm f o r Tu r b o c o de s

Ab s t r a c t : Th e L o g —ma p a n d Ma x —L o g — M AP lg a o r i t h m f o r Tu r b o c o d e s a r e a n a l y z e d i f r s d y . t h e n t h e Ma x — L o g —M AP a l g o r i t h m f o r Tu r b o c o d e s b a s e d o n CCS DS S t a n d a r d , i s s i mu l a t e d a n d v e i r i f e d b y Ma t l a b . F i n a l l y t h e Ma x —L o g —M AP i s i mp l e me n t e d o n t h e x c 4 v l x l O 0

FPGA o f Xi l i n x. Ke ywor d s : Tur bo; Log ~m a p; M a x —Lo g—M A P; CC S DS

1 引言

T u r b o码 ,又 称 并 行 级 联 卷 积 码 ( P C C C ) ,是在 1 9 9 3年 5

在T u r b o码编码 过程 中,信息序列经过一个交织器,形

成 一 个 新 序 列 ,两 个 序 列 分别 送 到 两 个 分 量 编 码 器 , 同时 原

始 的信息序列作为系统位输 出直接送至复接器。 ~般情况 下, 这两个编码器结构相同。为了能适应不 同的编码效率 ,信 息 序列需要经过删余矩阵,采用删余技术从这两个校验序列中 周期地删除一些校验位 ,生成 T u r b o编码序列 。 编码器 中交织器的使用是实现 T u r b o码近似随机编码的 关键 。交织器实际上是个~一映射 函数 ,作用是将输入信息 序列 中的比特位置进 行重置,以减小分量编码器输出校验 序 列 的相关性和提高码重。 删余矩 阵的作用是改变编码效 率,其元素取 自集合 { 0 ,

MPEG-2 TS到E2转换研究及其FPGA实现

使信号适配O对于 FG PA里面 的逻辑设计 , 理论

也跟解码板的逻辑 设计可逆 , 即实现 I B 码到 - 3 I D M 码的码型变换 , 84 8 b s M E 2' 码 和 . Mp到 PG I 4 S 流速率的调整。不过 由于 M E 2 码流是变速 PG 的, 所以直接用 848 bs . M p 来传输 同样可行 , 4 故码 速调整就不需要 , 但是 由于接收 信号没有携带时 钟信号 , 所以需要 从接收信号 中提取时钟 同步信 息, 从而恢复时钟 。总之 , 解码板的逻辑设计主要 有码型变换和时钟恢复构成。

V . 1 S m . 5 d l 5 u No 7

ME P G一2T S到 E 2转换研 究及 其 F G P A实现

,

●

邓 松 ,杨 必武 ,阮友 德

( 深圳职业技术学院工业中心 ,广 /深圳 , 105 j , - 5 85 )

【 摘要】通过深入研究I / ̄1 1— 及 1U TG73 S I 3 8 1 T — . 的基础上,设计出M F 2' 流到 E 非成帧格式 OF 8 0 P, I _ G一 S 2 数据流的转换方案,本文将对基于 的实现的原理和实现方法做一些介绍。 一 【 关健词】b E 2 S E ;-B ; f G一 ; 2 I 3 P T I - D 【 中圈分类号】' 911 【 r 4. N 文献标识码】B 【 文章编号】10 — r4(O6 1 09 — 3. 08 96 20)0 — 08 0 7

G 73 .0 规定 ,2的传输码率为恒定 848l .同 E .41 p , V的功能之一 , 同时 由于 M E P C一2' I S码流 码型 为 N Z码, E R 而 2格 式的码 流码型 为 I B - 3 I D 码 , N Z码 到 H B 故 R D 3码 的码 型 转 换 成 为 该 编 码 板的完成的功能之二。由此可见 , 编码板在逻辑 上要完成的工作就是码速调整和码型变换, 这部 分由 来完成。由于从 输 出 I B 码 - 3 I D 为两个单极性信号组成的差分 信号 , 考虑长 距离 传输的损耗 , 所以电路设计时 , 应加入差分驱动电 路 。同时 I B - 3为 双 极 性 码 , 此 需 要 加 入 变 压 I D 因 器将单极性差分信 号变换为双极性码 , 通过双绞 线或者同轴电缆传输。 对于 MP G I , 码 板 的 设计 , 实 就 E 2' t E S o 2解 其 是编码板设计的逆 过程 。 以针对编码板的变压 所 器输出, 解码板也应加入变压器来接收将双极性 信号转换成两路单极性信号。同时针对编码板的 差分驱动 , 在解码板上应有对应的差分接收芯片

OTS-E光端机说明书

OTS-E系列PDH光端机用户手册版本:V2.1(2004版)目录一、产品概述 (4)二、设备特点 (4)§2.1 独立式 (4)§2.2 机框插卡式 (4)三、设备说明 (5)§3.1 系统原理框图 (5)§3.2 系统描述 (5)§3.2.1 工作原理 (5)§3.3 隔爆壳和前、后面板标识及指示灯说明 (6)§3.4 外围接口 (10)四、设备安装与维护(以输入电源-48V为例) (11)§4.1 设备包装、外观检查 (11)§4.2 设备安装 (11)§4.2.1 各类机型安装方式 (11)§4.3 整机安装 (14)§4.4 安装注意事项 (15)§4.5 设备的维护 (15)§4.6 机房及接地要求 (15)§4.7 故障的判断 (15)五、技术规格 (16)§5.1 电部分 (16)§5.2 光部分 (17)§5.3 网管部分(选配,需单独购买) (17)§5.4 电源部分 (17)§5.5 环境要求 (18)§5.6 机械参数 (18)附录 (19)一、产品概述OTS系列光端机是对二次群光端机优化设计后的新一代产品,进一步完善了各项设计,使之成为稳定可靠、美观小巧、经济实用,具良好传输特性的新一代传输产品。

该设备作为一种性能优异的成熟技术产品,内部的软硬件均为模块化结构。

硬件部分采用了大规模FPGA电路──集编码、解码、信息插入、告警切换于一体,使电路变得简单,从而提高了整机的可靠性。

电接口部分采用大规模的ASIC电路,集数字抽样时钟、数字平滑锁相、编解码于一体,使得各项指标大大优于ITU-T各项建议。

二、设备特点§2.1 独立式OTS系列精巧型单板二次群光端机是通信技术和计算机技术有机结合的产物,适用于交换机远端传输和光纤环路等小容量点对点的应用场合,特别适合于通信容量小,可靠性要求高,辅助功能特别齐全的场合。

DTMB调制器FPGA设计文档

DTMB调制器FPGA设计文档一、总体框架图总体结构框图系统配置:帧格式:PN420,PN595,PN945载波数:单载波,多载波交织模式:短交织,长交织调制方式:QAM4NR,QAM4,QAM16,QAM32,QAM64LDPC编码率:LDPC04,LDPC06,LDPC08射频输出频率:950~2150MHz(外加射频电路)输出电平:-80~+2dBm(外加射频电路)二、各部分具体实现1.数据输入接口模块完成输入数据并-串转换逐位输出,送入下一级进行加扰。

每次请求BCHLen某 LDPCLen个752比特,其中BCHLen由编码率决定:4/6/8,LDPCLen由QAM阶数决定:1/2 /4/5/6,这样做以便映射是能取到刚好足够的信息比特。

中间有LDPCLen个校验比特数目的间隙,后面有由帧长决定的间隙。

2.加扰对前级过来的数据用扰码进行加扰。

输入与PN序列进行逐位模二加运算。

扰码在信号帧开始时复位到初始相位。

信号帧起始位置通过计数器循环计数来判断。

ValidOut信号与ValidIn信号同频, 与时钟Clk同频(108MHz)。

3.BCH编码对Scrambler模块的输出进行编码。

输入通过线性移位反馈寄存器计算编码值,前752个时钟将输入直接输出,后10个时钟输出移位寄存器中的编码值。

三种不同内码码率的FEC码的结构分别为:a)码率为0.4的FEC(7488,3008)码:先由4个BCH(762,752)码和LDPC(7493,3048)码级联构成,然后将LDPC(7493,3048)码前面的5个校验位删除。

b)码率为0.6的FEC(7488,4512)码:先由6个BCH(762,752)码和LDPC(7493,4572)码级联构成,然后将LDPC(7493,4572)码前面的5个校验位删除。

c)码率为0.8的FEC(7488,6016)码:先由8个BCH(762,752)码和LDPC(7493,6096)码级联构成,然后将LDPC(7493,6096)码前面的5个校验位删除。

EOC-700型继电保护光纤通信接口装置

EOC-700型继电保护光纤通信接⼝装置2EOC-700型继电保护光纤通信接⼝装置2.1装置概述EOC-700型继电保护光纤通信接⼝装置是⽤于各种线路保护中的光电转换设备,完成提供光纤接⼝的保护装置与数字通信设备(PCM、SDH微波/光纤等)的复接功能。

与数字通信设备复接的电接⼝特性符合CCITT制定的G.703接⼝协议标准,并提供2M电⼝和64K同向接⼝可选择。

EOC-700装置提供两路独⽴的光纤/电⼝通道,这两路通道由保护装置设定为单通道⼯作(另⼀停⽤)或⼀主⼀热备⼯作⽅式。

详细描述请参见《EOC-701继电保护光纤通信接⼝装置说明书》。

EOC-700装置可与深圳南瑞科技有限公司的PRS-753光纤分相纵差成套保护装置、PRS-701/702超⾼压线路成套保护装置等⾼压微机保护配合,传输三相电流和开关信号。

2.2装置特点1)数据的传输采⽤⾼效的同步通讯⽅式,采⽤先进、灵活的⼤规模可编程器件FPGA,提供了两路独⽴的全双⼯数据通道。

2)灵活的接⼝⽅式:2M电接⼝和64K同向数据接⼝⽅式可选,可以适应不同场合的应⽤。

3)装置内部采⽤适于光纤传输和E1传输的编解码⽅式,提⾼了数据传输的可靠性,抗⼲扰能⼒强。

4)采⽤全数字锁相环技术,提⾼了时钟的稳定性。

2.3技术参数1)光纤接⼝a)线路码速率:2MHzb)线路码型:CMIc)光接头:SC/PCd)光模块收发模式:模式—— 单模波长—— 1310nme)发送功率:≥-9dBmf)接收灵敏度:≤-40dBm2)电接⼝:电接⼝特性符合CCITT制定的G.703接⼝协议。

3)直流电源输⼊电压: 48V;允许偏差:±20%4)环境温度:正常⼯作温度:-5 ~ 40 ℃极限⼯作温度:-10 ~ 55 ℃贮存及运输:-25 ~ 70 ℃5)绝缘耐压及抗⼲扰性能:符合GB/T14598的规定。

2.4⼯作原理2.4.1装置原理及构成EOC-700装置的任务是为保护装置和数字通信设备提供⼀条透明的传输通道,即将保护装置发送的光信号转换为电信号通过数字通信设备传输到线路对端,同时将从数字通信设备接收来的电信号转换成光信号后发送给保护装置,其原理框图如图2-4-1所⽰。

adv202 设计

Project: the Compression and Decompression of Vid eo Data2009-09-14 10:52:41| 分类:学术论文|字号大中小订阅课题要求:此课题研发的是某航空遥感系统中视频数据压缩与解压的任务,以满足在有限的无限信道中传输海量的视频数据。

设计指标要求视频数据传输带宽为1.92Mbps,即可以同时以1.92Mbps传输一路视频信号或者分别以0.48Mbps带宽传输四路视频信号;另外附加1.92Mbps的任务数据信道,即总共拥有的信道是3.84Mbps,任务数据通过FPGA复接到视频数据中通过数传通道一起传回地面的控制器。

系统实现:机载摄像机提供的模拟视频经解码芯片SAA7115转换为数字视频,数字视频信号数据量非常大,按照CCIR656图像标准,并以4:2:2(Y:Cb:Cr,即每个像素用两个bytes表示)编码类型为例,可得视频数据比特流为:720×576×2byte×8bit×25帧/S=165.89 Mbps,显然此数据流无论是对存储还是对传输都是不实际的,因此必须对原始解码的数字视频进行压缩,以满足带宽有限的无线信道的传输,比如此系统中,就要求在0.48Mbps的无线信道中进行传输。

此系统中采用的视频压缩标准是JPEG2000压缩标准,其采用的是把运动的视频序列作为连续的静止图像来处理的方式,并且是独立压缩每一帧(即没有采用帧间相关性来压缩,而其他压缩标准都利用了帧间相关性的差异来提高编码效率),所以传输错误不会影响到其它帧,以使端到端的等待时间低,即使得实时性高。

另外,JPEG2000采用的是离散小波变换(DWT),不同其他压缩标准(H.261,H.263,H.263+,H.263++,H.264,MPEG 系列等)的DCT(离散余弦变换),也就是具有对信号进行多分辨率分析和反映信号局部特征的特点。

基于CPLD的I2S语音总线接口

基于CPLD的I2S语音总线接口摘要:本文介绍了利用Xilinx公司的XC9500系列CPLD器件,以I2S接口方式对四路输入语音信号进行处理与传输,并用VHDL进行建模,通过ISE软件仿真得出了比较理想的结果,并在工程应用中使用良好。

关键词:CPLD;XC9500;数据传输;多路复用1 引言CPLD器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

XC9500系列CPLD 器件tPD最快达3.5ns,系统时钟可达200MHz。

XC9500系列器件采用第二代“支持ISP”的引脚锁定结构,它拥有一个54比特输入函数块,是用户可以在进行多种改变的同时保持输出引脚固定。

这个特点使设计更具有灵活性,如时钟完全受控,用户既可以对每个宏单元作输出使能反转,也可以对个别的乘积项时钟作使能反转。

在视频监控光端机设备设计中,采用XC95144XL芯片实现了视频采集和处理,语音采集和处理,RS485、RS232通信、与光通信模块一起实现了远程监控系统,本文仅就语音采集和处理、传输的编程、仿真、实现作详细地阐述。

该系统在实际工程中性能稳定可靠,具有一定的参考价值。

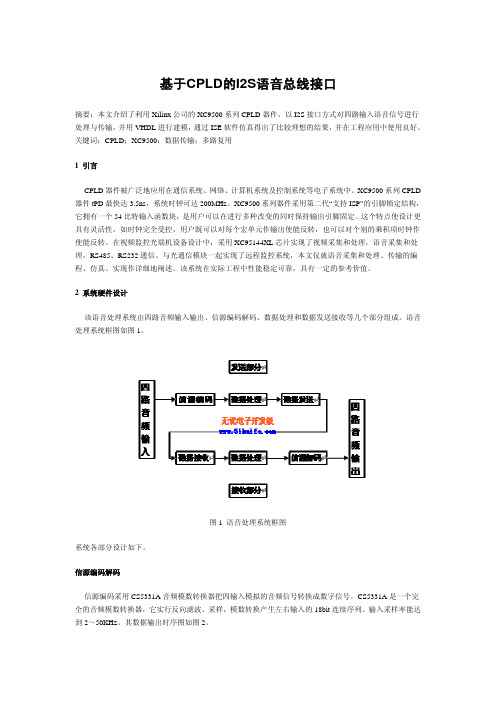

2 系统硬件设计该语音处理系统由四路音频输入输出、信源编码解码、数据处理和数据发送接收等几个部分组成。

语音处理系统框图如图1。

图1 语音处理系统框图系统各部分设计如下。

信源编码解码信源编码采用CS5331A音频模数转换器把四输入模拟的音频信号转换成数字信号。

CS5331A是一个完全的音频模数转换器,它实行反向滤波、采样,模数转换产生左右输入的18bit连续序列。

输入采样率能达到2~50KHz。

其数据输出时序图如图2。

图2 数据输出时序图信源解码采用CS4334芯片音频数模转换器把四输入数字信号转换成模拟信号的音频信号。

CS4334的特性主要有:完善的立体声D/A转换系统,插入补偿,D/A转换,输出模拟滤波,24位转换,96dB动态范围。

其时序如图3。

【电子技术应用】_设计过程_期刊发文热词逐年推荐_20140726

数据支持 数据加密 数字复接器 数字分接器 数字信号处理 攻击模型 改进粒子群优化算法 控制系统 拓扑结构 拉丝机 抗辐照 总线 张力控制 异步fifo 开槽波导 应用 差分故障攻击 巡线算法 嵌入式计算机 嵌入式技术 小波变换 密钥 实时操作系统 实时 多重 多参数 多任务实时操作系统 图像编码 固件程序 嗅探器 同步流密码机 同步 可靠性预计 可靠性 可重构系统 可视化 可抛式 变异 医疗仪器 包捕获 力学分析 切普扩频 传感器 以太网 代理协作 人机界面 产品生产 交叉编译 串口服务器 中央空调系统 下位机系统 三线制同步串行通信 vhdl usb接口

科研热词 fpga 数据采集 usb can 高速铁路信号 验证平台 验证 颤振 隔离 门控时钟 镜像 采集和处理 通道 通讯 通信 软硬件协同验证 超声波 资源平台 贝尔彩色 调试 误码测试仪 设计过程 设计环境 设备 讲座 训练系统 认证 解调 视景仿真 自动白平衡 联合调试 终端节点 终端系统 磁盘阵列 磁盘接口控制器 电池管理系统 电子工业 电子对抗 电子元器件 生物实验 片上系统 激光扫描 浮点dsp 测试模式 测试分析 流水线设计 汽车测量 染色工艺 机电 机动车检测 无缝接口 数字自动监测系统

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106

科研热词 linux fpga 齿轮箱 超宽带 振动噪声 反馈电路 反激式开关电源 voip uc3844 sopc pxi总线 labview ehpi 音频放大器 遥测数据 遥控 超薄系统 调制解调器 说话人识别 误码率 语音报数 设计工具 视频监控 表格 血管硬度 血压 脉冲 美国国家半导体公司 示波法 示波器 生物发酵 热测试 模糊控制 标签 时间积分相关器 无人机 斜波比较 整数变换 数据库 数据包 数字信号处理 开发 嵌入式系统 实时压缩 字段 套用 多路 外关键字 在线 反量化 单片机 动态时序仿真

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

同步复接器分接器的FPGA设计与实现 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 毕业论文 同步复接器/分接器的FPGA设计与实现 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 一. 复接器的设计 本设计采用了将复接器通过软件来实现,尽可能用软件来实现更多的硬件电路[18~19]。在FPGA设计中采用了分层设计,顶层为整个系统的原理框图(见图1),框图

中包含了构成同步数字复接器的主要模块,然后按各模块的功能分别进行设计[20]。

图1 四路同步复接器的VHDL建模框图 图1的四路同步复接器框图由分频器、内码控制器、时序产生器、内码产生器、输出电路等模块组成[21~22]。分频器模块的作用是用来产生一个256KHZ的时钟信号,内码控制器模块的作用是通过三个地址控制端来控制内码发生器的码字依次输出,时序发生器模块的作用是产生四路时序来控制四路信号的输出,内码产生器模块的作用是将八路并行输入码通过串行输出,输出电路模块的作用是用一个三态门来控制四路信号分时输出,从而实现复接功能。复接器的VHDL设计根据所划分的几大模块分别用VHDL语言去描述,最后用元件调用语句和例化语句将它们连接起来。

时钟 分频器 内码控制器 内码产生器 内码产生器 内码产生器 内码产生器

输出电路

时序发生器 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 1. 分频器

分频器实际是一个计数器,在本设计中,其作用是将由晶体震荡电路产生的4096KHZ的方波信号进行分频,其16分频(即256KHZ时钟)输出端作为内码控制器的控制输入端。其建模流程图如图2所示。

图2 16分频计数器流程图 分频器的VHDL描述程序如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity count16 is port (clk: in std_logic; d,c,b,a: out std_logic); end count16; architecture rtl of count16 is signal count_4:std_logic_vector(3 downto 0); begin process(clk) begin

时钟CLK输入 开始计数

=15 计数器计数 计数器清零 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 if(clk'event and clk='1') then if(count_4="1111") then count_4<="0000"; else count_4<=count_4+1; end if; end if; end process; d<=count_4(0); c<=count_4(1); b<=count_4(2); a<=count_4(3); end rtl;

上述程序在Max+plus II时序仿真波形如图3所示。

图3 分频器的时序仿真波形 图3中,a表示16分频输出,b表示8分频输出,c表示4分频输出,d表示2分频输出。由图中可以看出,实际仿真波形图与理论预期一致。 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 2. 内码控制器

内码控制器,实际也是一个分频器,一个输出端口输出三位并行信号作为内码产生器的地址控制端,另一输出端作为时序产生器的控制端。内码控制器对内码产生器的控制功能表如表3.1所示。 表3.1 内码控制器对内码产生器的控制功能表 内码控制器的3路输出信号(A2A1A0) 内码产生器输出信号位(Y0-Y7中选1) A2 A1 A0 Y 0 0 0 Y0 0 0 1 Y1 0 1 0 Y2 0 1 1 Y3 1 0 0 Y4 1 0 1 Y5 1 1 0 Y6 1 1 1 Y7

表3.1中的A2、A1、A0分别表示内码控制器内的二进制分频器的8、4、2分频信号。内码产生器应循环并依次输出从“000”、“001”、一直到“111”。这样,内码发生器每个时钟节拍,输出一位码,通过输出电路送到合路信道上,最终形成一路串行码流。精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 3. 时序产生器 时序产生器可产生脉宽为8个时钟周期的四路时序信号。具体实现是:将内码控制器的二分频端通过一个32分频器,其16分频和32分频输出端作为2/4译码器的控制端,2/4译码器的四个输出端,在经过反相器后,便得出本设计所要求的四路时序。译码器的建模流程图如图4所示。

图4 译码器的VHDL建模流程图 译码器的VHDL描述程序如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity yimaqi is port (f2,f1: in std_logic; y3,y2,y1,y0 : out std_logic ); end ; architecture rtl of yimaqi is signal indata:std_logic_vector(1 downto 0); signal y:std_logic_vector(3 downto 0); begin

分频器的两位输出F2&F1

F2&F1=00 F2&F1=01 F2&F1=10 F2&F1=11 输出=1110 输出=1101 输出=1011 输出=0111 精品好文档,推荐学习交流

仅供学习与交流,如有侵权请联系网站删除 谢谢3 indata<=f2&f1; process(indata) begin case indata is when"00"=>y<="1110"; when"01"=>y<="1101"; when"10"=>y<="1011"; when"11"=>y<="0111"; when others=>y<="0000"; end case; end process; y3<=y(3); y2<=y(2); y1<=y(1); y0<=y(0); end architecture rtl; 其时序仿真波形如图5所示。

图5 2/4译码器的时序仿真波形图 图5中,f2表示分频器的32分频输出端,f1表示16分频输出端,y0为第1路译码输出,y1为第二路译码输出,y2为第3路译码输出,y3为第4路译码输出。 时序发生器的仿真波形及相位关系图如图6所示。 精品好文档,推荐学习交流 仅供学习与交流,如有侵权请联系网站删除 谢谢3 图6 时序发生器的仿真波形及相位关系图 图6为译码器输出经过一个反向器处理后得出的仿真结果,图中S0、S1、S2、S3分别为四路的时序输出,由图中可以看出四路时序刚好组成一个完整的时序,仿真结果与理论预期一致。

4. 内码产生器 四个内码产生器可生产四路独立的八位数码,并在内码控制器的控制下输出相应的数码,例如:C、B、A为三个地址控制端,Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0为八位码的输出,则二者的关系表3.2所示: 表2 3/8控制关系图 C B A 输出

0 0 0 Y0 0 0 1 Y1 0 1 0 Y2 0 1 1 Y3 1 0 0 Y4 1 0 1 Y5 1 1 0 Y6 1 1 1 Y7

一个内码产生器的VHDL描述程序如下: library ieee; use ieee.std_logic_1164.all; 精品好文档,推荐学习交流 仅供学习与交流,如有侵权请联系网站删除 谢谢3 entity neimacs0 is port (in0_8,in0_7,in0_6,in0_5,in0_4,in0_3,in0_2,in0_1,k3,k2,k1,sx0: in std_logic; out0: out std_logic); end entity neimacs0 ; architecture nm0 of neimacs0 is component mux8_0 port (d7,d6,d5,d4,d3,d2,d1,d0,d,c,b: in std_logic; y : out std_logic); end component; component tri_gate0 port(din0,en: in std_logic; dout0:out std_logic); end component; signal l0: std_logic; begin u1:mux8_0 port map (d7=>in0_8,d6=>in0_7,d5=>in0_6,d4=>in0_5,d3=>in0_4,d2=>in0_3,d1=>in0_2,d0=>in0_1,d=>k3,b=>k2,c=>k1,y=>l0); u2:tri_gate0 port map(din0=>l0,en=>sx0,dout0=>out0); end architecture nm0 ; library ieee; use ieee.std_logic_1164.all; entity mux8_0 is port(d7,d6,d5,d4,d3,d2,d1,d0:in std_logic; d,c,b:in std_logic; y :out std_logic ); end mux8_0;