芯片引脚图及引脚描述

2812引脚图及原理

图1 主要元件位置示意图开发板采用一个TPS767D301芯片为整个系统供电,采用一个LED作为上电指示,添加了手动复位功能,将2812的全部引脚引出,开发板主要元件及其位置如图1所示。

标号功能描述P1~P4 DSP引脚引出P5 XMP/MCnP6 JTAGP7 电源输入表1 开发板插接件P1~P4将2812的全部有用引脚引出,以便用于扩展。

每个插接件的第一脚用方形焊盘表示。

下面图表分别描述了P1~P4的引脚排列及每个引脚的功能。

图2 P1的引脚排列引脚功能引脚功能1ADCINA72ADCINA63ADCINA54ADCINA4 5ADCINA36ADCINA2 7ADCINA18ADCINA0 9ADCINB110ADCINA0 11ADCINB312ADCINB2 13ADCINB514ADCINB4 15ADCINB716ADCINB6 17 3.3V_IO18GND 19MDRA20XA0 21MDXA22XD0 23MCLKRA24XD1 25XD226MFSXA 27MFSRA28MCLKXA 29 3.3V_IO30XD3 31GND32XD4 33SPICLKA34SPISTEA 35XD536XD6 37SPISIMOA38SPISOMI 39XRDn40XA1 41XZCS0AND1n42PWM7 43 3.3V_IO44GND表2 P1引脚功能描述图3 P2引脚排列引脚功能引脚功能1GND2 3.3V_IO 3XHOLDAn4T4CTRIP 5XWE6XA37CANTA8XZCS2n 9CANRA10SCITB 11SCIRB12PWM1 13PWM214PWM3 15PWM416XD12 17XD1318PWM519PWM620T1PWM 21XA422T2PWM 23CAP124CAP225XA526CAP327T1CTRIP28XA629GND30 3.3V_IO 31T2CTRIP32TDIRA33TCLKINA34XA735XCLKOUT36XA837C1TRIP38C2TRIP39C3TRIP40XA9表3 P2引脚功能描述图3 P3的引脚排列引脚功能引脚功能1 3.3V_IO2GND3XREADY4RESETn5XHOLDn6XA187SCIRA8XA179SCITA10XA1611XINT212XNMI/XINT13 13XINT114XA1515XD1516 3.3V_IO 17XA1418XA1319XPLLDISn20XD1421XA1222XZCS6AND7n 23XA1124XA10表4 P3引脚功能描述图5 P4引脚排列引脚功能引脚功能1XA22T3CTRIP3XD114GND5TCLKINB6XD107XD98TDIRB9XD810GND11C6TRIP12 3.3V_IO13C4TRIP14C5TRIP15CAP516CAP617T4PWM18CAP419T3PWM20XD721PWM1222XRW23PWM1024PWM1125PWM826PWM9表5 P4引脚功能描述P5为DSP的XMP/MCn选择跳线,P5不短接时,XMP/MCn引脚被下拉到GND,DSP 工作在微控制器模式,当P5被短接时DSP工作在微处理器模式。

芯片引脚说明

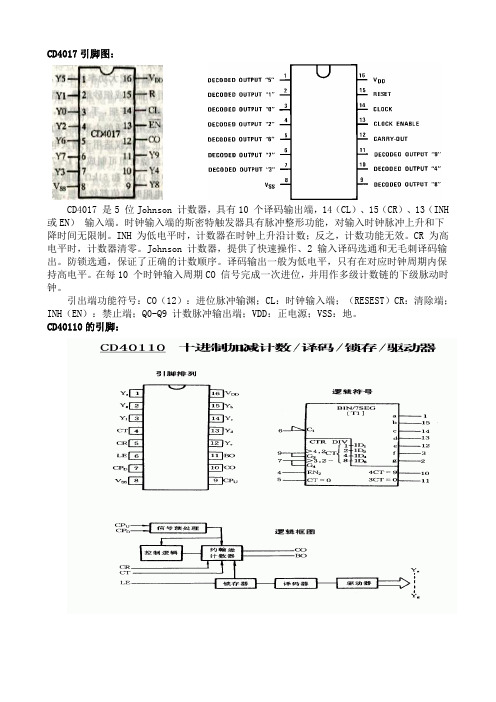

CD4017引脚图:CD4017 是5 位Johnson 计数器,具有10 个译码输出端,14(CL)、15(CR)、13(INH 或EN)输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。

引出端功能符号:CO(12):进位脉冲输渊;CL:时钟输入端;(RESEST)CR:清除端;INH(EN):禁止端;Q0-Q9 计数脉冲输出端;VDD:正电源;VSS:地。

CD40110的引脚:Ya~Yg:七段码,高电平有效;CPD(CP-):第七脚,减一、脉冲上升沿有效;CPU(CP+):第九脚,加一、脉冲上升沿有效;LE:第六脚,高电平有效,锁存数据;CT(TE):第四脚,高电平有效,禁止计数;CR(R):第五脚,高电平有效,清除计数显示。

数字式频率计LM317:输出电压连续可调的集成稳压电源,输出电压在1.25-37V之间连续可调,输出最大电流可达1.5A。

工作原理:电路原理图见图1。

LM317输出电流为1.5A,输出电压可在1.25-37V之间连续调节,其输出电压由两只外接电阻R1、RP1决定,输出端和调整端之间的电压差为1.25V,这个电压将产生几毫安的电流,经R1、RP1到地,在RP1上分得的电压加到调整端,通过改变RP1就能改变输出电压。

注意,为了得到稳定的输出电压,流经R1的电流小于3.5mA。

LM317在不加散热器时最大功耗为2W,加上200×200×4mm3散热板时其最大功耗可达15W。

VD1为保护二极管,防止稳压器输出端短路而损坏IC,VD2用于防止输入短路而损坏集成电路。

74LS系列主要芯片引脚及参数

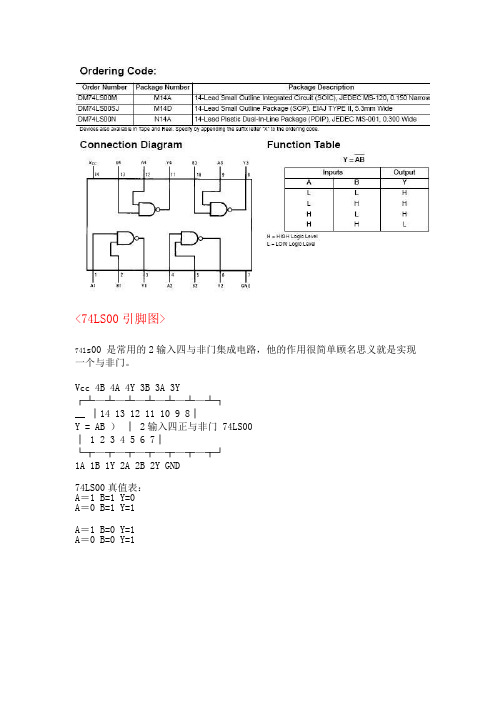

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

C51单片机引脚图及引脚功能介绍

80C51单片机引脚图及引脚功能介绍首先我们来介绍一下单片机的引脚图及引脚功能(如下图所示),引脚的具体功能将在下面详细介绍单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

⒈ 电源:⑴ VCC - 芯片电源,接+5V;⑵ VSS - 接地端;⒉ 时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

⒊ 控制线:控制线共有4根,⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲① ALE功能:用来锁存P0口送出的低8位地址② PROG功能:片内有EPROM的芯片,在EPROM 编程期间,此引脚输入编程脉冲。

⑵ PSEN:外ROM读选通信号。

⑶ RST/VPD:复位/备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD功能:在Vcc掉电情况下,接备用电源。

⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。

① EA功能:内外ROM选择端。

② Vp p功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

⒋ I/O线80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。

P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

拿到一块单片机,想要使用它,首先必须要知道怎样去连线,我们用的一块89C51的芯片为例,我们就看一下如何给它连线。

1、电源:这当然是必不可少的了。

单片机使用的是5V电源,其中正极接40管脚,负极(地)接20管脚。

2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。

只要买来晶体震荡器,电容,连上就能了,按图1接上即可。

3、复位管脚:按图1中画法连好,至于复位是何含义及为何需要复要复位,在单片机功能中介绍。

4、 EA管脚:EA管脚接到正电源端。

至此,一个单片机就接好,通上电,单片机就开始工作了。

我们的第一个任务是要用单片机点亮一只发光二极管LED,显然,这个LED必须要和单片机的某个管脚相连,不然单片机就没法控制它了,那么和哪个管脚相连呢单片机上除了刚才用掉的5个管脚,还有35个,我们将这个LED和1脚相连。

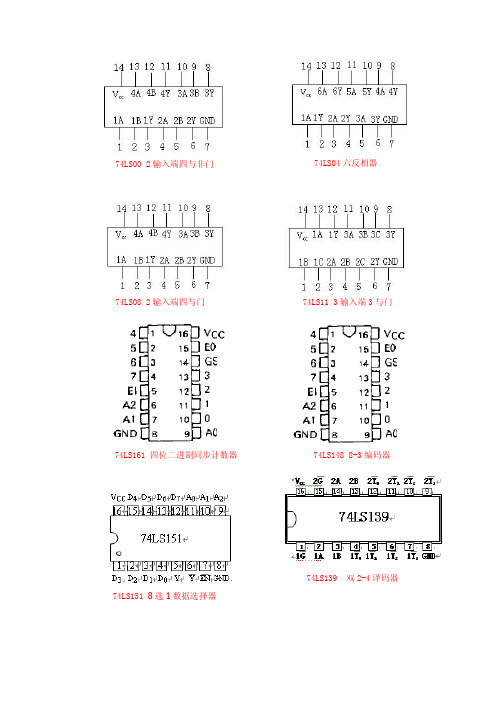

74系列芯片引脚图

类别 电路简称 四位比较器 74LS85

A3 B3

数据输入 A2 B2 A1 B1

真值表 A0 B0

级联输入

输出

A>B A<B A=B A>B A<B A=B

A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

GND 8

7744LLSS17124

16 Vcc 15 1CLR 14 2CLR 13 2CK 12 2K 11 2J 10 2PR 9 2Q

(a) JK 触发器 74112 引脚图

Y0 1

Y1 2

Y2 3 Y3 4 Y4 5 Y5 6 Y6 7 GND 8

7474LLSS7442

16 Vcc

15 A0 14 A1

13 A2 12 A3 11 Y9 10 Y8 9 Y7

图 3.2 74LS42 引脚图

74LS04

B1

C2

LT 3 BI/RBO 4

RBI 5 D6 A7

GND 8

747L4LSS7448

16 Vcc 15 f 14 g

13 a 12 b 11 c 10 d 9e

图 3.3 74LS48 引脚图

常用 74 系列 TTL 集成电路

真值表

时钟 CP J K

X

XX

X

XX

↓

00

↓

10

↓

01

↓

11

输出 清零(Q=0) 置 1(Q=1) 保持(Q=Qn)

Q=1 Q=0 翻转(Q=/Q)

电路引脚图

类别

电路简 称

常用芯片引脚图

附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )AGND :A/D 转换器参考地引脚12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

51单片机常用芯片引脚图

常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )AGND :A/D 转换器参考地引脚12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

INTEL2114芯片引脚图及逻辑符号

INTEL2114芯片引脚图及逻辑符号作者:本站来源:本站原创发布时间:2008-4-1 17:34:30 [收藏] [评论]

图2.4 INTEL 2114芯片引脚及逻辑符号

常用的静态RAM芯片有2114、2142、6116、6264等。

下面仅举几例。

Intel 2114是一个容量为1K×4位的静态RAM芯片,其内部结构如图2.3所示,芯片的引脚图和逻辑符号见图2.4(a)和(b)。

图中,A0~A9为10根地址线,可寻址=1024(1K)个存储单元。

I/O1~I/O4为4根双向数据线。

为写允许控制信号线,=0时为写入;=1时为读出。

为芯片片选信号,=0时,该芯片被选中。

由于2114的容量为1024×4位,故有4096个基本存储电路,排成64×64的矩阵。

用A3-A8六根地址线作为行译码,产生64根行选择线,用A0~A2与A9 四根地址线作为列译码,产生16根列选择线,而每根列选择线控制一组4位同时进行读或写操作。

存储器内部有4路I/O电路以及4路输入/输出三态

门电路,并由4根双向数据线I/O1~I/O4引与外部数据总线相连。

当=0与=0时,经门1输

出线的高电平将输入数据控制线上的4个三态门打开,使数据写入;当=0与=1时,经门2输出的高电平将输出数据控制线上的4个三态门打开,使数据读出.

图2.3 INTEL 2114内部结构。

笔记本维修常用芯片引脚说明

先有LDO5,给VCC供电(根据典型应用图判断) VCC有电后,再产生REF(根据内部框图判断) REF稳定后,再产生LDO3(根据引脚定义判断)

先有VREG5,再给V5FILT供电(根据典型应用图 判断) V5FILT正常后,再产生VREF2(根据内部框图判 断)

1、大于2V打开线 性供电

常用待机

常用待机芯片

PWM开启 引脚解释

1脚 ENTRIP1 2脚 ENTRIP2

通道1和通道2的开启和过流设定脚 1、直接接地,关闭PWM 2、通过电阻到地,作为电流极限设定

高电平开启(大于2.5V),低电平关闭 14脚EN1 (小于0.8V),当EN1连接REF时,PWM1会 27脚EN2 在PWM2稳定后延时开启,当EN2连接到REF

6脚VIN

4脚EN_LDO

高电平(大于1.6V)开启REF和LDO 低电平(小于1V)关闭REF和LDO

MAX8734 MAX8732 MAX8733 MAX1999

20脚V+

6脚SHDN#

高电平(大于1.6V)开启芯片 低电平(小于1V)关闭芯片

TPS51120

22脚VIN

9脚EN5 10脚EN3

时,PWM2会在PWM1稳定后延时开启

3脚ON3 4脚ON5

高电平开启(大于2.4V),低电平关闭 (低于0.8V),把ON3接REF,3.3V的PWM 会在5V的PWM稳定后延时启动

12脚EN2 29脚EN1

高电平(大于2.7V)直接开启 大于0.9V时会延时开启 低电平(小于0.5V)关闭

18脚ENC

74系列芯片引脚图资料大全

74系列芯片引脚图资料大全反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,是于1993年推出的PC局部总线标准。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

555芯片引脚图及引脚描述

555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。

1脚为地。

2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。

当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平;

2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。

6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。

3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。

4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。

5脚是控制端。

7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。

555集成电路管脚,工作原理,特点及典型应用电路介绍.

1 555集成电路的框图及工作原理

555集成电路开始是作定时器应用的,所以叫做555定时器或555时基

电路。

但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。

此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。

由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。

2. 555芯片管脚介绍

555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。

其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。

图2 555集成电路封装图

我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS端悬空。

另外还有复位端MR,控制电压端Vc,电源端VDD和

地端GND。

这个特殊的触发器有两个特点:

(1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s即触发端(TR)则要求低电乎;

(2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是高电平1,<1/3VDD是低电平0。

如果在控制端(Vc)上控制电压Vc时,这时上触发电平就变成Vc值,下触发电平就变成1/2Vc值,可见改变控制端的控制电压值就可以改变上下触发电平值。

它的功能表见图3(B)所示。

6. 555振荡器电路(无稳电路)

由555定时器构成的多谐振荡器如图9(a)所示,其工作波形见图9(b)。

接通电源后,电源VDD通过R1和R2对电容C充电,当Uc<1/3VDD时,振荡器输出Vo=1,放电管截止。

当Uc充电到≥2/3VDD后,振荡器输出Vo 翻转成0,此时放电管导通,使放电端(DIS)接地,电容C通过R2对地放电,使Uc下降。

当Uc下降到≤1/3VDD后,振荡器输出Vo又翻转成1,此时放电管又截止,使放电端(DIS)不接地,电源VDD通过R1和R2又对电容C充电,又使Uc从1/3VDD上升到2/3VDD,触发器又发生翻转,如此周而复始,从而在输出端Vo得到连续变化的振荡脉冲波形。

脉冲宽度TL≈0.7R2C,由电容C放电时间决定;TH=0.7(R1+R2)C,由电容C充电时间决定,脉冲周期T≈TH+TL。